Analog Devices AD7853CB, AD7853LBR, AD7853LBN, AD7853LAR, AD7853LAN Datasheet

...

a |

3 V to 5 V Single Supply, 200 kSPS |

|

12-Bit Sampling ADCs |

||

|

|

|

|

|

AD7853/AD7853L* |

|

|

|

FEATURES

Specified for VDD of 3 V to 5.5 V Read-Only Operation

AD7853–200 kSPS; AD7853L–100 kSPS

System and Self-Calibration with Autocalibration on Power-Up

Low Power:

AD7853: 12 mW (VDD = 3 V)

AD7853L: 4.5 mW (VDD = 3 V)

Automatic Power Down After Conversion (25 mW)

Flexible Serial Interface: 8051/SPI™/QSPI™/mP Compatible

24-Lead DIP, SOIC and SSOP Packages

APPLICATIONS

Battery-Powered Systems (Personal Digital Assistants,

Medical Instruments, Mobile Communications)

Pen Computers

Instrumentation and Control Systems

High Speed Modems

GENERAL DESCRIPTION

The AD7853/AD7853L are high speed, low power, 12-bit ADCs that operate from a single 3 V or 5 V power supply, the AD7853 being optimized for speed and the AD7853L for low power. The ADC powers up with a set of default conditions at which time it can be operated as a read-only ADC. The ADC contains self-calibration and system-calibration options to ensure accurate operation over time and temperature and have a number of power-down options for low power applications. The part powers up with a set of default conditions and can operate as a read only ADC.

The AD7853 is capable of 200 kHz throughput rate while the AD7853L is capable of 100 kHz throughput rate. The input track-and-hold acquires a signal in 500 ns and features a pseudodifferential sampling scheme. The AD7853/AD7853L voltage range is 0 to VREF with both straight binary and twos complement output coding. Input signal range is to the supply, and the part is capable of converting full power signals to 100 kHz.

CMOS construction ensures low power dissipation of typically 4.5 mW for normal operation and 1.15 mW in power-down mode, with a throughput rate of 10 kSPS (VDD = 3 V). The part is available in 24-lead, 0.3 inch wide dual-in-line package (DIP), 24-lead small outline (SOIC) and 24-lead small shrink outline (SSOP) packages.

*Patent pending.

SPI and QSPI are trademarks of Motorola, Incorporated.

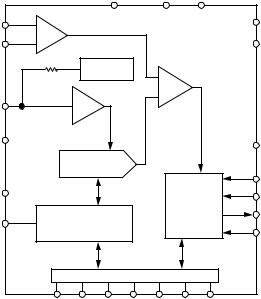

FUNCTIONAL BLOCK DIAGRAM

|

AVDD |

AGND |

AGND |

|

AIN(+) |

|

AD7853/AD7853L |

DVDD |

|

|

T/H |

|

||

AIN(–) |

|

|

DGND |

|

|

|

|

||

|

2.5V |

|

|

|

|

REFERENCE |

|

|

|

|

|

COMP |

|

|

REFIN/ |

BUF |

|

|

|

REFOUT |

|

|

|

|

CREF1 |

|

|

|

AMODE |

|

CHARGE |

|

|

|

|

REDISTRIBUTION |

|

|

|

|

DAC |

|

|

CLKIN |

|

|

|

|

|

CREF2 |

|

SAR + ADC |

CONVST |

|

|

|

CONTROL |

|

|

|

CALIBRATION |

|

|

BUSY |

CAL |

MEMORY |

|

|

|

|

AND CONTROLLER |

|

|

SLEEP |

|

SERIAL INTERFACE / CONTROL REGISTER |

|

||

SM1 SM2 SYNC DIN DOUT SCLK POLARITY

PRODUCT HIGHLIGHTS

1.Specified for 3 V and 5 V supplies.

2.Automatic calibration on power-up.

3.Flexible power management options including automatic power-down after conversion.

4.Operates with reference voltages from 1.2 V to VDD.

5.Analog input ranges from 0 V to VDD.

6.Selfand system calibration.

7.Versatile serial I/O port (SPI/QSPI/8051/ P).

8.Lower power version AD7853L.

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 1998 |

AD7853/AD7853L–SPECIFICATIONS1, 2 (AVDD = DVDD = +3.0 V to +5.5 V, REFIN/REFOUT = 2.5 V External Reference, fCLKIN = 4 MHz (1.8 MHz B Grade (08C to +708C), 1 MHz A and B Grades (–408C to +858C) for L Version); fSAMPLE = 200 kHz

(AD7853) 100 kHz (AD7853L); SLEEP = Logic High; TA = TMIN to TMAX, unless otherwise noted.) Specifications in () apply to the AD7853L.

Parameter |

A Version1 |

B Version1 |

Units |

Test Conditions/Comments |

DYNAMIC PERFORMANCE |

|

|

|

|

Signal to Noise + Distortion Ratio3 |

70 |

71 |

dB min |

Typically SNR Is 72 dB |

(SNR) |

|

|

|

VIN = 10 kHz Sine Wave, fSAMPLE = 200 kHz (100 kHz) |

Total Harmonic Distortion (THD) |

–78 |

–78 |

dB max |

VIN = 10 kHz Sine Wave, fSAMPLE = 200 kHz (100 kHz) |

Peak Harmonic or Spurious Noise |

–78 |

–78 |

dB max |

VIN = 10 kHz Sine Wave, fSAMPLE = 200 kHz (100 kHz) |

Intermodulation Distortion (IMD) |

|

|

|

|

Second Order Terms |

–78 |

–80 |

dB typ |

fa = 9.983 kHz, fb = 10.05 kHz, fSAMPLE = 200 kHz (100 kHz) |

Third Order Terms |

–78 |

–80 |

dB typ |

fa = 9.983 kHz, fb = 10.05 kHz, fSAMPLE = 200 kHz (100 kHz) |

DC ACCURACY |

|

|

|

|

Resolution |

12 |

12 |

Bits |

|

Integral Nonlinearity |

±1 |

±1 |

LSB max |

2.5 V External Reference VDD = 3 V, VDD = 5 V (B Grade Only) |

|

±1 |

±0.5 |

LSB max |

5 V External Reference VDD = 5 V |

|

(±1) |

(±1) |

LSB max |

(L Version, 5 V External Reference, VDD = 5 V) |

|

|

LSB max |

(L Version) |

|

Differential Nonlinearity |

±1 |

±1 |

LSB max |

Guaranteed No Missed Codes to 12 Bits. 2.5 V External Reference |

|

±1 |

±1 |

|

VDD = 3 V, 5 V External Reference VDD = 5 V |

Total Unadjusted Error |

LSB typ |

|

||

Unipolar Offset Error |

±1 |

±1 |

LSB max |

2.5 V External Reference VDD = 3 V, 5 V External Reference VDD = 5 V |

Unipolar Offset Error |

(±2.5) |

(±2.5) |

LSB max |

(L Versions, 2.5 V External Reference VDD = 3 V, 5 V External |

|

±2.5 |

±2.5 |

|

Reference VDD = 5 V) |

Positive Full-Scale Error |

LSB max |

2.5 V External Reference VDD = 3 V, 5 V External Reference VDD = 5 V |

||

Positive Full-Scale Error |

(±4) |

(±4) |

LSB max |

(L Versions, 2.5 V External Reference VDD = 3 V, 5 V External |

|

±2.5 |

±2.5 |

|

Reference VDD = 5 V) |

Negative Full-Scale Error |

LSB max |

2.5 V External Reference VDD = 3 V, 5 V External Reference VDD = 5 V |

||

Negative Full-Scale Error |

(±4) |

(±4) |

LSB max |

(L Versions, 2.5 V External Reference VDD = 3 V, 5 V External |

|

±2 |

±2 |

|

Reference VDD = 5 V) |

Bipolar Zero Error |

LSB max |

2.5 V External Reference VDD = 3 V, 5 V External Reference VDD = 5 V |

||

Bipolar Zero Error |

(±2.5) |

(±2.5) |

LSB max |

(L Versions, 2.5 V External Reference VDD = 3 V, 5 V External |

|

|

|

|

Reference VDD = 5 V) |

ANALOG INPUT |

|

|

|

|

Input Voltage Ranges |

0 to VREF |

0 to VREF |

Volts |

i.e., AIN(+) – AIN(–) = 0 to VREF, AIN(–) Can Be Biased |

|

±VREF/2 |

±VREF/2 |

|

Up But AIN(+) Cannot Go Below AIN(–) |

|

Volts |

i.e., AIN(+) – AIN(–) = –VREF/2 to +VREF/2, AIN(–) Should |

||

|

|

|

|

Be Biased to +VREF/2 and AIN(+) Can Go Below AIN(–) But |

|

±1 |

±1 |

µA max |

Cannot Go Below 0 V |

Leakage Current |

|

|||

Input Capacitance |

20 |

20 |

pF typ |

|

|

|

|

|

|

REFERENCE INPUT/OUTPUT |

|

|

|

|

REFIN Input Voltage Range |

2.3/VDD |

2.3/VDD |

V min/max |

Functional from 1.2 V |

Input Impedance |

150 |

150 |

kΩ typ |

|

REFOUT Output Voltage |

2.3/2.7 |

2.3/2.7 |

V min/max |

|

REFOUT Tempco |

20 |

20 |

ppm/°C typ |

|

LOGIC INPUTS |

|

|

|

|

Input High Voltage, VINH |

|

|

|

|

|

2.4 |

2.4 |

V min |

AVDD = DVDD = 4.5 V to 5.5 V |

|

2.1 |

2.1 |

V min |

AVDD = DVDD = 3.0 V to 3.6 V |

Input Low Voltage, VINL |

|

|

|

|

|

0.8 |

0.8 |

V max |

AVDD = DVDD = 4.5 V to 5.5 V |

|

0.6 |

0.6 |

V max |

AVDD = DVDD = 3.0 V to 3.6 V |

Input Current, IIN |

±10 |

±10 |

µA max |

Typically 10 nA, VIN = 0 V or VDD |

Input Capacitance, CIN4 |

10 |

10 |

pF max |

|

–2– |

REV. B |

AD7853/AD7853L

Parameter |

A Version1 |

|

B Version1 |

|

Units |

Test Conditions/Comments |

LOGIC OUTPUTS |

|

|

|

|

|

ISOURCE = 200 µA |

Output High Voltage, VOH |

|

|

|

|

|

|

|

4 |

|

4 |

|

V min |

AVDD = DVDD = 4.5 V to 5.5 V |

|

2.4 |

|

2.4 |

|

V min |

AVDD = DVDD = 3.0 V to 3.6 V |

Output Low Voltage, VOL |

0.4 |

|

0.4 |

|

V max |

ISINK = 0.8 mA |

Floating-State Leakage Current |

±10 |

|

±10 |

|

µA max |

|

Floating-State Output Capacitance4 |

10 |

|

10 |

|

pF max |

|

Output Coding |

Straight (Natural) Binary |

|

|

Unipolar Input Range |

||

|

|

Twos Complement |

|

Bipolar Input Range |

||

|

|

|

|

|

|

|

CONVERSION RATE |

|

|

|

|

|

|

Conversion Time |

4.6 (18) |

|

4.6 (18) |

|

µs max |

(L Versions Only, –40°C to +85°C, 1 MHz CLKIN) |

|

|

|

(10) |

|

µs max |

(L Versions Only, 0°C to +70°C, 1.8 MHz CLKIN) |

Track/Hold Acquisition Time |

0.4 (1) |

|

0.4 (1) |

|

µs min |

(L Versions Only) |

|

|

|

|

|

|

|

POWER REQUIREMENTS |

|

|

|

|

|

|

AVDD, DVDD |

+3.0/+5.5 |

|

+3.0/+5.5 |

|

V min/max |

|

IDD |

|

|

|

|

|

|

Normal Mode5 |

6 (1.9) |

|

6 (1.9) |

|

mA max |

AVDD = DVDD = 4.5 V to 5.5 V. Typically 4.5 mA (1.5); |

Sleep Mode6 |

5.5 (1.9) |

|

5.5 (1.9) |

|

mA max |

AVDD = DVDD = 3.0 V to 3.6 V. Typically 4.0 mA (1.5 mA) |

|

|

|

|

µA typ |

|

|

With External Clock On |

10 |

|

10 |

|

Full Power-Down. Power Management Bits in Control Register |

|

|

|

|

|

|

µA typ |

Set as PMGT1 = 1, PMGT0 = 0 |

|

400 |

|

400 |

|

Partial Power-Down. Power Management Bits in Control |

|

|

|

|

|

|

|

Register Set as PMGT1 = 1, PMGT0 = 1 |

With External Clock Off |

5 |

|

5 |

|

µA max |

Typically 1 µA. Full-Power Down. Power Management Bits in |

|

|

|

|

|

µA typ |

Control Register Set as PMGT1 = 1, PMGT0 = 0 |

|

200 |

|

200 |

|

Partial Power-Down. Power Management Bits in Control |

|

|

|

|

|

|

|

Register Set as PMGT1 = 1, PMGT0 = 1 |

Normal Mode Power Dissipation |

33 (10.5) |

|

33 (10.5) |

|

mW max |

VDD = 5.5 V: Typically 25 mW (8); SLEEP = VDD |

|

20 (6.85) |

|

20 (6.85) |

|

mW max |

VDD = 3.6 V: Typically 15 mW (5.4); SLEEP = VDD |

Sleep Mode Power Dissipation |

|

|

|

|

µW typ |

|

With External Clock On |

55 |

|

55 |

|

VDD = 5.5 V; SLEEP = 0 V |

|

|

36 |

|

36 |

|

µW typ |

VDD = 3.6 V; SLEEP = 0 V |

With External Clock Off |

27.5 |

|

27.5 |

|

µW max |

VDD = 5.5 V: Typically 5.5 µW; SLEEP = 0 V |

|

18 |

|

18 |

|

µW max |

VDD = 3.6 V: Typically 3.6 µW; SLEEP = 0 V |

SYSTEM CALIBRATION |

+0.05 × VREF/–0.05 × VREF |

|

|

|

||

Offset Calibration Span7 |

|

V max/min |

Allowable Offset Voltage Span for Calibration |

|||

Gain Calibration Span7 |

+1.025 × VREF/–0.975 × VREF |

|

V max/min |

Allowable Full-Scale Voltage Span for Calibration |

||

NOTES

1Temperature ranges as follows: A, B Versions, –40°C to +85°C. For L Versions, A and B Versions fCLKIN = 1 MHz over –40°C to +85°C temperature range, B Version fCLKIN = 1.8 MHz over 0°C to +70°C temperature range.

2Specifications apply after calibration.

3SNR calculation includes distortion and noise components.

4Sample tested @ +25°C to ensure compliance.

5All digital inputs @ DGND except for CONVST, SLEEP, CAL, and SYNC @ DVDD. No load on the digital outputs. Analog inputs @ AGND.

6CLKIN @ DGND when external clock off. All digital inputs @ DGND except for CONVST, SLEEP, CAL, and SYNC @ DVDD. No load on the digital outputs. Analog inputs @ AGND.

7The offset and gain calibration spans are defined as the range of offset and gain errors that the AD7853/AD7853L can calibrate. Note also that these are voltage spans and are not absolute voltages (i.e., the allowable system offset voltage presented at AIN(+) for the system offset error to be adjusted out will be AIN(–) ± 0.05 × VREF, and the allowable system full-scale voltage applied between AIN(+) and AIN(–) for the system full-scale voltage error to be adjusted out will be VREF ± 0.025 × VREF). This is explained in more detail in the calibration section of the data sheet.

Specifications subject to change without notice.

REV. B |

–3– |

AD7853/AD7853L

1 (AVDD = DVDD = +3.0 V to +5.5 V; fCLKIN = 4 MHz for AD7853 and 1.8/1 MHz for AD7853L; TA = TMIN to TIMING SPECIFICATIONS TMAX, unless otherwise noted)

|

Limit at TMIN, TMAX |

|

|

||

|

(A, B Versions) |

|

|

||

Parameter |

5 V |

3 V |

Units |

Description |

|

|

|

|

|

|

|

2 |

500 |

500 |

kHz min |

Master Clock Frequency |

|

fCLKIN |

|||||

|

4 |

4 |

MHz max |

L Version, 0°C to +70°C, B Grade Only |

|

|

1.8 |

1.8 |

MHz max |

||

3 |

1 |

1 |

MHz max |

L Version, –40°C to +85°C |

|

4 |

4 |

MHz max |

Interface Modes 1, 2, 3 (External Serial Clock) |

||

fSCLK |

|||||

t14 |

fCLKIN |

fCLKIN |

MHz max |

Interface Modes 4, 5 (Internal Serial Clock) |

|

100 |

100 |

ns min |

CONVST Pulsewidth |

||

t2 |

50 |

90 |

ns max |

CONVST↓ to BUSY↑ Propagation Delay |

|

tCONVERT |

4.6 |

4.6 |

µs max |

Conversion Time = 18 tCLKIN |

|

|

10 (18) |

10 (18) |

µs max |

L Version 1.8 (1) MHz CLKIN. Conversion Time = 18 tCLKIN |

|

t3 |

–0.4 tSCLK |

–0.4 tSCLK |

ns min |

SYNC↓ to SCLK↓ Setup Time (Noncontinuous SCLK Input) |

|

|

70.4 tSCLK |

70.4 tSCLK |

ns min/max |

SYNC↓ to SCLK↓ Setup Time (Continuous SCLK Input) |

|

t4 |

0.6 tSCLK |

0.6 tSCLK |

ns min |

SYNC↓ to SCLK↓ Setup Time. Interface Mode 4 Only |

|

t55 |

50 |

90 |

ns max |

Delay from SYNC↓ until DOUT 3-State Disabled |

|

t5A5 |

50 |

90 |

ns max |

Delay from SYNC↓ until DIN 3-State Disabled |

|

t65 |

75 |

115 |

ns max |

Data Access Time After SCLK↓ |

|

t7 |

40 |

60 |

ns min |

Data Setup Time Prior to SCLK↑ |

|

t8 |

20 |

30 |

ns min |

Data Valid to SCLK Hold Time |

|

t96 |

0.4 tSCLK |

0.4 tSCLK |

ns min |

SCLK High Pulsewidth (Interface Modes 4 and 5) |

|

t106 |

0.4 tSCLK |

0.4 tSCLK |

ns min |

SCLK Low Pulsewidth (Interface Modes 4 and 5) |

|

t11 |

30 |

50 |

ns min |

SCLK↑ to SYNC↑ Hold Time (Noncontinuous SCLK) |

|

|

30/0.4 tSCLK |

50/0.4 tSCLK |

ns min/max |

(Continuous SCLK) Does Not Apply to Interface Mode 3 |

|

t11A |

50 |

50 |

ns max |

SCLK↑ to SYNC↑ Hold Time |

|

t127 |

50 |

50 |

ns max |

Delay from SYNC↑ until DOUT 3-State Enabled |

|

t13 |

90 |

130 |

ns max |

Delay from SCLK↑ to DIN Being Configured as Output |

|

t148 |

50 |

90 |

ns max |

Delay from SCLK↑ to DIN Being Configured as Input |

|

t15 |

2.5 tCLKIN |

2.5 tCLKIN |

ns max |

CAL↑ to BUSY↑ Delay |

|

t16 |

2.5 tCLKIN |

2.5 tCLKIN |

ns max |

CONVST↓ to BUSY↑ Delay in Calibration Sequence |

|

9 |

31.25 |

31.25 |

ms typ |

Full Self-Calibration Time, Master Clock Dependent |

|

tCAL |

|||||

9 |

|

|

|

(125013 tCLKIN) |

|

27.78 |

27.78 |

ms typ |

Internal DAC Plus System Full-Scale Cal Time, Master Clock |

||

tCAL1 |

|||||

9 |

|

|

|

Dependent (111114 tCLKIN) |

|

3.47 |

3.47 |

ms typ |

System Offset Calibration Time, Master Clock Dependent |

||

tCAL2 |

|||||

|

|

|

|

(13899 tCLKIN) |

|

NOTES

Descriptions that refer to SCLK↑ (rising) or SCLK↓ (falling) edges here are with the POLARITY pin HIGH. For the POLARITY pin LOW then the opposite edge of SCLK will apply.

1Sample tested at +25°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of V DD) and timed from a voltage level of 1.6 V. See Table X and timing diagrams for different interface modes and calibration.

2Mark/Space ratio for the master clock input is 40/60 to 60/40.

3For Interface Modes 1, 2, 3 the SCLK max frequency will be 4 MHz. For Interface Modes 4 and 5 the SCLK will be an output and the frequency will be f CLKIN. 4The CONVST pulsewidth will apply here only for normal operation. When the part is in power-down mode, a different CONVST pulsewidth will apply (see Power-

Down section).

5Measured with the load circuit of Figure 1 and defined as the time required for the output to cross 0.8 V or 2.4 V.

6For self-clocking mode (Interface Modes 4, 5) the nominal SCLK high and low times will be 0.5 t SCLK = 0.5 tCLKIN.

7t12 is derived form the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the time, t 12, quoted in the timing characteristics is the true bus relinquish time of the part and is independent of the bus loading.

8t14 is derived form the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the time quoted in the timing characteristics is the true delay of the part in turning off the output drivers and configuring the DIN line as an input. Once this time has elapsed the user can drive the DIN line knowing that a bus conflict will not occur.

9The typical time specified for the calibration times is for a master clock of 4 MHz. For the L version the calibration times will be longer than those quoted here due to the 1.8/1 MHz master clock.

Specifications subject to change without notice.

–4– |

REV. B |

AD7853/AD7853L

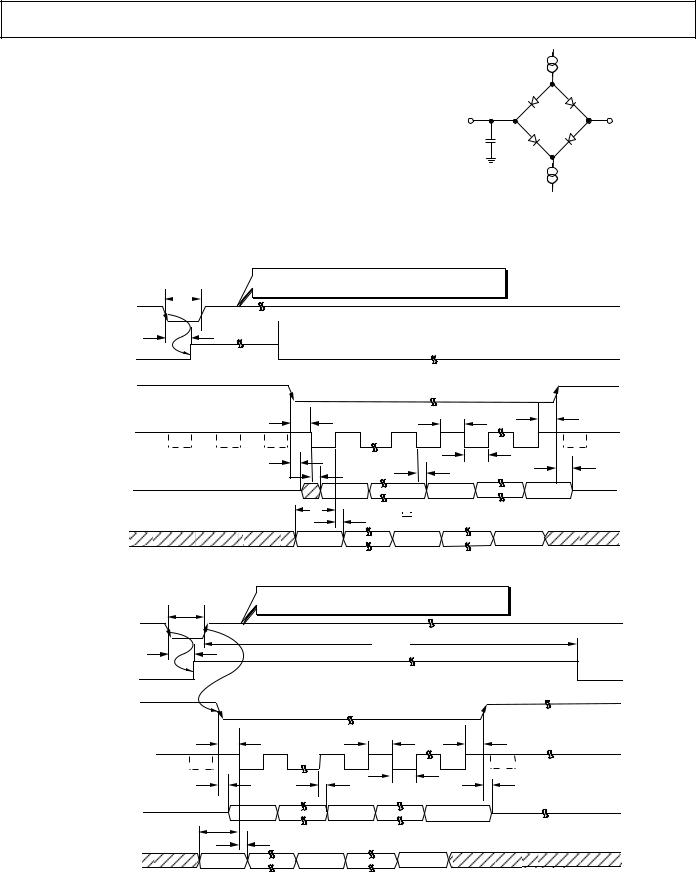

TYPICAL TIMING DIAGRAMS

Figures 2 and 3 show typical read and write timing diagrams. Figure 2 shows the reading and writing after conversion in Interface Modes 2 and 3. To attain the maximum sample rate of 100 kHz (AD7853L) or 200 kHz (AD7853) in Interface Modes 2 and 3, reading and writing must be performed during conversion. Figure 3 shows the timing diagram for Interface Modes 4 and 5 with sample rate of 100 kHz (AD7853L) or 200 kHz (AD7853). At least 400 ns acquisition time must be allowed

(the time from the falling edge of BUSY to the next rising edge of CONVST) before the next conversion begins to ensure that

the part is settled to the 12-bit level. If the user does not want to provide the CONVST signal, the conversion can be initiated in software by writing to the control register.

1.6mA |

IOL |

TO OUTPUT |

+2.1V |

PIN |

|

CL |

|

100pF |

|

200mA |

IOH |

Figure 1. Load Circuit for Digital Output Timing Specifications

POLARITY PIN LOGIC HIGH |

tCONVERT = 4.6ms MAX, 10ms FOR L VERSION |

||

|

t1 |

|

t1 = 100 ns MIN, t5 = 50/90 ns MAX 5V/3V, t7 = 40/60 ns MIN 5V/3V |

CONVST (I/P)

tCONVERT

tCONVERT

t2

BUSY (O/P)

SYNC (I/P)

|

|

t3 |

|

t |

t11 |

|

|

|

|

|

9 |

|

|

SCLK (I/P) |

|

1 |

5 |

6 |

16 |

|

|

|

|

|

|

|

|

|

t5 |

|

|

t10 |

|

|

|

t6 |

|

t6 |

|

t12 |

|

|

|

|

|

|||

DOUT (O/P) |

THREE- |

DB15 |

|

DB11 |

DB0 |

THREE- |

STATE |

|

STATE |

||||

|

|

|

|

|

||

|

|

t7 |

t8 |

|

|

|

|

|

|

|

|

|

|

|

|

DB15 |

DB11 |

|

DB0 |

|

Figure 2. AD7853/AD7853L Timing Diagram (Typical Read and Write Operation for Interface Modes 2, 3)

POLARITY PIN LOGIC HIGH |

tCONVERT = 4.6ms MAX, 10ms FOR L VERSION |

t1 |

t1 = 100 ns MIN, t5 = 50/90 ns MAX 5V/3V, t7 = 40/60 ns MIN 5V/3V |

CONVST (I/P) |

|

t2 |

tCONVERT |

|

|

BUSY (O/P) |

|

SYNC (O/P) |

|

|

|

|

|

|

|

|

t4 |

t9 |

|

|

t11 |

SCLK (O/P) |

|

1 |

5 |

6 |

16 |

|

|

|

|

|

|

|

|

|

t5 |

|

t6 |

t10 |

|

t12 |

|

|

|

|

|||

DOUT (O/P) |

THREE- |

DB15 |

DB11 |

|

DB0 |

THREE- |

STATE |

|

STATE |

||||

|

t7 |

|

|

|

||

|

|

|

|

|

|

|

|

|

t8 |

|

|

|

|

DIN (I/P) |

|

DB15 |

DB11 |

|

DB0 |

|

Figure 3. AD7853/AD7853L Timing Diagram (Typical Read and Write Operation for Interface Modes 4, 5)

REV. B |

–5– |

AD7853/AD7853L

ABSOLUTE MAXIMUM RATINGS1

(TA = +25°C unless otherwise noted)

AVDD to AGND . . . . . . . . . . |

. . . . . . . |

. . . . . |

. –0.3 V to +7 V |

DVDD to DGND . . . . . . . . . . |

. . . . . . . |

. . . . . |

. –0.3 V to +7 V |

AVDD to DVDD . . . . . . . . . . . |

. . . . . . . |

. . . . . |

–0.3 V to +0.3 V |

Analog Input Voltage to AGND . . . . |

–0.3 V to AVDD + 0.3 V |

||

Digital Input Voltage to DGND . . . . |

–0.3 V to DVDD + 0.3 V |

||

Digital Output Voltage to DGND . . . |

–0.3 V to DVDD + 0.3 V |

||

REFIN/REFOUT to AGND . . . |

. . . . . . |

–0.3 V to AVDD + 0.3 V |

|

Input Current to Any Pin Except Supplies2 . . |

. . . . . . ± 10 mA |

||

Operating Temperature Range |

|

–40°C to +85°C |

|

Commercial (A, B Versions) . . . . . . |

. . . . . |

||

Storage Temperature Range |

. . . . . . . |

. . . . |

–65°C to +150°C |

Junction Temperature . . . . . . |

. . . . . . . |

. . . . . |

. . . . . . . +150°C |

Plastic DIP Package, Power Dissipation |

. . . . |

. . . . . . 450 mW |

|

θJA Thermal Impedance . . . |

. . . . . . . |

. . . . . |

. . . . . . 105°C/W |

θJC Thermal Impedance . . . |

. . . . . . . |

. . . . . |

. . . . . 34.7°C/W |

Lead Temperature, (Soldering, 10 sec) . . . |

. . . . . . . +260°C |

||

SOIC, SSOP Package, Power Dissipation . . . |

. . . . . . 450 mW |

||

θJA Thermal Impedance . . . |

75°C/W (SOIC) 115°C/W (SSOP) |

||

θJC Thermal Impedance . . . . |

25°C/W (SOIC) 35°C/W (SSOP) |

||

Lead Temperature, Soldering |

|

+215°C |

|

Vapor Phase (60 sec) . . . |

. . . . . . . |

. . . . . |

|

Infrared (15 sec) . . . . . . . |

. . . . . . . |

. . . . . |

. . . . . . . +220°C |

ESD . . . . . . . . . . . . . . . . . . . . |

. . . . . . . |

. . . . . |

. . . . . . . . >3 kV |

NOTES

1Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2Transient currents of up to 100 mA will not cause SCR latch-up.

ORDERING GUIDE

|

Linearity |

Power |

|

|

Error |

Dissipation |

Package |

Model |

(LSB)1 |

(mW) |

Options2 |

AD7853AN |

± 1 |

20 |

N-24 |

AD7853BN |

±1/2 |

20 |

N-24 |

AD7853LAN3 |

± 1 |

6.85 |

N-24 |

AD7853LBN3 |

± 1 |

6.85 |

N-24 |

AD7853AR |

± 1 |

20 |

R-24 |

AD7853BR |

±1/2 |

20 |

R-24 |

AD7853LAR3 |

± 1 |

6.85 |

R-24 |

AD7853LBR3 |

± 1 |

6.85 |

R-24 |

AD7853ARS |

± 1 |

6.85 |

RS-24 |

AD7853LARS3 |

± 1 |

6.85 |

RS-24 |

EVAL-AD7853CB4 |

|

|

|

EVAL-CONTROL |

BOARD5 |

|

|

NOTES

1Linearity error refers to the integral linearity error. 2N = Plastic DIP; R = SOIC; RS = SSOP.

3L signifies the low power version.

4This can be used as a stand-alone evaluation board or in conjunction with the EVAL-CONTROL BOARD for evaluation/demonstration purposes.

5This board is a complete unit allowing a PC to control and communicate with all Analog Devices, Inc. evaluation boards ending in the CB designators.

PIN CONFIGURATIONS

DIP, SOIC AND SSOP

CONVST |

1 |

|

24 |

SYNC |

|

|

|

|

|

|

|

BUSY |

2 |

|

23 |

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

SLEEP |

3 |

|

22 |

CLKIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

REFI N /REFOUT |

4 |

|

21 |

DIN |

|

|

|

|

|

|

|

AVDD |

5 |

AD7853/53L 20 |

DOUT |

||

|

|

|

|

|

|

AGND |

6 |

TOP VIEW |

19 |

DGND |

|

(Not to Scale) |

|||||

|

|

|

|

||

|

|

|

|

|

|

CREF1 |

7 |

|

18 |

DVDD |

|

|

|

|

|

|

|

CREF2 |

8 |

|

17 |

CAL |

|

AIN(+) |

|

|

|

|

|

|

|

|

|

||

9 |

|

16 |

SM2 |

||

|

|

|

|

|

|

|

|

|

|

|

|

AIN(–) |

10 |

|

15 |

SM1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

11 |

|

14 |

POLARITY |

|

|

|

|

|

|

|

|

|

|

|

|

|

AGND |

12 |

|

13 |

AMODE |

|

|

|

|

|

||

|

NC = NO CONNECT |

|

|

||

–6– |

REV. B |

|

|

|

AD7853/AD7853L |

|||

|

|

|

|

|

|

|

|

|

PIN FUNCTION DESCRIPTIONS |

||||

|

|

|

|

|

|

|

Pin |

Mnemonic |

Description |

||||

|

|

|

|

|

|

|

1 |

CONVST |

Convert Start. Logic Input. A low to high transition on this input puts the track/hold into its hold mode and |

||||

|

|

starts conversion. When this input is not used, it should be tied to DVDD. |

||||

2 |

BUSY |

Busy Output. The busy output is triggered high by the falling edge of |

CONVST |

or rising edge of |

CAL |

, and |

|

|

remains high until conversion is completed. BUSY is also used to indicate when the AD7853/AD7853L has |

||||

|

|

completed its on-chip calibration sequence. |

||||

3 |

SLEEP |

Sleep Input/Low Power Mode. A Logic 0 initiates a sleep and all circuitry is powered down including the |

||||

|

|

internal voltage reference provided there is no conversion or calibration being performed. Calibration data |

||||

|

|

is retained. A Logic 1 results in normal operation. See Power-Down section for more details. |

||||

4 |

REFIN/ |

Reference Input/Output. This pin is connected to the internal reference through a series resistor and is the |

||||

|

REFOUT |

reference source for the analog-to-digital converter. The nominal reference voltage is 2.5 V and this appears |

||||

|

|

at the pin. This pin can be overdriven by an external reference or can be taken as high as AVDD. When this |

||||

|

|

pin is tied to AVDD, or when an externally applied reference approaches AVDD, the CREF1 pin should also be |

||||

|

|

tied to AVDD. |

||||

5 |

AVDD |

Analog Positive Supply Voltage, +3.0 V to +5.5 V. |

||||

6, 12 |

AGND |

Analog Ground. Ground reference for track/hold, reference and DAC. |

||||

7 |

CREF1 |

Reference Capacitor (0.1 F multilayer ceramic). This external capacitor is used as a charge source for the |

||||

|

|

internal DAC. The capacitor should be tied between the pin and AGND. |

||||

8 |

CREF2 |

Reference Capacitor (0.01 F ceramic disc). This external capacitor is used in conjunction with the on-chip |

||||

|

|

reference. The capacitor should be tied between the pin and AGND. |

||||

9 |

AIN(+) |

Analog Input. Positive input of the pseudo-differential analog input. Cannot go below AGND or above |

||||

|

|

AVDD at any time, and cannot go below AIN(–) when the unipolar input range is selected. |

||||

10 |

AIN(–) |

Analog Input. Negative input of the pseudo-differential analog input. Cannot go below AGND or above |

||||

|

|

AVDD at any time. |

||||

11 |

NC |

No Connect Pin. |

||||

13 |

AMODE |

Analog Mode Pin. This pin allows two different analog input ranges to be selected. A Logic 0 selects range |

||||

|

|

0 to VREF (i.e., AIN(+) – AIN(–) = 0 to VREF). In this case AIN(+) cannot go below AIN(–) and |

||||

|

|

AIN(–) cannot go below AGND. A Logic 1 selects range –VREF/2 to +VREF/2 (i.e., AIN(+) – AIN(–) = |

||||

|

|

–VREF/2 to +VREF/2). In this case AIN(+) cannot go below AGND so that AIN(–) needs to be biased to |

||||

|

|

+VREF/2 to allow AIN(+) to go from 0 V to +VREF V. |

||||

14 |

POLARITY |

Serial Clock Polarity. This pin determines the active edge of the serial clock (SCLK). Toggling this pin will |

||||

|

|

reverse the active edge of the serial clock (SCLK). A Logic 1 means that the serial clock (SCLK) idles high |

||||

|

|

and a Logic 0 means that the serial clock (SCLK) idles low. It is best to refer to the timing diagrams and |

||||

|

|

Table IX for the SCLK active edges. |

||||

15 |

SM1 |

Serial Mode Select Pin. This pin is used in conjunction with the SM2 pin to give different modes of opera- |

||||

|

|

tion as described in Table X. |

||||

16 |

SM2 |

Serial Mode Select Pin. This pin is used in conjunction with the SM1 pin to give different modes of opera- |

||||

|

|

tion as described in Table X. |

||||

17 |

CAL |

Calibration Input. This pin has an internal pull-up current source of 0.15 A. A Logic 0 on this pin resets |

||||

|

|

all calibration control logic and initiates a calibration on its rising edge. There is the option of connecting a |

||||

|

|

10 nF capacitor from this pin to DGND to allow for an automatic self-calibration on power-up. This input |

||||

|

|

overrides all other internal operations. If the autocalibration is not required, this pin should be tied to a |

||||

|

|

logic high. |

||||

18 |

DVDD |

Digital Supply Voltage, +3.0 V to +5.5 V. |

||||

19 |

DGND |

Digital Ground. Ground reference point for digital circuitry. |

||||

20 |

DOUT |

Serial Data Output. The data output is supplied to this pin as a 16-bit serial word. |

||||

21 |

DIN |

Serial Data Input. The data to be written is applied to this pin in serial form (16-bit word). This pin can act |

||||

|

|

as an input pin or as a I/O pin depending on the serial interface mode the part is in (see Table X). |

||||

22 |

CLKIN |

Master Clock Signal for the device (4 MHz for AD7853, 1.8 MHz for AD7853L). Sets the conversion and |

||||

|

|

calibration times. |

||||

23 |

SCLK |

Serial Port Clock. Logic input/output. The SCLK pin is configured as an input or output, dependent on the |

||||

|

|

type of serial data transmission (self-clocking or external-clocking) that has been selected by the SM1 and |

||||

|

|

SM2 pins. The SCLK idles high or low depending on the state of the POLARITY pin. |

||||

24 |

SYNC |

This pin can be an input level triggered active low (similar to a chip select in one case and to a frame sync |

||||

|

|

in the other) or an output (similar to a frame sync) pin depending on SM1, SM2 (see Table X). |

||||

|

|

|

||||

REV. B |

–7– |

|||||

AD7853/AD7853L

TERMINOLOGY Integral Nonlinearity

This is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point 1/2 LSB below the first code transition, and full scale, a point 1/2 LSB above the last code transition.

Differential Nonlinearity

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

Total Unadjusted Error

This is the deviation of the actual code from the ideal code taking all errors into account (Gain, Offset, Integral Nonlinearity, and other errors) at any point along the transfer function.

Unipolar Offset Error

This is the deviation of the first code transition (00 . . . 000 to 00 . . . 001) from the ideal AIN(+) voltage (AIN(–) + 1/2 LSB) when operating in the unipolar mode.

Positive Full-Scale Error

This applies to the unipolar and bipolar modes and is the deviation of the last code transition from the ideal AIN(+) voltage (AIN(–) + Full Scale – 1.5 LSB) after the offset error has been adjusted out.

Negative Full-Scale Error

This applies to the bipolar mode only and is the deviation of the first code transition (10 . . . 000 to 10 . . . 001) from the ideal AIN(+) voltage (AIN(–) – VREF/2 + 0.5 LSB).

Bipolar Zero Error

This is the deviation of the midscale transition (all 1s to all 0s) from the ideal AIN(+) voltage (AIN(–) – 1/2 LSB).

Track/Hold Acquisition Time

The track/hold amplifier returns into track mode and the end of conversion. Track/Hold acquisition time is the time required for the output of the track/hold amplifier to reach its final value, within ±1/2 LSB, after the end of conversion.

Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the sum of all nonfundamental signals up to half the sampling frequency (fS/2), excluding dc. The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by:

Signal to (Noise + Distortion) = (6.02 N +1.76) dB

Thus for a 12-bit converter, this is 74 dB.

Total Harmonic Distortion

Total harmonic distortion (THD) is the ratio of the rms sum of harmonics to the fundamental. For the AD7853/AD7853L, it is defined as:

= (V22 +V32 +V 42 +V52 +V62 )

THD (dB) 20 log

V1

where V1 is the rms amplitude of the fundamental and V2, V3, V4, V5 and V6 are the rms amplitudes of the second through the sixth harmonics.

Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to fS/2 and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for parts where the harmonics are buried in the noise floor, it will be a noise peak.

Intermodulation Distortion

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities will create distortion products at sum and difference frequencies of mfa ± nfb where m, n = 0, 1, 2, 3, etc. Intermodulation distortion terms are those for which neither m nor n are equal to zero. For example, the second order terms include (fa + fb) and (fa – fb), while the third order terms include (2fa + fb), (2fa – fb), (fa + 2fb) and (fa – 2fb).

Testing is performed using the CCIF standard where two input frequencies near the top end of the input bandwidth are used. In this case, the second order terms are usually distanced in frequency from the original sine waves while the third order terms are usually at a frequency close to the input frequencies. As a result, the second and third order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification where it is the ratio of the rms sum of the individual distortion products to the rms amplitude of the sum of the fundamentals expressed in dBs.

–8– |

REV. B |

AD7853/AD7853L

ON-CHIP REGISTERS

The AD7853/AD7853L powers up with a set of default conditions, and the user need not ever write to the device. In this case the AD7853/AD7853L will operate as a Read-Only ADC. The AD7853/AD7853L still retains the flexibility for performing a full powerdown, and a full self-calibration. Note that the DIN pin should be tied to DGND for operating the AD7853/AD7853L as a ReadOnly ADC.

Extra features and flexibility such as performing different power-down options, different types of calibrations including system calibration, and software conversion start can be selected by writing to the part.

The AD7853/AD7853L contains a Control register, ADC output data register, Status register, Test register and 10 Calibration registers. The control register is write-only, the ADC output data register and the status register are read-only, and the test and calibration registers are both read/write registers. The test register is used for testing the part and should not be written to.

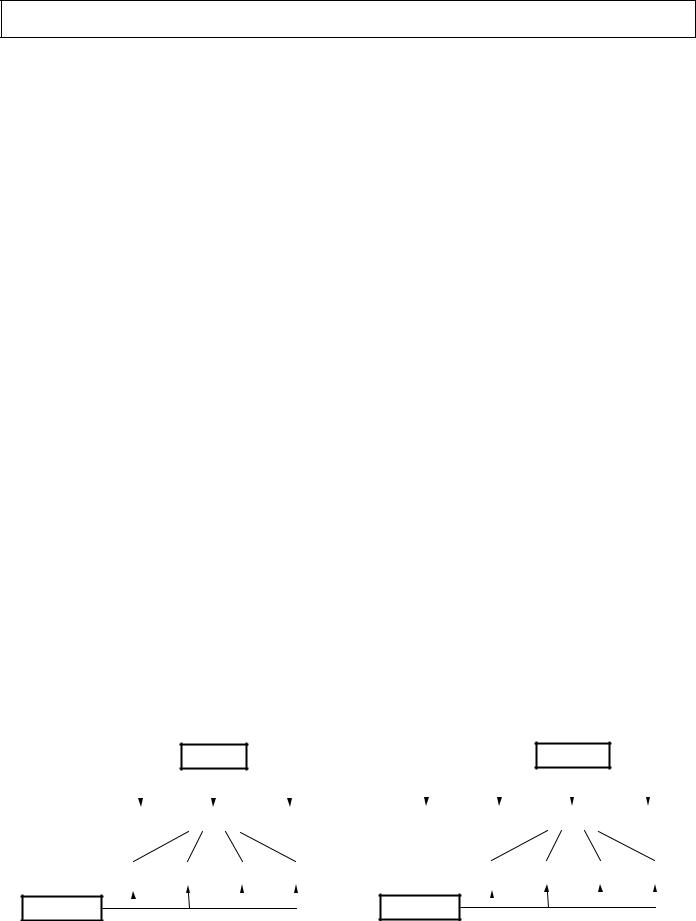

Addressing the On-Chip Registers

Writing

A write operation to the AD7853/AD7853L consists of 16 bits. The two MSBs, ADDR0 and ADDR1, are decoded to determine which register is addressed, and the subsequent 14 bits of data are written to the addressed register. It is not until all 16 bits are written that the data is latched into the addressed register. Table I shows the decoding of the address bits, while Figure 4 shows the overall write register hierarchy.

|

|

Table I. Write Register Addressing |

|

|

|

ADDR1 |

ADDR0 |

Comment |

|

|

|

0 |

0 |

This combination does not address any register so the subsequent 14 data bits are ignored. |

0 |

1 |

This combination addresses the TEST REGISTER. The subsequent 14 data bits are written to the test register. |

1 |

0 |

This combination addresses the CALIBRATION REGISTERS. The subsequent 14 data bits are written |

|

|

to the selected calibration register. |

1 |

1 |

This combination addresses the CONTROL REGISTER. The subsequent 14 data bits are written to the |

|

|

control register. |

|

|

|

Reading

To read from the various registers the user must first write to Bits 6 and 7 in the Control Register, RDSLT0 and RDSLT1. These bits are decoded to determine which register is addressed during a read operation. Table II shows the decoding of the read address bits while Figure 5 shows the overall read register hierarchy. The power-up status of these bits is 00 so that the default read will be from the ADC output data register.

Once the read selection bits are set in the control register all subsequent read operations that follow will be from the selected register until the read selection bits are changed in the control register.

|

|

Table II. Read Register Addressing |

|

|

|

RDSLT1 |

RDSLT0 |

Comment |

|

|

|

0 |

0 |

All successive read operations will be from ADC OUTPUT DATA REGISTER. This is the power-up |

|

|

default setting. There will always be four leading zeros when reading from the ADC output data register. |

0 |

1 |

All successive read operations will be from TEST REGISTER. |

1 |

0 |

All successive read operations will be from CALIBRATION REGISTERS. |

1 |

1 |

All successive read operations will be from STATUS REGISTER. |

|

|

|

ADDR1, ADDR0

DECODE

RDSLT1, RDSLT0

DECODE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

01 |

|

|

|

10 |

|

|

|

|

|

|

|

|

|

11 |

|

|

00 |

|

|

|

01 |

|

|

|

10 |

|

|

|

|

|

|

|

|

|

11 |

|

|||||||||

|

|

TEST |

|

|

CALIBRATION |

|

|

CONTROL |

|

|

ADC OUTPUT |

|

TEST |

|

|

CALIBRATION |

|

|

|

STATUS |

|||||||||||||||||||||||||||

|

|

REGISTER |

|

|

REGISTERS |

|

|

REGISTER |

|

|

DATA REGISTER |

|

REGISTER |

|

|

REGISTERS |

|

|

REGISTER |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GAIN(1) |

|

|

GAIN(1) |

|

|

OFFSET(1) |

|

GAIN(1) |

|

|

|

|

|

|

|

GAIN(1) |

|

|

GAIN(1) |

|

|

OFFSET(1) |

|

GAIN(1) |

|

||||||||||||||||||||

|

|

OFFSET(1) |

|

OFFSET(1) |

|

|

|

|

|

|

|

|

|

OFFSET(1) |

|

OFFSET(1) |

|

|

|

|

|||||||||||||||||||||||||||

|

|

DAC(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DAC(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

CALSLT1, CALSLT0 |

00 |

|

|

|

|

01 |

|

10 |

|

|

|

11 |

|

|

|

CALSLT1, CALSLT0 |

00 |

|

|

|

|

01 |

|

10 |

|

|

|

11 |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

DECODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DECODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Figure 4. Write Register Hierarchy/Address Decoding |

Figure 5. Read Register Hierarchy/Address Decoding |

||||||||||||||||||||||||||||||||||||||||||||||

REV. B |

–9– |

AD7853/AD7853L

CONTROL REGISTER

The arrangement of the control register is shown below. The control register is a write only register and contains 14 bits of data. The control register is selected by putting two 1s in ADDR1 and ADDR0. The function of the bits in the control register are described below. The power-up status of all bits is 0.

|

|

|

|

|

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ZERO |

|

|

ZERO |

|

ZERO |

|

ZERO |

PMGT1 |

|

PMGT0 |

RDSLT1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RDSLT0 |

2/3 MODE |

|

CONVST |

|

CALMD |

CALSLT1 |

|

CALSLT0 |

STCAL |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

Control Register Bit Function Descriptions |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit |

|

Mnemonic |

|

|

Comment |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

13 |

|

ZERO |

|

|

These four bits must be set to 0 when writing to the control register. |

|

|

|||||||||||||||

12 |

|

ZERO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

11 |

|

ZERO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

10 |

|

ZERO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

9 |

|

PMGT1 |

|

|

Power Management Bits. These two bits are used with the |

|

pin for putting the part into various |

|||||||||||||||

|

|

SLEEP |

||||||||||||||||||||

8 |

|

PMGT0 |

|

|

power-down modes (See Power-Down section for more details). |

|

|

|||||||||||||||

7 |

|

RDSLT1 |

|

|

These two bits determine which register is addressed for the read operations. See Table II. |

|||||||||||||||||

6 |

|

RDSLT0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

5 |

|

2/ |

|

MODE |

|

|

Interface Mode Select Bit. With this bit set to 0, Interface Mode 2 is enabled. With this bit set to 1, |

|||||||||||||||

3 |

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

Interface Mode 1 is enabled where DIN is used as an output as well as an input. This bit is set to 0 by |

||||||||||||

|

|

|

|

|

|

|

|

|

|

default after every read cycle; thus when using Interface Mode 1, this bit needs to be set to 1 in every |

||||||||||||

|

|

|

|

|

|

|

|

|

|

write cycle. |

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

CONVST |

|

|

Conversion Start Bit. A logic one in this bit position starts a single conversion, and this bit is automati- |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

cally reset to 0 at the end of conversion. This bit may also used in conjunction with system calibration |

||||||||||||

|

|

|

|

|

|

|

|

|

|

(see Calibration Section on page 21). |

|

|

|

|

|

|

|

|||||

3 |

|

CALMD |

|

|

Calibration Mode Bit. A 0 here selects self-calibration and a 1 selects a system calibration (see Table III). |

|||||||||||||||||

2 |

|

CALSLT1 |

|

|

Calibration Selection Bits and Start Calibration Bit. These bits have two functions. |

|||||||||||||||||

1 |

|

CALSLT0 |

|

|

With the STCAL bit set to 1, the CALSLT1 and CALSLT0 bits determine the type of calibration per- |

|||||||||||||||||

0 |

|

STCAL |

|

|

formed by the part (see Table III). The STCAL bit is automatically reset to 0 at the end of calibration. |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

With the STCAL bit set to 0, the CALSLT1 and CALSLT0 bits are decoded to address the calibration |

||||||||||||

|

|

|

|

|

|

|

|

|

|

register for read/write of calibration coefficients (see section on the calibration registers for more details). |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Table III. Calibration Selection |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CALMD |

|

|

CALSLT1 |

|

CALSLT0 |

Calibration Type |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

0 |

|

|

0 |

|

|

0 |

|

A full internal calibration is initiated where the internal DAC is calibrated followed by the |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

internal gain error and finally the internal offset error is calibrated out. This is the default setting. |

|||||||||||

0 |

|

|

0 |

|

|

1 |

|

Here the internal gain error is calibrated out followed by the internal offset error calibrated |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

out. |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

|

|

0 |

|

This calibrates out the internal offset error only. |

|

|

||||||||||||

0 |

|

|

1 |

|

|

1 |

|

This calibrates out the internal gain error only. |

|

|

||||||||||||

1 |

|

|

0 |

|

|

0 |

|

A full system calibration is initiated here where first the internal DAC is calibrated, fol- |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

lowed by the system gain error, and finally the system offset error is calibrated out. |

|||||||||||

1 |

|

|

0 |

|

|

1 |

|

Here the system gain error is calibrated out followed by the system offset error. |

||||||||||||||

1 |

|

|

1 |

|

|

0 |

|

This calibrates out the system offset error only. |

|

|

||||||||||||

1 |

|

|

1 |

|

|

1 |

|

This calibrates out the system gain error only. |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–10– |

REV. B |

AD7853/AD7853L

STATUS REGISTER

The arrangement of the status register is shown below. The status register is a read-only register and contains 16 bits of data. The status register is selected by first writing to the control register and putting two 1s in RDSLT1 and RDSLT0. The function of the bits in the status register are described below. The power-up status of all bits is 0.

|

|

|

|

|

|

|

|

START |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WRITE TO CONTROL REGISTER |

|

|

|

|

|

||

|

|

|

|

|

|

|

SETTING RDSLT0 = RDSLT1 = 1 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

READ STATUS REGISTER |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 6. Flowchart for Reading the Status Register |

|

|

|||||||

|

MSB |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ZERO |

BUSY |

ZERO |

|

ZERO |

|

ZERO |

|

ZERO |

PMGT1 |

PMGT0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RDSLT1 |

RDSLT0 |

2/3 MODE |

|

X |

|

CALMD |

|

CALSLT1 |

CALSLT0 |

STCAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LSB |

|

|

|

|

|

|

Status Register Bit Function Descriptions |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Bit |

Mnemonic |

|

Comment |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

ZERO |

|

This bit is always 0. |

|

|

|

|

|

|

|

|

|||

14 |

BUSY |

|

Conversion/Calibration Busy Bit. When this bit is 1, it indicates that there is a conversion or calibration in |

|||||||||||

|

|

|

|

progress. When this bit is 0, no conversion or calibration is in progress. |

|

|

||||||||

13 |

ZERO |

|

These four bits are always 0. |

|

|

|

|

|

|

|

|

|||

12 |

ZERO |

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

ZERO |

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

ZERO |

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

PMGT1 |

|

Power Management Bits. These bits, along with the SLEEP pin, will indicate whether or not the part is in a |

|||||||||||

8 |

PMGT0 |

|

power-down mode. See Table VI in Power-Down Section for description. |

|

|

|||||||||

7 |

RDSLT1 |

|

Both of these bits are always 1, indicating it is the status register that is being read. See Table II. |

|||||||||||

6 |

RDSLT0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

5 |

2/3 MODE |

|

Interface Mode Select Bit. With this bit at 0, the device is in Interface Mode 2. With this bit at 1, the device |

|||||||||||

|

|

|

|

is in Interface Mode 1. This bit is reset to 0 after every read cycle. |

|

|

|

|||||||

4 |

X |

|

Don’t care bit. |

|

|

|

|

|

|

|

|

|||

3 |

CALMD |

|

Calibration Mode Bit. A 0 in this bit indicates a self-calibration is selected; a 1 in this bit indicates a system |

|||||||||||

|

|

|

|

calibration is selected (see Table III). |

|

|

|

|

|

|

|

|||

2 |

CALSLT1 |

|

Calibration Selection Bits and Start Calibration Bit. The STCAL bit is read as a 1 if a calibration is in |

|||||||||||

1 |

CALSLT0 |

|

progress and as a 0 if no calibration is in progress. The CALSLT1 and CALSLT0 bits indicate |

|||||||||||

0 |

STCAL |

|

which of the calibration registers are addressed for reading and writing (see section on the Calibration |

|||||||||||

|

|

|

|

Registers for more details). |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REV. B |

–11– |

Loading...

Loading...