Analog Devices AD8403ARU50-REEL, AD8403ARU50, AD8400AN1, AD8400ARU100-REEL, AD8400ARU100 Datasheet

...

a |

1-/2-/4-Channel |

|

Digital Potentiometers |

||

|

|

AD8400/AD8402/AD8403 |

FEATURES 256-Position

Replaces 1, 2, or 4 Potentiometers 1 k , 10 k , 50 k , 100 k Power Shutdown—Less than 5 A

3-Wire SPI-Compatible Serial Data Input

10 MHz Update Data Loading Rate

2.7 V to 5.5 V Single-Supply Operation Midscale Preset

APPLICATIONS

Mechanical Potentiometer Replacement

Programmable Filters, Delays, Time Constants

Volume Control, Panning

Line Impedance Matching

Power Supply Adjustment

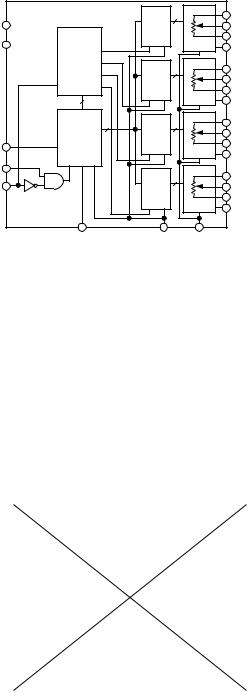

FUNCTIONAL BLOCK DIAGRAM

|

AD8403 |

|

8-BIT |

RDAC1 |

A1 |

VDD |

|

8 |

|||

DAC |

|

LATCH |

|

W1 |

|

|

|

CK RS |

|

B1 |

|

DGND |

SELECT |

1 |

SHDN |

AGND1 |

|

|

|

||||

|

|

|

|

|

|

|

|

2 |

|

RDAC2 |

A2 |

|

|

3 |

8-BIT |

8 |

|

|

|

4 |

LATCH |

|

W2 |

|

A1, A0 |

|

B2 |

||

|

CK RS |

|

|||

|

2 |

|

SHDN |

AGND2 |

|

|

|

|

|||

|

10-BIT |

8 |

|

RDAC3 |

A3 |

|

SERIAL |

8-BIT |

8 |

||

|

W3 |

||||

|

LATCH |

|

LATCH |

|

|

SDI |

D |

|

CK RS |

|

B3 |

|

SHDN |

AGND3 |

|||

|

|

|

|||

|

CK Q RS |

|

|||

CLK |

|

|

|

||

|

|

|

RDAC4 |

A4 |

|

|

|

|

8-BIT |

8 |

|

CS |

|

|

W4 |

||

|

|

LATCH |

|

||

|

|

|

|

B4 |

|

|

|

|

CK RS |

|

|

|

|

|

SHDN |

AGND4 |

|

|

|

|

|

||

|

SDO |

|

RS |

SHDN |

|

GENERAL DESCRIPTION

The AD8400/AD8402/AD8403 provide a single, dual or quad channel, 256 position digitally controlled variable resistor (VR) device. These devices perform the same electronic adjustment function as a potentiometer or variable resistor. The AD8400 contains a single variable resistor in the compact SO-8 package. The AD8402 contains two independent variable resistors in space-saving SO-14 surfacemount packages. The AD8403 contains four independent variable resistors in 24-lead PDIP, SOIC, and TSSOP packages. Each part contains a fixed resistor with a wiper contact that taps the fixed resistor value at a point determined by a digital code loaded into the controlling serial input register. The resistance between the wiper and either endpoint of the fixed resistor varies linearly with respect to the digital code transferred into the VR latch. Each variable resistor offers a completely programmable value of resistance, between the A terminal and the wiper or the B terminal and the wiper. The fixed A to B terminal resistance of 1 kΩ, 10 kΩ, 50 kΩ, or 100 kΩ has a ±1% channel-to-channel matching tolerance with a nominal temperature coefficient of 500 ppm/°C. A unique switching circuit minimizes the high glitch inherent in traditional switched resistor designs avoiding any make-before-break or break-before-make operation.

Each VR has its own VR latch that holds its programmed resistance value. These VR latches are updated from an SPI compatible serial- to-parallel shift register that is loaded from a standard 3-wire serial-input digital interface. Ten data bits make up the data word clocked into the serial input register. The data word is decoded where the first two bits determine the address of the VR latch to be loaded, the last eight bits are data. A serial data output pin at the opposite end of the serial register allows simple daisy-chaining in multiple VR applications without additional external decoding logic.

The reset (RS) pin forces the wiper to the midscale position by loading 80H into the VR latch. The SHDN pin forces the resistor

REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

to an end-to-end open circuit condition on the A terminal and shorts the wiper to the B terminal, achieving a microwatt power shutdown state. When SHDN is returned to logic high, the previous latch settings put the wiper in the same resistance setting prior to shutdown. The digital interface is still active in shutdown so that code changes can be made that will produce new wiper positions when the device is taken out of shutdown.

The AD8400 is available in both the SO-8 surface-mount and the 8-lead plastic DIP package.

The AD8402 is available in both surface mount (SO-14) and 14-lead plastic DIP packages, while the AD8403 is available in a narrow body 24-lead plastic DIP and a 24-lead surface-mount package. The AD8402/AD8403 are also offered in the 1.1 mm thin TSSOP-14/TSSOP-24 packages for PCMCIA applications. All parts are guaranteed to operate over the extended industrial temperature range of –40°C to +125°C.

|

100 |

|

|

|

|

|

|

|

|

|

AB |

|

RWA |

|

|

|

|

RWB |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

R |

50 |

|

|

|

|

|

|

|

|

|

Nominalof%– |

|

|

|

|

|

|

|

|

|

|

(D) |

75 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WB |

|

|

|

|

|

|

|

|

|

|

(D), R |

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

WA |

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

0 |

64 |

128 |

192 |

255 |

|||||

|

|

|

|

|

CODE – Decimal |

|

|

|||

|

|

Figure 1. RWA and RWB vs. Code |

|

|

||||||

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. |

||||||||||

Tel: 781/329-4700 |

|

|

|

|

|

www.analog.com |

||||

Fax: 781/326-8703 |

|

|

|

|

© Analog Devices, Inc., 2002 |

|||||

|

|

|

|

|

(VDD = 3 V 10% or 5 V 10%, VA = VDD, VB = 0 V, |

|||||

|

AD8400/AD8402/AD8403–SPECIFICATIONS –40 C ≤ TA ≤ +125 C unless otherwise noted.) |

|||||||||

ELECTRICAL CHARACTERISTICS–10 k VERSION |

|

|

|

|

|

|||||

|

Parameter |

Symbol |

|

Conditions |

Min |

Typ1 |

Max |

Unit |

|

|

|

DC CHARACTERISTICS RHEOSTAT MODE (Specifications Apply to All VRs) |

|

± 1/4 |

|

|

|

||||

|

Resistor Differential NL2 |

|

R-DNL |

|

RWB, VA = No Connect |

–1 |

+1 |

LSB |

||

|

|

|

||||||||

|

Resistor Nonlinearity2 |

|

R-INL |

|

RWB, VA = No Connect |

–2 |

± 1/2 |

+2 |

LSB |

|

|

Nominal Resistance3 |

|

RAB |

|

TA = 25°C, Model: AD840XYY10 |

8 |

10 |

12 |

kΩ |

|

|

Resistance Tempco |

|

∆RAB/∆T |

|

VAB = VDD, Wiper = No Connect |

|

500 |

|

ppm/°C |

|

|

Wiper Resistance |

|

RW |

|

IW = 1 V/R |

|

50 |

100 |

Ω |

|

|

Nominal Resistance Match |

|

∆R/RAB |

|

CH 1 to 2, 3, or 4, VAB = VDD, TA = 25°C |

|

0.2 |

1 |

% |

|

|

DC CHARACTERISTICS POTENTIOMETER DIVIDER Specifications Apply to All VRs |

|

|

|

|

|

||||

|

Resolution |

|

N |

|

|

8 |

± 1/2 |

|

Bits |

|

|

|

|

|

|

||||||

|

Integral Nonlinearity4 |

|

INL |

|

|

–2 |

+2 |

LSB |

||

|

Differential Nonlinearity4 |

|

DNL |

|

VDD = 5 V |

–1 |

± 1/4 |

+1 |

LSB |

|

|

|

|

DNL |

|

VDD = 3 V TA = 25°C |

–1 |

± 1/4 |

+1 |

LSB |

|

|

|

|

DNL |

|

VDD = 3 V TA = –40°C, +85°C |

–1.5 |

± 1/2 |

+1.5 |

LSB |

|

|

Voltage Divider Tempco |

|

∆VW/∆T |

|

Code = 80H |

|

15 |

|

ppm/°C |

|

|

Full-Scale Error |

|

VWFSE |

|

Code = FFH |

–4 |

–2.8 |

0 |

LSB |

|

|

Zero-Scale Error |

|

VWZSE |

|

Code = 00H |

0 |

1.3 |

2 |

LSB |

|

|

RESISTOR TERMINALS |

|

|

|

|

|

|

|

|

|

|

Voltage Range5 |

|

VA, B, W |

|

|

0 |

|

VDD |

V |

|

|

Capacitance6 Ax, Bx |

|

CA, B |

|

f = 1 MHz, Measured to GND, Code = 80H |

|

75 |

|

pF |

|

|

Capacitance6 Wx |

|

CW |

|

f = 1 MHz, Measured to GND, Code = 80H |

|

120 |

|

pF |

|

|

Shutdown Current7 |

|

IA_SD |

|

VA = VDD, VB = 0 V, SHDN = 0 |

|

0.01 |

5 |

µA |

|

|

Shutdown Wiper Resistance |

|

RW_SD |

|

VA = VDD, VB = 0 V, SHDN = 0, VDD = 5 V |

|

100 |

200 |

Ω |

|

|

DIGITAL INPUTS AND OUTPUTS |

|

|

|

|

|

|

|

|

|

|

Input Logic High |

|

VIH |

|

VDD = 5 V |

2.4 |

|

|

V |

|

|

Input Logic Low |

|

VIL |

|

VDD = 5 V |

|

|

0.8 |

V |

|

|

Input Logic High |

|

VIH |

|

VDD = 3 V |

2.1 |

|

|

V |

|

|

Input Logic Low |

|

VIL |

|

VDD = 3 V |

|

|

0.6 |

V |

|

|

Output Logic High |

|

VOH |

|

RL = 2.2 kΩ to VDD |

VDD – 0.1 |

|

|

V |

|

|

Output Logic Low |

|

VOL |

|

IOL = 1.6 mA, VDD = 5 V |

|

|

0.4 |

V |

|

|

Input Current |

|

IIL |

|

VIN = 0 V or +5 V, VDD = 5 V |

|

|

± 1 |

µA |

|

|

Input Capacitance6 |

|

CIL |

|

|

|

5 |

|

pF |

|

|

POWER SUPPLIES |

|

|

|

|

|

|

|

|

|

|

Power Supply Range |

|

VDD Range |

|

|

2.7 |

|

5.5 |

V |

|

|

Supply Current (CMOS) |

|

IDD |

|

VIH = VDD or VIL = 0 V |

|

0.01 |

5 |

µA |

|

|

Supply Current (TTL)8 |

|

IDD |

|

VIH = 2.4 V or 0.8 V, VDD = 5.5 V |

|

0.9 |

4 |

mA |

|

|

Power Dissipation (CMOS)9 |

|

PDISS |

|

VIH = VDD or VIL = 0 V, VDD = 5.5 V |

|

|

27.5 |

µW |

|

|

Power Supply Sensitivity |

|

PSS |

|

VDD = 5 V ± 10% |

|

0.0002 |

0.001 |

%/% |

|

|

|

|

PSS |

|

VDD = 3 V ± 10% |

|

0.006 |

0.03 |

%/% |

|

|

DYNAMIC CHARACTERISTICS6, 10 |

|

|

|

R = 10 kΩ |

|

|

|

|

|

|

Bandwidth –3 dB |

|

BW_10K |

|

|

600 |

|

kHz |

||

|

Total Harmonic Distortion |

|

THDW |

|

VA = 1 V rms + 2 V dc, VB = 2 V dc, f = 1 kHz |

|

0.003 |

|

% |

|

|

VW Settling Time |

|

tS |

|

VA = VDD, VB = 0 V, ±1% Error Band |

|

2 |

|

µs |

|

|

Resistor Noise Voltage |

|

eNWB |

|

RWB = 5 kΩ, f = 1 kHz, RS = 0 |

|

9 |

|

nV/√Hz |

|

|

Crosstalk11 |

|

CT |

|

VA = VDD, VB = 0 V |

|

–65 |

|

dB |

|

NOTES

1Typicals represent average readings at 25°C and VDD = 5 V.

2Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See TPC 29 test circuit.

IW = 50 µA for VDD = 3 V and IW = 400 µA for VDD = 5 V for the 10 kΩ versions. 3VAB = VDD, Wiper (VW) = No Connect.

4INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0 V. DNL Specification limits of ±1 LSB maximum are Guaranteed Monotonic operating conditions. See TPC 28 test circuit.

5Resistor terminals A, B, W have no limitations on polarity with respect to each other.

6Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

7Measured at the Ax terminals. All Ax terminals are open circuited in shutdown mode.

8Worst-case supply current consumed when input logic level at 2.4 V, standard characteristic of CMOS logic. See TPC 20 for a plot of IDD versus logic voltage. 9PDISS is calculated from (IDD × VDD). CMOS logic level inputs result in minimum power dissipation.

10All Dynamic Characteristics use VDD = 5 V.

11Measured at a VW pin where an adjacent VW pin is making a full-scale voltage change. Specifications subject to change without notice.

–2– |

REV. C |

AD8400/AD8402/AD8403

SPECIFICATIONS (VDD = 3 V 10% or 5 V 10%, VA = VDD, VB = 0 V, –40 C ≤ TA ≤ +125 C unless otherwise noted.)

ELECTRICAL CHARACTERISTICS–50 k and 100 k VERSIONS

Parameter |

|

Symbol |

|

Conditions |

Min |

Typ1 |

Max |

Unit |

|

DC CHARACTERISTICS RHEOSTAT MODE (Specifications Apply to All VRs) |

|

± 1/4 |

|

|

|||||

Resistor Differential NL2 |

|

R-DNL |

|

RWB, VA = No Connect |

–1 |

+1 |

LSB |

||

|

|

||||||||

Resistor Nonlinearity2 |

|

R-INL |

|

RWB, VA = No Connect |

–2 |

± 1/2 |

+2 |

LSB |

|

Nominal Resistance3 |

|

RAB |

|

TA = 25°C, Model: AD840XYY50 |

35 |

50 |

65 |

kΩ |

|

|

|

RAB |

|

TA = 25°C, Model: AD840XYY100 |

70 |

100 |

130 |

kΩ |

|

Resistance Tempco |

|

∆RAB/∆T |

|

VAB = VDD, Wiper = No Connect |

|

500 |

|

ppm/°C |

|

Wiper Resistance |

|

RW |

|

IW = 1 V/R |

|

53 |

100 |

Ω |

|

Nominal Resistance Match |

|

∆R/RAB |

|

CH 1 to 2, 3, or 4, VAB = VDD, TA = 25°C |

|

0.2 |

1 |

% |

|

DC CHARACTERISTICS POTENTIOMETER DIVIDER (Specifications Apply to All VRs) |

|

|

|

|

|||||

Resolution |

|

N |

|

|

|

8 |

± 1 |

|

Bits |

|

|

|

|

|

|||||

Integral Nonlinearity4 |

|

INL |

|

|

|

–4 |

+4 |

LSB |

|

Differential Nonlinearity4 |

|

DNL |

|

|

VDD = 5 V |

–1 |

± 1/4 |

+1 |

LSB |

|

|

DNL |

|

|

VDD = 3 V TA = 25°C |

–1 |

± 1/4 |

+1 |

LSB |

|

|

DNL |

|

|

VDD = 3 V TA = –40°C, +85°C |

–1.5 |

± 1/2 |

+1.5 |

LSB |

Voltage Divider Tempco |

|

∆VW/∆T |

|

|

Code = 80H |

|

15 |

|

ppm/°C |

Full-Scale Error |

|

VWFSE |

|

|

Code = FFH |

–1 |

–0.25 |

0 |

LSB |

Zero-Scale Error |

|

VWZSE |

|

|

Code = 00H |

0 |

+0.1 |

+1 |

LSB |

RESISTOR TERMINALS |

|

|

|

|

|

|

|

|

|

Voltage Range5 |

|

VA, B, W |

|

|

|

0 |

|

VDD |

V |

Capacitance6 Ax, Bx |

|

CA, B |

|

|

f = 1 MHz, Measured to GND, Code = 80H |

|

15 |

|

pF |

Capacitance6 Wx |

|

CW |

|

|

f = 1 MHz, Measured to GND, Code = 80H |

|

80 |

|

pF |

Shutdown Current7 |

|

IA_SD |

|

|

VA = VDD, VB = 0 V, SHDN = 0 |

|

0.01 |

5 |

µA |

Shutdown Wiper Resistance |

|

RW_SD |

|

|

VA = VDD, VB = 0 V, SHDN = 0, VDD = 5 V |

|

100 |

200 |

Ω |

DIGITAL INPUTS AND OUTPUTS |

|

|

|

|

|

|

|

|

|

Input Logic High |

|

VIH |

|

|

VDD = 5 V |

2.4 |

|

|

V |

Input Logic Low |

|

VIL |

|

|

VDD = 5 V |

|

|

0.8 |

V |

Input Logic High |

|

VIH |

|

|

VDD = 3 V |

2.1 |

|

|

V |

Input Logic Low |

|

VIL |

|

|

VDD = 3 V |

|

|

0.6 |

V |

Output Logic High |

|

VOH |

|

|

RL = 2.2 kΩ to VDD |

VDD – 0.1 |

|

|

V |

Output Logic Low |

|

VOL |

|

|

IOL = 1.6 mA, VDD = 5 V |

|

|

0.4 |

V |

Input Current |

|

IIL |

|

|

VIN = 0 V or 5 V, VDD = 5 V |

|

|

± 1 |

µA |

Input Capacitance6 |

|

CIL |

|

|

|

|

5 |

|

pF |

POWER SUPPLIES |

|

|

|

|

|

|

|

|

|

Power Supply Range |

|

VDD Range |

|

|

|

2.7 |

|

5.5 |

V |

Supply Current (CMOS) |

|

IDD |

|

|

VIH = VDD or VIL = 0 V |

|

0.01 |

5 |

µA |

Supply Current (TTL)8 |

|

IDD |

|

|

VIH = 2.4 V or 0.8 V, VDD = 5.5 V |

|

0.9 |

4 |

mA |

Power Dissipation (CMOS)9 |

|

PDISS |

|

|

VIH = VDD or VIL = 0 V, VDD = 5.5 V |

|

|

27.5 |

µW |

Power Supply Sensitivity |

|

PSS |

|

|

VDD = 5 V ± 10% |

|

0.0002 |

0.001 |

%/% |

|

|

PSS |

|

|

VDD = 3 V ± 10% |

|

0.006 |

0.03 |

%/% |

DYNAMIC CHARACTERISTICS6, 10 |

|

|

|

|

R = 50 kΩ |

|

|

|

|

Bandwidth –3 dB |

|

BW_50K |

|

|

|

125 |

|

kHz |

|

|

|

BW_100K |

|

|

R = 100 kΩ |

|

71 |

|

kHz |

Total Harmonic Distortion |

|

THDW |

|

|

VA = 1 V rms + 2 V dc, VB = 2 V dc, f = 1 kHz |

|

0.003 |

|

% |

VW Settling Time |

|

tS_50K |

|

|

VA = VDD, VB = 0 V, ±1% Error Band |

|

9 |

|

µs |

|

|

tS_100K |

|

|

VA = VDD, VB = 0 V, ±1% Error Band |

|

18 |

|

µs |

Resistor Noise Voltage |

|

eNWB_50K |

|

|

RWB = 25 kΩ, f = 1 kHz, RS = 0 |

|

20 |

|

nV/√Hz |

Crosstalk11 |

|

eNWB_100K |

|

|

RWB = 50 kΩ, f = 1 kHz, RS = 0 |

|

29 |

|

nV/√Hz |

|

CT |

|

|

VA = VDD, VB = 0 V |

|

–65 |

|

dB |

|

NOTES

1Typicals represent average readings at 25°C and VDD = 5 V.

2Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See TPC 29 test circuit.

IW = VDD/R for VDD = 3 V or 5 V for the 50 kΩ and 100 kΩ versions. 3VAB = VDD, Wiper (VW) = No Connect.

4INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0 V. DNL Specification limits of ±1 LSB maximum are Guaranteed Monotonic operating conditions. See TPC 28 test circuit.

5Resistor terminals A, B, W have no limitations on polarity with respect to each other.

6Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

7Measured at the Ax terminals. All Ax terminals are open circuited in shutdown mode.

8Worst-case supply current consumed when input logic level at 2.4 V, standard characteristic of CMOS logic. See TPC 20 for a plot of IDD versus logic voltage. 9PDISS is calculated from (IDD × VDD). CMOS logic level inputs result in minimum power dissipation.

10All Dynamic Characteristics use VDD = 5 V.

11Measured at a VW pin where an adjacent VW pin is making a full-scale voltage change. Specifications subject to change without notice.

REV. C |

–3– |

|

|

|

(VDD = 3 V 10% or 5 V 10%, VA = VDD, VB = 0 V, |

|||||

AD8400/AD8402/AD8403–SPECIFICATIONS –40 C ≤ TA ≤ +125 C unless otherwise noted.) |

||||||||

ELECTRICAL CHARACTERISTICS–1 k VERSION |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

Conditions |

Min |

Typ1 |

Max |

Unit |

|

DC CHARACTERISTICS RHEOSTAT MODE Specifications Apply to All VRs |

|

|

|

|

|

|||

Resistor Differential NL2 |

|

R-DNL |

RWB, VA = No Connect |

–5 |

–1 |

+3 |

LSB |

|

|

||||||||

Resistor Nonlinearity2 |

|

R-INL |

RWB, VA = No Connect |

–4 |

± 1.5 |

+4 |

LSB |

|

Nominal Resistance3 |

|

RAB |

TA = 25°C, Model: AD840XYY1 |

0.8 |

1.2 |

1.6 |

kΩ |

|

Resistance Tempco |

|

∆RAB/∆T |

VAB = VDD, Wiper = No Connect |

|

700 |

|

ppm/°C |

|

Wiper Resistance |

|

RW |

IW = 1 V/RAB |

|

53 |

100 |

Ω |

|

Nominal Resistance Match |

|

∆R/RAB |

CH 1 to 2, VAB = VDD, TA = 25°C |

|

0.75 |

2 |

% |

|

DC CHARACTERISTICS POTENTIOMETER DIVIDER Specifications Apply to All VRs |

|

|

|

|

|

|||

Resolution |

|

N |

|

8 |

± 2 |

|

Bits |

|

Integral Nonlinearity4 |

|

INL |

|

–6 |

+6 |

LSB |

||

Differential Nonlinearity4 |

|

DNL |

VDD = 5 V |

–4 |

–1.5 |

+2 |

LSB |

|

|

|

DNL |

VDD = 3 V, TA = 25°C |

–5 |

–2 |

+5 |

LSB |

|

Voltage Divider Temperature Coefficent |

|

∆VW/∆T |

Code = 80H |

|

25 |

|

ppm/°C |

|

Full-Scale Error |

|

VWFSE |

Code = FFH |

–20 |

–12 |

0 |

LSB |

|

Zero-Scale Error |

|

VWZSE |

Code = 00H |

0 |

6 |

10 |

LSB |

|

RESISTOR TERMINALS |

|

|

|

|

|

|

|

|

Voltage Range5 |

|

VA, B, W |

|

0 |

|

VDD |

V |

|

Capacitance6 Ax, Bx |

|

CA, B |

f = 1 MHz, Measured to GND, Code = 80H |

|

75 |

|

pF |

|

Capacitance6 Wx |

|

CW |

f = 1 MHz, Measured to GND, Code = 80H |

|

120 |

|

pF |

|

Shutdown Supply Current7 |

|

IA_SD |

VA = VDD, VB = 0 V, SHDN = 0 |

|

0.01 |

5 |

µA |

|

Shutdown Wiper Resistance |

|

RW_SD |

VA = VDD, VB = 0 V, SHDN = 0, VDD = 5 V |

|

50 |

100 |

Ω |

|

DIGITAL INPUTS AND OUTPUTS |

|

|

|

|

|

|

|

|

Input Logic High |

|

VIH |

VDD = 5 V |

2.4 |

|

|

V |

|

Input Logic Low |

|

VIL |

VDD = 5 V |

|

|

0.8 |

V |

|

Input Logic High |

|

VIH |

VDD = 3 V |

2.1 |

|

|

V |

|

Input Logic Low |

|

VIL |

VDD = 3 V |

|

|

0.6 |

V |

|

Output Logic High |

|

VOH |

RL = 2.2 kΩ to VDD |

VDD – 0.1 |

|

|

V |

|

Output Logic Low |

|

VOL |

IOL = 1.6 mA, VDD = 5 V |

|

|

0.4 |

V |

|

Input Current |

|

IIL |

VIN = 0 V or 5 V, VDD = 5 V |

|

|

± 1 |

µA |

|

Input Capacitance6 |

|

CIL |

|

|

5 |

|

pF |

|

POWER SUPPLIES |

|

|

|

|

|

|

|

|

Power Supply Range |

|

VDD Range |

|

2.7 |

|

5.5 |

V |

|

Supply Current (CMOS) |

|

IDD |

VIH = VDD or VIL = 0 V |

|

0.01 |

5 |

µA |

|

Supply Current (TTL)8 |

|

IDD |

VIH = 2.4 V or 0.8 V, VDD = 5.5 V |

|

0.9 |

4 |

mA |

|

Power Dissipation (CMOS)9 |

|

PDISS |

VIH = VDD or VIL = 0 V, VDD = 5.5 V |

|

|

27.5 |

µW |

|

Power Supply Sensitivity |

|

PSS |

∆VDD = 5 V ± 10% |

|

0.0035 |

0.008 |

%/% |

|

|

|

PSS |

∆VDD = 3 V ± 10% |

|

0.05 |

0.13 |

%/% |

|

DYNAMIC CHARACTERISTICS6, 10 |

|

|

R = 1 kΩ |

|

|

|

|

|

Bandwidth –3 dB |

|

BW_1K |

|

5,000 |

|

kHz |

||

Total Harmonic Distortion |

|

THDW |

VA = 1 V rms + 2 V dc, VB = 2 V dc, f = 1 kHz |

|

0.015 |

|

% |

|

VW Settling Time |

|

tS |

VA = VDD, VB = 0 V, ± 1% Error Band |

|

0.5 |

|

µs |

|

Resistor Noise Voltage |

|

eNWB |

RWB = 500 Ω, f = 1 kHz, RS = 0 |

|

3 |

|

nV/√Hz |

|

Crosstalk11 |

|

CT |

VA = VDD, VB = 0 V |

|

–65 |

|

dB |

|

NOTES

1Typicals represent average readings at 25°C and VDD = 5 V.

2Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. See TPC 29 test circuit.

IW = 500 µA for VDD = 3 V and IW = 2.5 mA for VDD = 5 V for 1 kΩ version. 3VAB = VDD, Wiper (VW) = No Connect.

4INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. VA = VDD and VB = 0 V. DNL Specification limits of ±1 LSB maximum are Guaranteed Monotonic operating conditions. See TPC 28 test circuit.

5Resistor terminals A, B, W have no limitations on polarity with respect to each other.

6Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

7Measured at the Ax terminals. All Ax terminals are open circuited in shutdown mode.

8Worst-case supply current consumed when input logic level at 2.4 V, standard characteristic of CMOS logic. See TPC 20 for a plot of IDD versus logic voltage. 9PDISS is calculated from (IDD × VDD). CMOS logic level inputs result in minimum power dissipation.

10All Dynamic Characteristics use VDD = 5 V.

11Measured at a VW pin where an adjacent VW pin is making a full-scale voltage change. Specifications subject to change without notice.

–4– |

REV. C |

AD8400/AD8402/AD8403

SPECIFICATIONS (VDD = 3 V 10% or 5 V 10%, VA = VDD, VB = 0 V, –40 C ≤ TA ≤ +125 C unless otherwise noted.)

ELECTRICAL CHARACTERISTICS–ALL VERSIONS

Parameter |

Symbol |

Conditions |

Min |

Typ1 |

Max |

Unit |

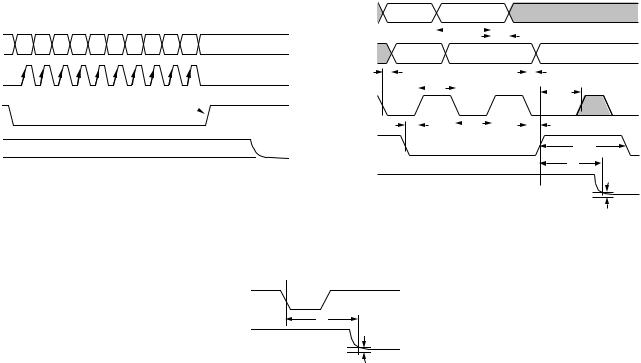

SWITCHING CHARACTERISTICS2, 3 |

|

|

|

|

|

|

Input Clock Pulsewidth |

tCH, tCL |

Clock Level High or Low |

10 |

|

|

ns |

Data Setup Time |

tDS |

|

5 |

|

|

ns |

Data Hold Time |

tDH |

RL = 1 kΩ to 5 V, CL ≤ 20 pF |

5 |

|

|

ns |

CLK to SDO Propagation Delay4 |

tPD |

1 |

|

25 |

ns |

|

CS Setup Time |

tCSS |

|

10 |

|

|

ns |

CS High Pulsewidth |

tCSW |

|

10 |

|

|

ns |

Reset Pulsewidth |

tRS |

|

50 |

|

|

ns |

CLK Fall to CS Rise Hold Time |

tCSH |

|

0 |

|

|

ns |

CS Rise to Clock Rise Setup |

tCS1 |

|

10 |

|

|

ns |

NOTES

1Typicals represent average readings at 25°C and VDD = 5 V.

2Guaranteed by design and not subject to production test. Resistor-terminal capacitance tests are measured with 2.5 V bias on the measured terminal. The remaining resistor terminals are left open circuit.

3See timing diagram for location of measured values. All input control voltages are specified with tR = tF = 1 ns (10% to 90% of VDD) and timed from a voltage level of 1.6 V. Switching characteristics are measured using VDD = 3 V or 5 V. To avoid false clocking, a minimum input logic slew rate of 1 V/ s should be maintained. 4Propagation Delay depends on value of VDD, RL, and CL—see Applications section.

Specifications subject to change without notice.

|

1 |

|

|

|

|

|

|

|

|

|

SDI |

A1 |

A0 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

0

1

CLK

0

DAC REGISTER LOAD 1

CS

0

VDD

VOUT

0V

1

SDI

(DATA IN)

0

SDO 1

(DATA OUT)

0

1

CLK

0

1

CS

0

VDD

VOUT0V

Ax OR Dx |

|

|

|

Ax OR Dx |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDS |

|

|

|

|

tDH |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

A'x OR D'x |

A'x OR D'x |

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

tPD_MIN |

|

|

|

|

|

|

|

|

|

|

|

|

tPD_MAX |

|||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

tCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCS1 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

tCL |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

tCSS |

|

|

|

|

|

|

|

|

|

t |

CSH |

|||||||||

tCSW

tS

1 %

1% ERROR BAND

Figure 2a. Timing Diagram |

Figure 2b. Detail Timing Diagram |

1

RS

0

VDD

VOUT

VDD/2

tRS

tRS

tS

1%

1% ERROR BAND

Figure 2c. Reset Timing Diagram

REV. C |

–5– |

AD8400/AD8402/AD8403

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C, unless otherwise noted.) |

|

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . –0.3 V, +8 V |

VA, VB, VW to GND . . . . . . . . . . . . . . . . . . . . |

. . . . . . 0 V, VDD |

AX – BX, AX – WX, BX – WX . . . . . . . . . . . . . . |

. . . . . . . ± 20 mA |

Digital Input and Output Voltage to GND . . |

. . . . . . 0 V, 7 V |

Operating Temperature Range . . . . . . . . . . |

–40°C to +125°C |

Maximum Junction Temperature (TJ max) . . |

. . . . . . . . 150°C |

Storage Temperature . . . . . . . . . . . . . . . . . . |

–65°C to +150°C |

Lead Temperature (Soldering, 10 sec) . . . . . |

. . . . . . . . 300°C |

Package Power Dissipation . . . . . . . . . . . . . |

(TJ max – TA)/θJA |

Thermal Resistance (θJA) |

103°C/W |

P-DIP (N-8) . . . . . . . . . . . . . . . . . . . . . . . |

|

SOIC (SO-8) . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . 158°C/W |

P-DIP (N-14) . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 83°C/W |

P-DIP (N-24) . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 63°C/W |

SOIC (SO-14) . . . . . . . . . . . . . . . . . . . . . . |

. . . . . 120°C/W |

SOIC (SOL-24) . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 70°C/W |

TSSOP-14 (RU-14) . . . . . . . . . . . . . . . . . . |

. . . . . 180°C/W |

TSSOP-24 (RU-24) . . . . . . . . . . . . . . . . . . |

. . . . . 143°C/W |

*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table I. Serial Data Word Format

ADDR |

|

|

|

|

DATA |

|

|

|

|

B9 |

B8 |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

B0 |

|

|

|

|

|

|

|

|

|

|

A1 |

A0 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

MSB |

LSB |

MSB |

|

|

|

|

|

|

LSB |

29 |

28 |

27 |

|

|

|

|

|

|

20 |

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8400/AD8402/AD8403 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–6– |

REV. C |

Loading...

Loading...