Analog Devices AD7718EB, AD7708EB, AD7718BRU, AD7708BRU, AD7708BR Datasheet

a |

8-/10-Channel, Low Voltage, |

|

Low Power, - ADCs |

||

|

|

|

|

|

AD7708/AD7718 |

|

|

|

|

FEATURES |

GENERAL DESCRIPTION |

|

8-/10-Channel, High Resolution - ADCs |

The AD7708/AD7718 are complete analog front-ends for low |

|

AD7708 Has 16-Bit Resolution |

frequency measurement applications. The AD7718 contains a |

|

AD7718 Has 24-Bit Resolution |

24-bit Σ-∆ ADC with PGA and can be configured as 4/5 fully- |

|

Factory-Calibrated |

differential input channels or 8/10 pseudo-differential input |

|

Single Conversion Cycle Setting |

channels. Two pins on the device are configurable as analog |

|

Programmable Gain Front End |

inputs or reference inputs. The AD7708 is a 16-bit version of |

|

Simultaneous 50 Hz and 60 Hz Rejection |

the AD7718. Input signal ranges from 20 mV to 2.56 V can be |

|

VREF Select™ Allows Absolute and Ratiometric |

directly converted using these ADCs. Signals can be converted |

|

Measurement Capability |

directly from a transducer without the need for signal conditioning. |

|

Operation Can Be Optimized for |

The device operates from a 32 kHz crystal with an on-board PLL |

|

Analog Performance (CHOP = 0) or |

|

|

generating the required internal operating frequency. The output |

|

|

Channel Throughput (CHOP = 1) |

|

|

data rate from the part is software programmable. The peak-to- |

|

|

|

|

|

INTERFACE |

peak resolution from the part varies with the programmed gain |

|

3-Wire Serial |

and output data rate. |

|

SPITM, QSPITM, MICROWIRETM, and DSP-Compatible |

The part operates from a single 3 V or 5 V supply. When operating |

|

Schmitt Trigger on SCLK |

|

|

from 3 V supplies, the power dissipation for the part is 3.84 mW typ. |

|

|

|

|

|

POWER |

Both parts are pin-for-pin compatible allowing an upgradable |

|

Specified for Single 3 V and 5 V Operation |

path from 16 to 24 bits without the need for hardware modifica- |

|

Normal: 1.28 mA Typ @ 3 V |

tions. The AD7708/AD7718 are housed in 28-lead SOIC and |

|

Power-Down: 30 A (32 kHz Crystal Running) |

TSSOP packages. |

|

On-Chip Functions |

|

|

Rail-to-Rail Input Buffer and PGA |

|

|

2-Bit Digital I/O Port |

|

APPLICATIONS

Industrial Process Control

Instrumentation

Pressure Transducers

Portable Instrumentation

Smart Transmitters

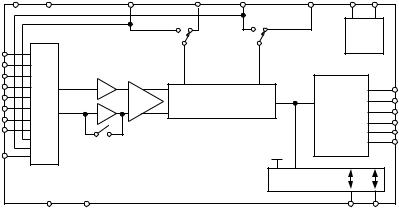

FUNCTIONAL BLOCK DIAGRAM

DVDD |

DGND |

|

REFIN2(+)/AIN9 |

REFIN1(+) |

REFIN2(–)/AIN10 |

REFIN1(–) XTAL1 XTAL2 |

||

|

|

|

|

|

|

|

OSC |

|

|

|

|

|

|

|

|

AND |

|

|

|

|

|

|

|

|

PLL |

|

AIN1 |

|

|

|

|

|

|

|

|

AIN2 |

|

|

POS BUF |

|

|

|

|

|

AIN3 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

AIN4 |

|

|

|

|

REFIN(+) |

REFIN(–) |

|

DOUT |

AIN5 |

|

|

|

|

SERIAL |

|||

MUX |

NEG BUF |

PGA |

- ADC* |

DIN |

||||

AIN6 |

INTERFACE |

SCLK |

||||||

|

|

|

|

|

|

AND |

||

AIN7 |

|

|

|

|

*AD7708 16-BIT ADC |

CS |

||

|

|

|

|

CONTROL |

||||

AIN8 |

|

|

|

|

RDY |

|||

|

|

|

|

*AD7718 24-BIT ADC |

LOGIC |

|||

|

|

|

|

|

|

|

|

RESET |

AINCOM |

|

|

|

|

|

AVDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7708/AD7718 |

|

|

I/O PORT |

|

|

|

AVDD |

|

AGND |

|

|

|

P2 |

P1 |

SPI and QSPI are trademarks of Motorola Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

VREF Select is a trademark of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 2001 |

AD7708/AD7718

TABLE OF CONTENTS

FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 FUNCTIONAL BLOCK DIAGRAM . . . . . . . . . . . . . . . . . 1 GENERAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . 1 AD7718 SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . 3 AD7708 SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . 6 TIMING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . 9 ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . 10 ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 PIN FUNCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . 12 PIN CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . . . 13 ADC CIRCUIT INFORMATION . . . . . . . . . . . . . . . . . . . 15

Signal Chain Overview (CHOP Enabled, CHOP = 0) . . . 15

ADC NOISE PERFORMANCE CHOP ENABLED

(CHOP = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Signal Chain Overview (CHOP Disabled CHOP = 1) . . . 19

ADC NOISE PERFORMANCE CHOP DISABLED

(CHOP = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

ON-CHIP REGISTERS . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Communications Register . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Mode Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Operating Characteristics when Addressing the

Mode and Control Registers . . . . . . . . . . . . . . . . . . . . . . . 28 ADC Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Filter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 I/O Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 ADC Data Result Register . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Unipolar Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Bipolar Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 ADC Offset Calibration Coefficient Registers . . . . . . . . . . . 31 ADC Gain Calibration Coefficient Register . . . . . . . . . . . . . 31 ID Register (ID) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

User Nonprogrammable Test Registers . . . . . . . . . . . . . . . . 31

Configuring the AD7708/AD7718 . . . . . . . . . . . . . . . . . . . . 32

DIGITAL INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

MICROCOMPUTER/MICROPROCESSOR INTERFACING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

AD7708/AD7718 to 68HC11 Interface . . . . . . . . . . . . . . . . 34 AD7708/AD7718-to-8051 Interface . . . . . . . . . . . . . . . . . . 35 AD7708/AD7718-to-ADSP-2103/ADSP-2105 Interface . . . 36 BASIC CONFIGURATION . . . . . . . . . . . . . . . . . . . . . . . . 36 Analog Input Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Single-Ended Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Chop Mode of Operation (CHOP = 0) . . . . . . . . . . . . . . . . 37 Nonchop Mode of Operation (CHOP = 1) . . . . . . . . . . . . . 38 Programmable Gain Amplifier . . . . . . . . . . . . . . . . . . . . . . . 38 Bipolar/Unipolar Configuration . . . . . . . . . . . . . . . . . . . . . . 38 Data Output Coding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Oscillator Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Reference Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 RESET Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Power-Down Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 Grounding and Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 APPLICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Data Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Programmable Logic Controllers . . . . . . . . . . . . . . . . . . . . . 41 Converting Single-Ended Inputs. . . . . . . . . . . . . . . . . . . . . 42

Combined Ratiometric and Absolute Value

Measurement System . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Optimizing Throughput while Maximizing 50 Hz and 60 Hz Rejection in a Multiplexed Data

Acquisition System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . 44

–2– |

REV. 0 |

AD7708/AD7718

AD7718 SPECIFICATIONS1 (AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V; REFIN(–) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz Crystal Input Buffer Enabled. All specifications TMIN to TMAX unless otherwise noted.)

Parameter |

B Grade |

Unit |

Test Conditions |

|

|

|

|

AD7718 (CHOP DISABLED) |

|

|

|

Output Update Rate |

16.06 |

Hz min |

CHOP = 1 |

No Missing Codes2 |

1.365 |

kHz max |

|

24 |

Bits min |

± 20 mV Range, SF = 69 |

|

Resolution |

13 |

Bits p-p |

|

|

18 |

Bits p-p |

± 2.56 V Range, SF = 69 |

Output Noise and Update Rates |

See Tables in |

|

|

|

ADC Description |

|

|

Integral Nonlinearity |

± 10 |

ppm of FSR max |

2 ppm Typical |

Offset Error3 |

Table VII |

µV typ |

Offset Error is in the order of the noise for the |

|

|

|

programmed gain and update rate following a |

Offset Error Drift vs. Temp4 |

± 200 |

nV/°C typ |

calibration |

|

|||

Full-Scale Error3 |

± 10 |

µV typ |

|

Gain Drift vs. Temp4 |

± 0.5 |

ppm/°C typ |

|

Negative Full-Scale Error |

± 0.003 |

% FSR max |

|

|

|

|

|

ANALOG INPUTS |

± 1.024 × REFIN/GAIN |

|

|

Differential Input Full-Scale Voltage |

V nom |

REFIN Refers to Both REFIN1 and |

|

|

|

|

REFIN2. REFIN = REFIN(+) –REFIN(–) |

|

|

|

GAIN = 1 to 128 |

Absolute AIN Voltage Limits |

AGND + 100 mV |

V min |

AIN1–AIN10 and AINCOM with |

|

AVDD – 100 mV |

V max |

NEGBUF = 1 |

Absolute AINCOM Voltage Limits |

AGND – 30 mV |

V min |

NEGBUF = 0 |

Analog Input Current |

AVDD + 30 mV |

V max |

AIN1–AIN10 and AINCOM with NEGBUF = 1 |

± 1 |

|

||

DC Input Current2 |

nA max |

|

|

DC Bias Current Drift |

± 5 |

pA/°C typ |

|

AINCOM Input Current |

|

|

NEGBUF = 0 |

DC Input Current2 |

± 125 |

nA/V typ |

± 2.56 V Range |

DC Bias Current Drift |

± 2 |

pA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

dB min |

|

@ 60 Hz |

100 |

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection |

|

|

|

@ DC |

90 |

dB min |

100 dB typ, Analog Input = 1 V, |

|

|

|

Input Range = ± 2.56 V |

|

|

|

110 dB typ on ± 20 mV Range |

@ 50 Hz |

100 |

dB typ |

50 Hz ± 1 Hz, SF Word = 82 |

@ 60 Hz |

100 |

dB typ |

60 Hz ± 1 Hz, SF Word = 68 |

|

|

|

|

REFERENCE INPUTS (REFIN1 AND REFIN2) |

|

|

|

REFIN(+) to REFIN(–) Voltage |

2.5 |

V nom |

REFIN Refers to Both REFIN1 and REFIN2 |

REFIN(+) to REFIN(–) Range2 |

1 |

V min |

|

|

AVDD |

V max |

|

REFIN Common-Mode Range |

AGND – 30 mV |

V min |

|

|

AVDD + 30 mV |

V max |

|

Reference DC Input Current |

0.5 |

µA/V typ |

|

Reference DC Input Current Drift |

± 0.1 |

nA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

dB min |

|

@ 60 Hz |

100 |

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection |

|

|

Input Range = ± 2.56 V |

@ DC |

100 |

dB typ |

Analog Input = 1 V. Input Range = ± 2.56 V |

@ 50 Hz |

100 |

dB typ |

|

@ 60 Hz |

100 |

dB typ |

|

|

|

|

|

REV. 0 |

–3– |

AD7718–SPECIFICATIONS1 (AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.7 V to 3.6 2.5 V ; REFIN(–) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz Crystal Input Buffer Enabled. All specifications TMIN

V or 4.75 V to 5.25 V, REFIN(+) = to TMAX unless otherwise noted.)

Parameter |

B Grade |

Unit |

Test Conditions |

|

|

|

|

AD7718 (CHOP ENABLED) |

|

|

|

Output Update Rate |

5.4 |

Hz min |

CHOP = 0 |

No Missing Codes2 |

105 |

Hz max |

|

24 |

Bits min |

20 Hz Update Rate |

|

Resolution |

13 |

Bits p-p |

± 20 mV Range, 20 Hz Update Rate |

|

18 |

Bits p-p |

± 2.56 V Range, 20 Hz Update Rate |

Output Noise and Update Rates |

See Tables in |

|

|

|

ADC Description |

|

|

Integral Nonlinearity |

± 10 |

ppm of FSR max |

2 ppm Typical |

Offset Error3 |

± 3 |

µV typ |

|

Offset Error Drift vs. Temp4 |

10 |

nV/°C typ |

|

Full-Scale Error3 |

± 10 |

µV/°C typ |

|

Gain Drift vs. Temp4 |

± 0.5 |

ppm/°C typ |

|

ANALOG INPUTS |

±1.024 × REFIN/GAIN |

|

|

Differential Input Full-Scale Voltage |

V nom |

REFIN Refers to Both REFIN1 and |

|

|

|

|

REFIN2. REFIN = REFIN(+) REFIN(–) |

|

± 2 |

µV typ |

GAIN = 1 to 128 |

Range Matching |

Analog Input = 18 mV |

||

Absolute AIN Voltage Limits |

AGND + 100 mV |

V min |

AIN1–AIN10 and AINCOM with |

|

AVDD – 100 mV |

V max |

NEGBUF = 1 |

Absolute AINCOM Voltage Limits |

AGND – 30 mV |

V min |

NEGBUF = 0 |

Analog Input Current |

AVDD + 30 mV |

V max |

AIN1–AIN10 and AINCOM with |

|

|

||

DC Input Current2 |

± 1 |

|

NEGBUF = 1 |

nA max |

|

||

DC Input Current Drift |

± 5 |

pA/°C typ |

|

AINCOM Input Current |

|

|

NEGBUF = 0 |

DC Input Current2 |

± 125 |

nA/V typ |

± 2.56 V Range |

DC Bias Current Drift |

± 2 |

pA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

dB min |

|

@ 60 Hz |

100 |

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection |

|

|

|

@ DC |

90 |

dB min |

100 dB typ, Analog Input = 1 V, |

|

|

|

Input Range = ±2.56 V |

|

|

|

110 dB typ on ± 20 mV Range |

@ 50 Hz2 |

100 |

dB min |

50 Hz ± 1 Hz, 20 Hz Update Rate |

@ 60 Hz2 |

100 |

dB min |

60 Hz ± 1 Hz, 20 Hz Update Rate |

REFERENCE INPUTS (REFIN1 AND REFIN2) |

|

|

|

REFIN(+) to REFIN(–) Voltage |

2.5 |

V nom |

REFIN Refers to Both REFIN1 and |

REFIN(+) to REFIN(–) Range2 |

|

|

REFIN2 |

1 |

V min |

|

|

|

AVDD |

V max |

|

REFIN Common-Mode Range |

AGND – 30 mV |

V min |

|

|

AVDD + 30 mV |

V max |

|

Reference DC Input Current2 |

± 0.5 |

µA/V typ |

|

Reference DC Input Current Drift |

± 0.01 |

nA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

dB min |

|

@ 60 Hz |

100 |

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection2 |

|

|

Input Range = ± 2.56 V |

@ DC |

110 |

dB typ |

Analog Input = 1 V |

@ 50 Hz |

110 |

dB typ |

50 Hz ± 1 Hz, 20 Hz Update Rate |

@ 60 Hz |

110 |

dB typ |

60 Hz ± 1 Hz, 20 Hz Update Rate |

|

|

|

|

LOGIC INPUTS5 |

|

|

|

All Inputs Except SCLK and XTAL12 |

|

|

|

VINL, Input Low Voltage |

0.8 |

V max |

DVDD = 5 V |

VINL, Input Low Voltage |

0.4 |

V max |

DVDD = 3 V |

VINH, Input High Voltage |

2.0 |

V min |

DVDD = 3 V or 5 V |

–4– |

REV. 0 |

|

|

|

|

|

AD7708/AD7718 |

|

|

|

|

|

|

Parameter |

B Grade |

Unit |

|

Test Conditions |

|

|

|

|

|

|

|

LOGIC INPUTS (Continued) |

|

|

|

|

|

SCLK Only (Schmitt-Triggered Input)2 |

|

|

|

|

|

VT(+) |

1.4/2 |

|

V min/V max |

|

DVDD = 5 V |

VT(–) |

0.8/1.4 |

|

V min/V max |

|

DVDD = 5 V |

VT(+) – VT(–) |

0.3/0.85 |

|

V min/V max |

|

DVDD = 5 V |

VT(+) |

0.95/2 |

|

V min/V max |

|

DVDD = 3 V |

VT(–) |

0.4/1.1 |

|

V min/V max |

|

DVDD = 3 V |

VT(+)–VT(–) |

0.3/0.85 |

|

V min/V max |

|

DVDD = 3 V |

XTAL1 Only2 |

|

|

|

|

|

VINL, Input Low Voltage |

0.8 |

|

V max |

|

DVDD = 5 V |

VINH, Input High Voltage |

3.5 |

|

V min |

|

DVDD = 5 V |

VINL, Input Low Voltage |

0.4 |

|

V max |

|

DVDD = 3 V |

VINH, Input High Voltage |

2.5 |

|

V min |

|

DVDD = 3 V |

Input Currents |

± 10 |

|

µA max |

|

Logic Input = DVDD |

|

–70 |

µA max |

|

Logic Input = DGND, Typical –40 µA @ 5 V |

|

|

|

|

|

|

and –20 µA at 3 V |

Input Capacitance |

10 |

|

pF typ |

|

All Digital Inputs |

|

|

|

|

|

|

LOGIC OUTPUTS (Excluding XTAL2)5 |

|

|

|

|

DVDD = 3 V, ISOURCE = 100 µA |

VOH, Output High Voltage2 |

DVDD – 0.6 |

V min |

|

||

VOL, Output Low Voltage2 |

0.4 |

|

V max |

|

DVDD = 3 V, ISINK = 100 µA |

VOH, Output High Voltage2 |

4 |

|

V min |

|

DVDD = 5 V, ISOURCE = 200 µA |

VOL, Output Low Voltage2 |

0.4 |

|

V max |

|

DVDD = 5 V, ISINK = 1.6 mA |

Floating State Leakage Current |

± 10 |

|

µA max |

|

|

Floating State Output Capacitance |

± 10 |

|

pF typ |

|

|

Data Output Coding |

Binary |

|

|

Unipolar Mode |

|

|

Offset Binary |

|

|

Bipolar Mode |

|

|

|

|

|

|

|

SYSTEM CALIBRATION2 |

1.05 × FS |

|

|

|

|

Full-Scale Calibration Limit |

V max |

|

|

||

Zero-Scale Calibration Limit |

–1.05 × FS |

V min |

|

|

|

Input Span |

0.8 × FS |

V min |

|

|

|

|

2.1 × FS |

V max |

|

|

|

|

|

|

|

|

|

START-UP TIME |

|

|

|

|

|

From Power-On |

300 |

|

ms typ |

|

|

From Power-Down Mode |

1 |

|

ms typ |

|

Oscillator Enabled |

|

300 |

|

ms typ |

|

Oscillator Powered Down |

|

|

|

|

|

|

POWER REQUIREMENTS |

|

|

|

|

|

Power Supply Voltages |

AVDD and DVDD can be operated independently of each other. |

||||

AVDD–AGND |

2.7/3.6 |

|

V min/max |

|

AVDD = 3 V nom |

|

|||||

|

|

||||

|

4.75/5.25 |

|

V min/max |

|

AVDD = 5 V nom |

DVDD–DGND |

2.7/3.6 |

|

V min/max |

|

DVDD = 3 V nom |

|

4.75/5.25 |

|

V min |

|

DVDD = 5 V nom |

DIDD (Normal Mode) |

0.55 |

|

mA max |

|

DVDD = 3 V, 0.43 mA typ |

|

0.65 |

|

mA max |

|

DVDD = 5 V, 0.5 mA typ |

AIDD (Normal Mode) |

1.1 |

|

mA max |

|

AVDD = 3 V or 5 V, 0.85 mA typ |

DIDD (Power-Down Mode) |

10 |

|

µA max |

|

DVDD = 3 V, 32.768 kHz Osc. Running |

|

2 |

|

µA max |

|

DVDD = 3 V, Oscillator Powered Down |

|

30 |

|

µA max |

|

DVDD = 5 V, 32.768 kHz Osc. Running |

|

8 |

|

µA max |

|

DVDD = 5 V, Oscillator Powered Down |

AIDD (Power-Down Mode) |

1 |

|

µA max |

|

AVDD = 3 V or 5 V |

Power Supply Rejection (PSR) |

|

|

|

|

Input Range = ± 2.56 V, AIN = 1 V |

Chop Disabled |

70 |

|

dB min |

|

95 dB typ |

Chop Enabled |

100 |

|

dB typ |

|

|

|

|

|

|

|

|

NOTES

1Temperature range is –40°C to +85°C.

2Not production tested, guaranteed by design and/or characterization data at release.

3Following a self-calibration this error will be in the order of the noise for the programmed gain and update selected. A system calibration will completely remove this error. 4Recalibration at any temperature will remove these errors.

5I/O Port Logic Levels are with respect to AVDD and AGND. Specifications are subject to change without notice.

REV. 0 |

–5– |

AD7708/AD7718

AD7708 SPECIFICATIONS1 (AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V; REFIN(–) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz Crystal Input Buffers Enabled. All specifications TMIN to TMAX unless otherwise noted.)

Parameter |

B Grade |

Unit |

Test Conditions |

|

|

|

|

|

|

AD7708 (CHOP DISABLED) |

|

|

|

|

Output Update Rate |

16.06 |

|

Hz min |

CHOP = 1 |

No Missing Codes2 |

1.365 |

|

kHz max |

|

16 |

|

Bits min |

± 20 mV Range, SF Word = 69 |

|

Resolution |

13 |

|

Bits p-p |

|

|

16 |

|

Bits p-p |

± 2.56 V Range, SF Word = 69 |

|

|

|

||

Output Noise and Update Rates |

See Tables in ADC |

Description |

|

|

Integral Nonlinearity |

± 15 |

|

ppm of FSR max |

2ppm Typical |

|

||||

Offset Error3 |

± 0.65 |

|

LSB typ |

Following a Self-Calibration |

Offset Error Drift vs. Temp4 |

± 200 |

|

nV/°C typ |

|

Full-Scale Error3 |

± 0.75 |

|

LSB typ |

|

Gain Drift vs. Temp4 |

± 0.5 |

|

ppm/°C typ |

|

Negative Full-Scale Error |

± 0.003 |

|

% FSR typ |

|

|

|

|

|

|

ANALOG INPUTS |

±1.024 × REFIN/GAIN |

|

|

|

Differential Input Full-Scale Voltage |

V nom |

REFIN Refers to Both REFIN1 and |

||

|

|

|

|

REFIN2. REFIN = REFIN(+) – REFIN(–) |

|

|

|

|

GAIN = 1 to 128 |

Absolute AIN Voltage Limits |

AGND + 100 mV |

V min |

AIN1–AIN10 and AINCOM with |

|

|

AVDD – 100 mV |

V max |

NEGBUF = 1 |

|

Absolute AINCOM Voltage Limits |

AGND – 30 mV |

V min |

NEGBUF = 0 |

|

Analog Input Current |

AVDD + 30 mV |

V max |

AIN1–AIN10 and AINCOM with |

|

|

|

|

||

DC Input Current2 |

± 1 |

|

|

NEGBUF = 1 |

|

nA max |

|

||

DC Bias Current Drift |

± 5 |

|

pA/°C typ |

|

AINCOM Input Current |

|

|

|

NEGBUF = 0 |

DC Input Current2 |

± 125 |

|

nA/V typ |

± 2.56 V Range |

DC Bias Current Drift |

± 2 |

|

pA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

|

dB min |

|

@ 60 Hz |

100 |

|

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection |

|

|

|

|

@ DC |

90 |

|

dB min |

100 dB typ, Analog Input = 1 V, |

|

|

|

|

Input Range = ± 2.56 V |

|

|

|

|

110 dB typ on ± 20 mV Range |

@ 50 Hz |

100 |

|

dB typ |

50 Hz ± 1 Hz, SF Word = 82 |

@ 60 Hz |

100 |

|

dB typ |

60 Hz ± 1 Hz, SF Word = 68 |

|

|

|

|

|

REFERENCE INPUTS (REFIN1 AND REFIN2) |

|

|

|

|

REFIN(+) to REFIN(–) Voltage |

2.5 |

|

V nom |

REFIN Refers to Both REFIN1 and |

REFIN(+) to REFIN(–) Range2 |

|

|

|

REFIN2 |

1 |

|

V min |

|

|

|

AVDD |

V max |

|

|

REFIN Common-Mode Range |

AGND – 30 mV |

V min |

|

|

|

AVDD + 30 mV |

V max |

|

|

Reference DC Input Current |

0.5 |

|

µA/V typ |

|

Reference DC Input Current Drift |

± 0.1 |

|

nA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

|

dB min |

|

@ 60 Hz |

100 |

|

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection |

|

|

|

Input Range = ± 2.56 V |

@ DC |

100 |

|

dB typ |

Analog Input = 1 V. Input Range = ±2.56 V |

@ 50 Hz |

100 |

|

dB typ |

|

@ 60 Hz |

100 |

|

dB typ |

|

|

|

|

|

|

–6– |

REV. 0 |

|

|

|

AD7708/AD7718 |

|

|

|

|

Parameter |

B Grade |

Unit |

Test Conditions |

|

|

|

|

AD7708 (CHOP ENABLED) |

|

|

|

Output Update Rate |

5.4 |

Hz min |

CHOP = 1 |

No Missing Codes2 |

105 |

Hz max |

0.732 ms Increments |

16 |

Bits min |

20 Hz Update Rate |

|

Resolution |

13 |

Bits p-p |

± 20 mV Range, 20 Hz Update Rate |

|

16 |

Bits p-p |

± 2.56 V Range, 20 Hz Update Rate |

Output Noise and Update Rates |

See Tables in |

|

|

|

ADC Description |

|

|

Integral Nonlinearity |

± 15 |

ppm of FSR max |

2 ppm Typical |

Offset Error3 |

± 3 |

µV typ |

Calibration is Accurate to ± 0.5 LSB |

Offset Error Drift vs. Temp4 |

10 |

nV/°C typ |

|

Full-Scale Error3 |

± 0.75 |

LSB typ |

Includes Positive and Negative ERRORS |

Gain Drift vs. Temp4 |

± 0.5 |

ppm/°C typ |

|

ANALOG INPUTS |

±1.024 × REFIN/GAIN |

|

|

Differential Input Full-Scale Voltage |

V nom |

REFIN Refers to Both REFIN1 and |

|

|

|

|

REFIN2. REFIN = REFIN(+) REFIN(–) |

|

± 2 |

µV typ |

GAIN = 1 to 128 |

Range Matching |

Analog Input = 18 mV |

||

Absolute AIN Voltage Limits |

AGND + 100 mV |

V min |

AIN1–AIN10 and AINCOM with |

|

AVDD – 100 mV |

V max |

NEGBUF = 1 |

Absolute AINCOM Voltage Limits |

AGND – 30 mV |

V min |

NEGBUF = 0 |

Analog Input Current |

AVDD + 30 mV |

V max |

AIN1–AIN10 and AINCOM with |

|

|

||

DC Input Current2 |

± 1 |

|

NEGBUF = 1 |

nA max |

|

||

DC Input Current Drift |

± 5 |

pA/°C typ |

|

AINCOM Input Current |

± 125 |

|

NEGBUF = 0 |

DC Input Current2 |

nA/V typ |

|

|

DC Bias Current Drift |

± 2 |

pA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

dB min |

|

@ 60 Hz |

94 |

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection |

|

|

|

@ DC |

90 |

dB min |

100 dB typ, Analog Input = 1 V, |

|

|

|

Input Range = ±2.56 V |

|

|

|

110 dB typ on ± 20 mV Range |

@ 50 Hz2 |

100 |

dB min |

50 Hz ± 1 Hz, 20 Hz Update Rate |

@ 60 Hz2 |

100 |

dB min |

60 Hz ± 1 Hz, 20 Hz Update Rate |

REFERENCE INPUTS (REFIN1 AND REFIN2) |

|

|

|

REFIN(+) to REFIN(–) Voltage |

2.5 V |

nom |

REFIN Refers to Both REFIN1 and |

REFIN(+) to REFIN(–) Range2 |

|

|

REFIN2 |

1 |

V min |

|

|

|

AVDD |

V max |

|

REFIN Common-Mode Range |

AGND – 30 mV |

V min |

|

|

AVDD + 30 mV |

V max |

|

Reference DC Input Current2 |

± 0.5 |

µA/V typ |

|

Reference DC Input Current Drift |

± 0.01 |

nA/V/°C typ |

|

Normal-Mode Rejection2 |

|

|

50 Hz ± 1 Hz, SF Word = 82 |

@ 50 Hz |

100 |

dB min |

|

@ 60 Hz |

100 |

dB min |

60 Hz ± 1 Hz, SF Word = 68 |

Common-Mode Rejection |

|

|

Input Range = ± 2.56 V |

@ DC |

110 |

dB typ |

Analog Input = 1 V |

@ 50 Hz |

110 |

dB typ |

50 Hz ± 1 Hz, 20 Hz Update Rate |

@ 60 Hz |

110 |

dB typ |

60 Hz ± 1 Hz, 20 Hz Update Rate |

|

|

|

|

LOGIC INPUTS5 |

|

|

|

All Inputs Except SCLK and XTAL12 |

|

|

|

VINL, Input Low Voltage |

0.8 |

V max |

DVDD = 5 V |

|

0.4 |

V max |

DVDD = 3 V |

VINH, Input High Voltage |

2.0 |

V min |

DVDD = 3 V or 5 V |

REV. 0 |

–7– |

AD77018–SPECIFICATIONS1 (AVDD = 2.7 V to 3.6 V or 4.75 V to 5.25 V, DVDD = 2.7 V to 3.6 2.5 V ; REFIN(–) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz Crystal Input Buffer Enabled. All specifications TMIN

V or 4.75 V to 5.25 V, REFIN(+) = to TMAX unless otherwise noted.)

Parameter |

B Grade |

Unit |

|

Test Conditions |

|

|

|

|

|

|

|

LOGIC INPUTS (Continued) |

|

|

|

|

|

SCLK Only (Schmitt-Triggered Input)2 |

|

|

|

|

|

VT(+) |

1.4/2 |

V min/V max |

|

DVDD = 5 V |

|

VT(–) |

0.8/1.4 |

V min/V max |

|

DVDD = 5 V |

|

VT(+)–VT(–) |

0.3/0.85 |

V min/V max |

|

DVDD = 5 V |

|

VT(+) |

0.95/2 |

V min/V max |

|

DVDD = 3 V |

|

VT(–) |

0.4/1.1 |

V min/V max |

|

DVDD = 3 V |

|

VT(+)–VT(–) |

0.3/0.85 |

V min/V max |

|

DVDD = 3 V |

|

XTAL1 Only2 |

|

|

|

|

|

VINL, Input Low Voltage |

0.8 |

V max |

|

DVDD = 5 V |

|

VINH, Input High Voltage |

3.5 |

V min |

|

DVDD = 5 V |

|

VINL, Input Low Voltage |

0.4 |

V max |

|

DVDD = 3 V |

|

VINH, Input High Voltage |

2.5 |

V min |

|

DVDD = 3 V |

|

Input Currents |

± 10 |

µA max |

|

Logic Input = DVDD |

|

|

–70 |

µA max |

|

Logic Input = DGND, Typical –40 µA @ 5 V |

|

|

|

|

|

|

and –20 µA at 3 V |

Input Capacitance |

10 |

pF typ |

|

All Digital Inputs |

|

|

|

|

|

|

|

LOGIC OUTPUTS (Excluding XTAL2)5 |

|

|

|

|

DVDD = 3 V, ISOURCE = 100 µA |

VOH, Output High Voltage2 |

DVDD – 0.6 |

V min |

|

||

VOL, Output Low Voltage2 |

0.4 |

V max |

|

DVDD = 3 V, ISINK = 100 µA |

|

VOH, Output High Voltage2 |

4 |

V min |

|

DVDD = 5 V, ISOURCE = 200 µA |

|

VOL, Output Low Voltage2 |

0.4 |

V max |

|

DVDD = 5 V, ISINK = 1.6 mA |

|

Floating State Leakage Current |

± 10 |

µA max |

|

|

|

Floating State Output Capacitance |

± 10 |

pF typ |

|

|

|

Data Output Coding |

Binary |

|

|

|

Unipolar Mode |

|

Offset Binary |

|

|

|

Bipolar Mode |

|

|

|

|

|

|

SYSTEM CALIBRATION2 |

1.05 × FS |

|

|

|

|

Full-Scale Calibration Limit |

V max |

|

|

||

Zero-Scale Calibration Limit |

–1.05 × FS |

V min |

|

|

|

Input Span |

0.8 × FS |

V min |

|

|

|

|

2.1 × FS |

V max |

|

|

|

|

|

|

|

|

|

START-UP TIME |

|

|

|

|

|

From Power-On |

300 |

ms typ |

|

|

|

From Power-Down Mode |

1 |

ms typ |

|

|

|

|

300 |

ms typ |

|

Oscillator Powered Down |

|

|

|

|

|

|

|

POWER REQUIREMENTS |

|

|

|

|

|

Power Supply Voltages |

AVDD and DVDD can |

be operated independently |

of |

each other. |

|

AVDD–AGND |

2.7/3.6 |

V min/max |

|

|

AVDD = 3 V nom |

|

4.75/5.25 |

V min/max |

|

AVDD = 5 V nom |

|

DVDD–DGND |

2.7/3.6 |

V min/max |

|

DVDD = 3 V nom |

|

|

4.75/5.25 |

V min |

|

DVDD = 5 V nom |

|

DIDD (Normal Mode) |

0.55 |

mA max |

|

DVDD = 3 V, 0.43 mA typ |

|

|

0.65 |

mA |

|

DVDD = 5 V, 0.5 mA typ |

|

AIDD (Normal Mode) |

1.1 |

mA |

|

AVDD = 3 V or 5 V, 0.85 mA typ |

|

DIDD (Power-Down Mode) |

10 |

µA max |

|

DVDD = 3 V, 32.768 kHz Osc. Running |

|

|

2 |

µA max |

|

DVDD = 3 V, Oscillator Powered Down |

|

|

30 |

µA max |

|

DVDD = 5 V, 32.768 kHz Osc. Running |

|

|

8 |

µA max |

|

DVDD = 5 V, Oscillator Powered Down |

|

AIDD (Power-Down Mode) |

1 |

µA max |

|

AVDD = 3 V or 5 V |

|

Power Supply Rejection (PSR) |

|

|

|

|

Input Range = ± 2.56 V, AIN = 1 V |

Chop Disabled |

70 |

dB min |

|

95 dB typ |

|

Chop Enabled |

100 |

dB typ |

|

|

|

|

|

|

|

|

|

NOTES

1Temperature range is –40°C to +85°C.

2Not production tested, guaranteed by design and/or characterization data at release.

3Following a self-calibration this error will be in the order of the noise for the programmed gain and update selected. A system calibration will completely remove this error.

4Recalibration at any temperature will remove these errors. 5I/O Port Logic Levels are with respect to AVDD and AGND.

Specifications are subject to change without notice.

–8– |

REV. 0 |

AD7708/AD7718

TIMING CHARACTERISTICS1, 2 (AVDD = 2.7 V to 3.6 V or AVDD = 5 V 5%; DVDD = 2.7 V to 3.6 V or DVDD = 5 V 5%; AGND =

DGND = 0 V; XTAL = 32.768 kHz; Input Logic 0 = 0 V, Logic 1 = DVDD unless otherwise noted.

|

Limit at TMIN, TMAX |

|

|

Parameter |

(B Version) |

Unit |

Conditions/Comments |

|

|

|

|

t1 |

32.768 |

kHz typ |

Crystal Oscillator Frequency |

t2 |

50 |

ns min |

RESET Pulsewidth |

Read Operation |

|

|

|

t3 |

0 |

ns min |

RDY to CS Setup Time |

t4 |

0 |

ns min |

CS Falling Edge to SCLK Active Edge Setup Time3 |

t54 |

0 |

ns min |

SCLK Active Edge to Data Valid Delay3 |

|

60 |

ns max |

DVDD = 4.5 V to 5.5 V |

|

80 |

ns max |

DVDD = 2.7 V to 3.6 V |

t5A4, 5 |

0 |

ns min |

CS Falling Edge to Data Valid Delay3 |

|

60 |

ns max |

DVDD = 4.5 V to 5.5 V |

|

80 |

ns max |

DVDD = 2.7 V to 3.6 V |

t6 |

100 |

ns min |

SCLK High Pulsewidth |

t7 |

100 |

ns min |

SCLK Low Pulsewidth |

t8 |

0 |

ns min |

CS Rising Edge to SCLK Inactive Edge Hold Time3 |

t96 |

10 |

ns min |

Bus Relinquish Time after SCLK Inactive Edge3 |

|

80 |

ns max |

SCLK Active Edge to RDY High3, 7 |

t10 |

100 |

ns max |

|

Write Operation |

|

|

CS Falling Edge to SCLK Active Edge Setup Time3 |

t11 |

0 |

ns min |

|

t12 |

30 |

ns min |

Data Valid to SCLK Edge Setup Time |

t13 |

25 |

ns min |

Data Valid to SCLK Edge Hold Time |

t14 |

100 |

ns min |

SCLK High Pulsewidth |

t15 |

100 |

ns min |

SCLK Low Pulsewidth |

t16 |

0 |

ns min |

CS Rising Edge to SCLK Edge Hold Time |

NOTES

1Sample tested during initial release to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of DV DD) and timed from a voltage level of 1.6 V.

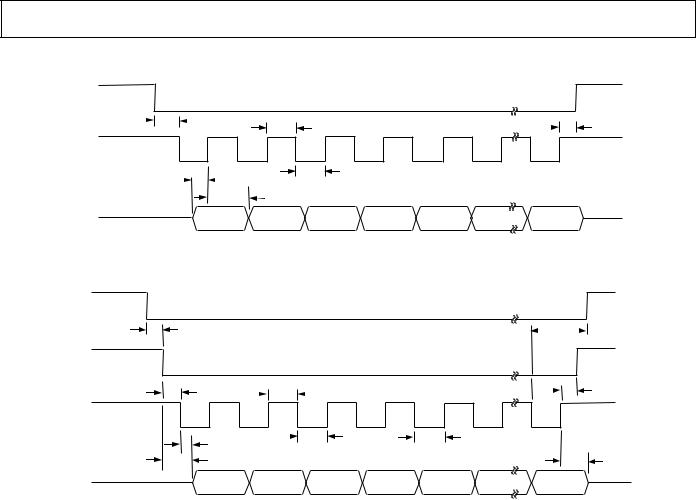

2See Figures 1 and 2.

3SCLK active edge is falling edge of SCLK.

4These numbers are measured with the load circuit of Figure 1 and defined as the time required for the output to cross the VOL or VOH limits. 5This specification only comes into play if CS goes low while SCLK is low. It is required primarily for interfacing to DSP machines.

6These numbers are derived from the measured time taken by the data output to change 0.5 V when loaded with the load circuit of Figure 1. The measured number is then extrapolated back to remove effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and as such are independent of external bus loading capacitances.

7RDY returns high after the first read from the device after an output update. The same data can be read again, if required, while RDY is high, although care should be taken that subsequent reads do not occur close to the next output update.

Specifications subject to change without notice.

ISINK (1.6mA WITH DVDD = 5V

100 A WITH DVDD = 3V)

TO OUTPUT |

1.6V |

|

PIN |

||

50pF |

||

|

ISOURCE

(200 A WITH DVDD = 5V

100 A WITH DVDD = 3V)

Figure 1. Load Circuit for Timing Characterization

REV. 0 |

–9– |

AD7708/AD7718

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C unless otherwise noted)

AVDD to AGND . . . . . . . . . . . . . . . . . |

. . . . . . –0.3 V to +7 V |

|

AVDD to DGND . . . . . . . . . . . . . . . . . |

. . . . . . –0.3 V to +7 V |

|

DVDD to AGND . . . . . . . . . . . . . . . . . |

. . . . . . –0.3 V to +7 V |

|

DVDD to DGND . . . . . . . . . . . . . . . . . |

. . . . . . –0.3 V to +7 V |

|

AGND to DGND . . . . . . . . . . . . . . . . |

. . –0.05 V to +0.05 V |

|

AVDD to DVDD . . . . . . . . . . . . . . . . . . |

. . . . . . . –5 V to +5 V |

|

Analog Input Voltage to AGND . . . . |

–0.3 V to AVDD +0.3 |

V |

Reference Input Voltage to AGND . . |

–0.3 V to AVDD +0.3 |

V |

Total AIN/REFIN Current (Indefinite) |

. . . . . . . . . . . . 30 mA |

|

Digital Input Voltage to DGND . . . . |

–0.3 V to DVDD +0.3 |

V |

Digital Output Voltage to DGND . . . |

–0.3 V to DVDD +0.3 |

V |

Operating Temperature Range . . . . . . |

. . . . . –40°C to +85°C |

|

Storage Temperature Range . . . . . . . . |

. . . . –65°C to +150°C |

|

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . |

. . 150°C |

SOIC Package |

71.4°C/W |

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . |

|

θJC Thermal Impedance . . . . . . . . . . . . . . . . . . . . . |

23°C/W |

TSSOP Package |

97.9°C/W |

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . |

|

θJC Thermal Impedance . . . . . . . . . . . . . . . . . . . . . |

14°C/W |

Lead Temperature, Soldering |

215°C |

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . . |

|

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 220°C |

*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ORDERING GUIDE

|

Temperature |

Package |

Package |

Model |

Range |

Description |

Option |

|

|

|

|

AD7708BR |

–40°C to +85°C |

SOIC |

R-28 |

AD7708BRU |

–40°C to +85°C |

TSSOP |

RU-28 |

EVAL-AD7708EB |

–40°C to +85°C |

|

Evaluation Board |

AD7718BR |

SOIC |

R-28 |

|

AD7718BRU |

–40°C to +85°C |

TSSOP |

RU-28 |

EVAL-AD7718EB |

|

|

Evaluation Board |

|

|

|

|

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7708/AD7718 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–10– |

REV. 0 |

AD7708/AD7718

CS

t11 |

t14 |

t16 |

SCLK |

|

|

|

t12 |

t15 |

|

|

|

|

t13 |

|

DIN |

MSB |

LSB |

Figure 2. Write Cycle Timing Diagram

RDY

t3 |

|

t10 |

CS |

|

|

t4 |

t6 |

t8 |

|

||

SCLK |

|

|

|

t7 |

t6 |

|

t5 |

|

t5A |

|

t9 |

DOUT |

MSB |

LSB |

Figure 3. Read Cycle Timing Diagram

REV. 0 |

–11– |

AD7708/AD7718

|

|

PIN FUNCTION DESCRIPTIONS |

|

|

|

Pin No |

Mnemonic |

Function |

|

|

|

1 |

AIN7 |

Analog Input Channel 7. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the positive input of a fully-differential input |

|

|

pair when used with AIN8. (See ADC Control Register section.) |

2 |

AIN8 |

Analog Input Channel 8. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the negative input of a fully-differential input |

|

|

pair when used with AIN7. (See ADC Control Register section.) |

3 |

AVDD |

Analog Supply Voltage |

4 |

AGND |

Analog Ground |

5 |

REFIN1(–) |

Negative Reference Input. This reference input can lie anywhere between AGND and AVDD – 1 V. |

6 |

REFIN1(+) |

Positive reference input. REFIN(+) can lie anywhere between AVDD and AGND. The nominal |

|

|

reference voltage [REFIN(+)–REFIN(–)] is 2.5 V but the part is functional with a reference |

|

|

range from 1 V to AVDD. |

7 |

AIN1 |

Analog Input Channel 1. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the positive input of a fully-differential input |

|

|

pair when used with AIN2. (See ADC Control Register Section.) |

8 |

AIN2 |

Analog Input Channel 2. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the negative input of a fully-differential input |

|

|

pair when used with AIN1. (See ADC Control Register section.) |

9 |

AIN3 |

Analog Input Channel 3. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the positive input of a fully-differential input |

|

|

pair when used with AIN4. (See ADC Control Register section.) |

10 |

AIN4 |

Analog Input Channel 4. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the negative input of a fully-differential input |

|

|

pair when used with AIN3. (See ADC Control Register section.) |

11 |

AIN5 |

Analog Input Channel 5. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the positive input of a fully-differential input |

|

|

pair when used with AIN6. (See ADC Control Register section ADCCON.) |

12 |

AINCOM |

All analog inputs are referenced to this input when configured in pseudo-differential input mode. |

13 |

REFIN2(+)/AIN9 |

Positive reference input/analog input. This input can be configured as a reference input with the |

|

|

same characteristics as REFIN1(+) or as an additional analog input. When configured as an |

|

|

analog input this pin provides a programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the positive input of a fully-differential input |

|

|

pair when used with AIN10. (See ADC Control Register section.) |

14 |

REFIN2(–)/AIN10 |

Negative reference input/analog input. This pin can be configured as a reference or analog input. |

|

|

When configured as a reference input it provides the negative reference input for REFIN2. |

|

|

When configured as an analog input it provides a programmable-gain analog input that can be |

|

|

used as a pseudo-differential input when used with AINCOM, or as the negative input of a fully- |

|

|

differential input pair when used with AIN9. (See ADC Control Register section.) |

15 |

AIN6 |

Analog Input Channel 6. Programmable-gain analog input that can be used as a pseudo- |

|

|

differential input when used with AINCOM, or as the negative input of a fully-differential input |

|

|

pair when used with AIN5. (See ADC Control Register section.) |

16 |

P2 |

P2 can act as a general-purpose Input/Output bit referenced between AVDD and AGND. There |

|

|

is a weak pull-up to AVDD internally on this pin. |

17 |

AGND |

It is recommended that this pin be tied directly to AGND. |

18 |

P1 |

P1 can act as a general-purpose Input/Output bit referenced between AVDD and AGND. There |

|

|

is a weak pull-up to AVDD internally on this pin. |

19 |

RESET |

Digital input used to reset the ADC to its power-on-reset status. This pin has a weak pull-up |

|

|

internally to DVDD. |

20 |

SCLK |

Serial clock input for data transfers to and from the ADC. The SCLK has a Schmitt-trigger |

|

|

input making an opto-isolated interface more robust. The serial clock can be continuous with all |

|

|

data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock |

|

|

with the information being transmitted to or from the AD7708/AD7718 in smaller batches of data. |

|

|

|

–12– |

REV. 0 |

AD7708/AD7718

Pin No |

Mnemonic |

Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

CS |

Chip Select Input. This is an active low logic input used to select the AD7708/AD7718. CS can |

||||||

|

|

be used to select the AD7708/AD7718 in systems with more than one device on the serial bus or |

||||||

|

|

as a frame synchronization signal in communicating with the device. CS can be hardwired low, |

||||||

|

|

allowing the AD7708/AD7718 to be operated in 3-wire mode with SCLK, DIN, and DOUT |

||||||

|

|

used to interface with the device. |

|

|

||||

22 |

RDY |

RDY is a logic low status output from the AD7708/AD7718. RDY is low when valid data exists |

||||||

|

|

in the data register for the selected channel. This output returns high on completion of a read |

||||||

|

|

operation from the data register. If data is not read, RDY will return high prior to the next update |

||||||

|

|

indicating to the user that a read operation should not be initiated. The RDY pin also returns |

||||||

|

|

low following the completion of a calibration cycle. RDY does not return high after a calibration |

||||||

|

|

until the mode bits are written to enabling a new conversion or calibration. |

||||||

23 |

DOUT |

Serial data output with serial data being read from the output shift register of the ADC. The output |

||||||

|

|

shift register can contain data from any of the on-chip data, calibration or control registers. |

||||||

24 |

DIN |

Serial Data Input with serial data being written to the input shift register on the AD7708/AD7718 |

||||||

|

|

Data in this shift register is transferred to the calibration or control registers within the ADC |

||||||

|

|

depending on the selection bits of the Communications register. |

||||||

25 |

DGND |

Ground Reference Point for the Digital Circuitry. |

||||||

26 |

DVDD |

Digital Supply Voltage, 3 V or 5 V Nominal. |

||||||

27 |

XTAL2 |

Output from the 32 kHz Crystal Oscillator or Resonator Inverter. |

||||||

28 |

XTAL1 |

Input to the 32 kHz Crystal Oscillator or Resonator Inverter. |

||||||

|

|

|

|

|

|

|

|

|

|

|

PIN CONFIGURATION |

||||||

|

|

|

|

|

|

|

|

XTAL1 |

|

|

|

|

|

|

|

|

|

|

|

AIN7 |

1 |

|

|

|

28 |

|

|

|

AIN8 |

|

|

|

|

|

XTAL2 |

|

|

2 |

|

|

|

27 |

||

|

|

AVDD |

|

|

|

|

|

|

|

|

3 |

|

|

|

26 |

DVDD |

|

|

|

AGND |

|

|

|

|

|

DGND |

|

|

4 |

AD7708/ |

25 |

||||

|

|

REFIN1(–) |

|

|

DIN |

|||

|

|

5 |

AD7718 |

24 |

||||

|

|

REFIN1(+) |

|

|

|

|||

|

|

6 |

TOP VIEW |

23 |

DOUT |

|||

|

|

AIN1 |

|

(Not to Scale) |

|

|

||

|

|

7 |

22 |

RDY |

||||

|

|

|

|

|

|

|

|

|

|

|

AIN2 |

8 |

|

|

|

21 |

CS |

|

|

AIN3 |

|

|

|

|

|

|

|

|

9 |

|

|

|

20 |

SCLK |

|

|

|

AIN4 |

|

|

|

|

|

|

|

|

10 |

|

|

|

19 |

RESET |

|

|

|

|

|

|

|

|

|

|

|

|

AIN5 |

11 |

|

|

|

18 |

P1 |

|

|

|

|

|

|

17 |

|

|

|

|

AINCOM |

12 |

|

|

|

AGND |

|

|

|

|

|

|

|

|

16 |

|

|

|

REFIN2(+)/AIN9 |

13 |

|

|

|

P2 |

|

|

|

REFIN2(–)/AIN10 |

|

|

|

|

15 |

|

|

|

14 |

|

|

|

AIN6 |

||

|

|

|

|

|

|

|

|

|

REV. 0 |

–13– |

AD7708/AD7718–Typical Performance Characteristics

|

8389600 |

AVDD = DVDD = 5V |

|

|

REFIN1(+)–REFIN1(–) = 2.5V |

||||||

|

|

|

|

||||||||

|

8389400 |

INPUT RANGE = 20mV |

|

UPDATE RATE = 19.79Hz |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

8389200 |

|

|

|

|

|

|

|

|

|

|

READ |

8389000 |

|

|

|

|

|

|

|

|

|

|

8388800 |

|

|

|

|

|

|

|

|

|

|

|

CODE |

8388600 |

|

|

|

|

|

|

|

|

|

|

|

8388400 |

|

|

|

|

|

|

|

|

|

|

|

8388200 |

|

|

|

|

|

|

|

TA = 25 C |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

8388000 |

RMS NOISE = 0.58 V rms |

|

|

VREF = 2.5V |

||||||

|

100 |

200 |

300 |

400 |

500 |

600 |

700 |

800 |

900 |

1000 |

|

|

0 |

||||||||||

READING NUMBER

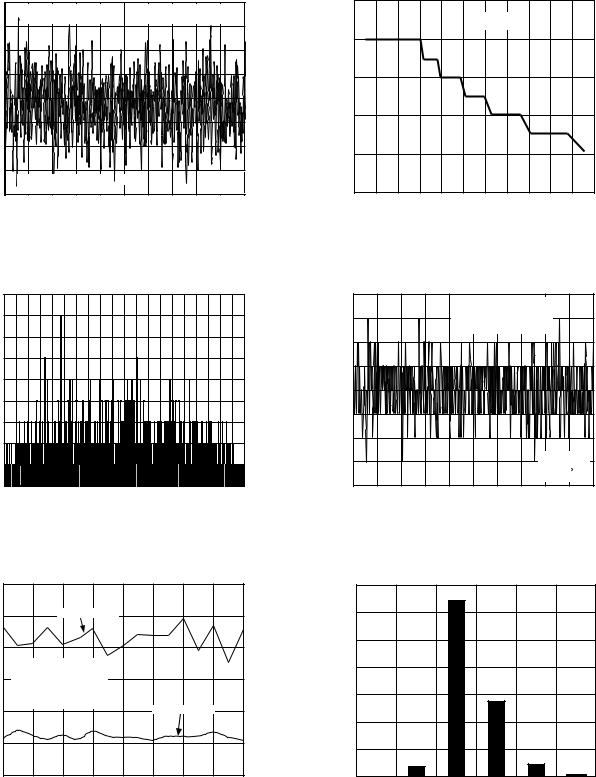

TPC 1. AD7718 Typical Noise Plot on ±20 mV Input Range with 19.79 Hz Update Rate

9

8

7

6

5

4

3

2

1

0

8388039 |

8388382 |

8388449 |

8388499 |

8388547 |

8388579 |

8388615 |

8388657 |

8388687 |

8388721 |

8388754 |

8388779 |

8388805 |

8388841 |

8388874 |

8388906 |

8388941 |

8388985 |

8389033 |

8389110 |

TPC 2. AD7718 Noise Distribution Histogram

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CHOP = 0 |

|

|

|

|

|

– Min |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CODES |

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NO MISSING |

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

|

|

|

|

|

|

|

|

110 |

|

0 |

10 |

20 |

30 |

40 |

50 |

60 |

70 |

80 |

90 |

100 |

|

|

|

|

|

|

UPDATE RATE – Hz |

|

|

|

|

|||

TPC 4. AD7718 No-Missing Codes Performance

32772

AVDD = DVDD = 5V

AVDD = DVDD = 5V

|

32771 |

|

|

|

INPUT RANGE = 20mV |

|

|

||||

|

|

|

|

|

UPDATE RATE = 19.79Hz |

|

|

||||

|

32770 |

|

|

|

|

|

|

|

|

|

|

READ |

32769 |

|

|

|

|

|

|

|

|

|

|

32768 |

|

|

|

|

|

|

|

|

|

|

|

CODE |

|

|

|

|

|

|

|

|

|

|

|

32767 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32766 |

|

|

|

|

|

|

|

|

|

|

|

32765 |

|

|

|

|

|

|

|

VREF = 2.5V |

||

|

|

|

|

|

|

|

|

|

TA = 25 C |

|

|

|

32764 |

100 |

200 |

300 |

400 |

500 |

600 |

700 |

800 |

900 |

1000 |

|

0 |

||||||||||

READING NUMBER

TPC 5. AD7708 Typical Noise Plot on ±20 mV Input Range

|

3.0 |

|

|

|

|

|

|

|

|

|

2.5 |

|

2.56V RANGE |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

V |

2.0 |

|

|

|

|

|

|

|

|

– |

|

AVDD = DVDD = 5V |

|

|

|

|

|

|

|

NOISE |

|

|

|

|

|

|

|

||

1.5 |

VREF = 2.5V |

|

|

|

|

|

|

|

|

INPUT RANGE = 2.56V |

|

|

|

|

|

||||

|

|

|

|

|

|

||||

|

UPDATE RATE = 19.79Hz |

|

|

|

|

|

|||

RMS |

|

|

|

|

|

|

|||

1.0 |

TA = 25 C |

|

|

|

20mV RANGE |

|

|||

|

|

|

|

|

|

|

|

|

|

|

0.5 |

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

1.0 |

1.5 |

2.0 |

2.5 |

3.0 |

3.5 |

4.0 |

4.5 |

5.0 |

|

|

|

|

|

VREF – V |

|

|

|

|

TPC 3. RMS Noise vs. Reference Input (AD7718 andAD7708)

|

700 |

|

|

|

|

|

|

600 |

|

|

|

|

|

|

500 |

|

|

|

|

|

OCCURRENCE |

400 |

|

|

|

|

|

300 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

200 |

|

|

|

|

|

|

100 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

32766 |

32767 |

32768 |

32769 |

32770 |

32771 |

|

|

|

CODE |

|

|

|

TPC 6. AD7708 Noise Histogram

–14– |

REV. 0 |

Loading...

Loading...