Analog Devices AD7541AKN, AD7541AJP, AD7541AJN, AD7541ABQ, AD7541AAQ Datasheet

...

a |

CMOS |

12-Bit Monolithic Multiplying DAC |

|

|

|

|

AD7541A |

|

FEATURES |

FUNCTIONAL BLOCK DIAGRAM |

||||

Improved Version of AD7541 |

10kΩ |

10kΩ |

|

10kΩ |

|

Full Four-Quadrant Multiplication |

|

||||

VREF |

|

|

|

||

12-Bit Linearity (Endpoint) |

|

|

|

||

20kΩ |

20kΩ |

20kΩ |

20kΩ 20kΩ |

||

All Parts Guaranteed Monotonic |

|||||

S1 |

S2 |

S3 |

S12 |

||

TTL/CMOS Compatible |

|||||

|

|

|

|

||

Low Cost |

|

|

|

|

|

Protection Schottky Diodes Not Required |

|

|

|

OUT2 |

|

Low Logic Input Leakage |

|

|

|

||

|

|

|

OUT1 |

||

|

|

|

|

||

|

|

|

|

10kΩ |

|

|

|

|

|

RFEEDBACK |

|

GENERAL DESCRIPTION

The Analog Devices AD7541A is a low cost, high performance 12-bit monolithic multiplying digital-to-analog converter. It is fabricated using advanced, low noise, thin film on CMOS technology and is available in a standard 18-lead DIP and in 20-terminal surface mount packages.

The AD7541A is functionally and pin compatible with the industry standard AD7541 device and offers improved specifications and performance. The improved design ensures that the device is latch-up free so no output protection Schottky diodes are required.

This new device uses laser wafer trimming to provide full 12-bit endpoint linearity with several new high performance grades.

ORDERING GUIDE1

|

|

Relative |

Gain |

|

|

Temperature |

Accuracy |

Error |

Package |

Model2 |

Range |

TMIN to TMAX |

TA = +258C |

Options3 |

AD7541AJN |

0°C to +70°C |

±1 LSB |

±6 LSB |

N-18 |

AD7541AKN |

0°C to +70°C |

±1/2 LSB |

±1 LSB |

N-18 |

AD7541AJP |

0°C to +70°C |

±1 LSB |

±6 |

P-20A |

AD7541AKP |

0°C to +70°C |

±1/2 LSB |

±1 |

P-20A |

AD7541AKR |

0°C to +70°C |

±1/2 LSB |

±1 |

R-18 |

AD7541AAQ |

–25°C to +85°C |

±1 LSB |

±6 LSB |

Q-18 |

AD7541ABQ |

–25°C to +85°C |

±1/2 LSB |

±1 LSB |

Q-18 |

AD7541ASQ |

–55°C to +125°C |

±1 LSB |

±6 LSB |

Q-18 |

AD7541ATQ |

–55°C to +125°C |

±1/2 LSB |

±1 LSB |

Q-18 |

AD7541ASE |

–55°C to +125°C |

±1 LSB |

±6 LSB |

E-20A |

AD7541ATE |

–55°C to +125°C |

±1/2 LSB |

±1 LSB |

E-20A |

NOTES

1Analog Devices reserves the right to ship either ceramic (D-18) or cerdip (Q-18) hermetic packages.

2To order MIL-STD-883, Class B process parts, add /883B to part number. Contact local sales office for military data sheet.

3E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip; R = Small Outline IC.

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

BIT 1 (MSB) BIT 2 |

BIT 3 |

BIT 12 (LSB) |

DIGITAL INPUTS (DTL/TTL/CMOS COMPATIBLE)

LOGIC: A SWITCH IS CLOSED TO IOUT1 FOR

ITS DIGITAL INPUT IN A "HIGH" STATE.

PRODUCT HIGHLIGHTS

Compatibility: The AD7541A can be used as a direct replacement for any AD7541-type device. As with the Analog Devices AD7541, the digital inputs are TTL/CMOS compatible and have been designed to have a ±1 μA maximum input current requirement so as not to load the driving circuitry.

Improvements: The AD7541A offers the following improved specifications over the AD7541:

1.Gain Error for all grades has been reduced with premium grade versions having a maximum gain error of ±3 LSB.

2.Gain Error temperature coefficient has been reduced to 2 ppm/°C typical and 5 ppm/°C maximum.

3.Digital-to-analog charge injection energy for this new device is typically 20% less than the standard AD7541 part.

4.Latch-up proof.

5.Improvements in laser wafer trimming provides 1/2 LSB max differential nonlinearity for top grade devices over the operating temperature range (vs. 1 LSB on older 7541 types).

6.All grades are guaranteed monotonic to 12 bits over the operating temperature range.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 617/326-8703 |

© Analog Devices, Inc., 1997 |

AD7541A–SPECIFICATIONS (VDD = +15 V, VREF = +10 V; OUT 1 = OUT 2 = GND = 0 V unless otherwise noted)

|

|

TA = |

TA = |

1 |

|

|

|

Parameter |

Version |

+258C |

TMIN, TMAX |

Units |

Test Conditions/Comments |

||

|

|||||||

ACCURACY |

|

|

|

|

|

|

|

Resolution |

All |

12 |

12 |

|

Bits |

|

|

Relative Accuracy |

J, A, S |

±1 |

± 1 |

|

LSB max |

±1 LSB = ±0.024% of Full Scale |

|

|

K, B, T |

±1/2 |

± 1/2 |

|

LSB max |

± 1/2 LSB = ± 0.012% of Full Scale |

|

Differential Nonlinearity |

J, A, S |

±1 |

± 1 |

|

LSB max |

All Grades Guaranteed Monotonic |

|

|

K, B, T |

±1/2 |

± 1/2 |

|

LSB max |

to 12 Bits, TMIN to TMAX. |

|

Gain Error |

J, A, S |

± 6 |

±8 |

|

LSB max |

Measured Using Internal RFB and Includes |

|

|

K, B, T |

± 3 |

±5 |

|

LSB max |

Effect of Leakage Current and Gain TC. |

|

|

|

|

|

|

|

Gain Error Can Be Trimmed to Zero. |

|

Gain Temperature Coefficient2 |

|

|

|

|

ppm/°C max |

Typical Value Is 2 ppm/°C. |

|

DGain/DTemperature |

All |

5 |

5 |

|

|||

Output Leakage Current |

|

± 5 |

±10 |

|

|

|

|

OUT1 (Pin 1) |

J, K |

|

nA max |

All Digital Inputs = 0 V. |

|||

|

A, B |

± 5 |

±10 |

|

nA max |

|

|

|

S, T |

± 5 |

±200 |

|

nA max |

|

|

OUT2 (Pin 2) |

J, K |

± 5 |

±10 |

|

nA max |

All Digital Inputs = VDD. |

|

|

A, B |

±5 |

±10 |

|

nA max |

|

|

|

S, T |

±5 |

± 200 |

|

nA max |

|

|

|

|

|

|

|

|

|

|

REFERENCE INPUT |

|

|

|

|

kΩ min/max |

Typical Input Resistance = 11 kΩ. |

|

Input Resistance (Pin 17 to GND) |

All |

7–18 |

7–18 |

|

|||

|

|

|

|

|

|

Typical Input Resistance Temperature |

|

|

|

|

|

|

|

Coefficient = –300 ppm/°C. |

|

|

|

|

|

|

|

|

|

DIGITAL INPUTS |

|

|

|

|

|

|

|

VIH (Input HIGH Voltage) |

All |

2.4 |

2.4 |

|

V min |

|

|

VIL (Input LOW Voltage) |

All |

0.8 |

0.8 |

|

V max |

|

|

IIN (Input Current) |

All |

±1 |

± 1 |

|

μA max |

Logic Inputs Are MOS Gates. IIN typ (25°C) = 1 nA. |

|

CIN (Input Capacitance)2 |

All |

8 |

8 |

|

pF max |

VIN = 0 V |

|

POWER SUPPLY REJECTION |

|

±0.01 |

± 0.02 |

|

|

DVDD = ±5% |

|

DGain/DVDD |

All |

|

% per % max |

||||

POWER SUPPLY |

|

|

|

|

|

|

|

VDD Range |

All |

+5 to +16 |

+5 to +16 |

|

V min/V max |

Accuracy Is Not Guaranteed Over This Range. |

|

IDD |

All |

2 |

2 |

|

mA max |

All Digital Inputs VIL or VIH. |

|

|

|

100 |

500 |

|

μA max |

All Digital Inputs 0 V or VDD. |

|

|

|

|

|

|

|

|

AC PERFORMANCE CHARACTERISTICS

These Characteristics are included for Design Guidance only and are not subject to test. VDD = +15 V, VIN = +10 V except where noted, OUT1 = 0UT2 = GND = 0 V, Output Amp is AD544 except where noted.

|

|

Version1 |

TA = |

TA = |

|

|

Parameter |

+258C |

TMIN, TMAX1 |

Units |

Test Conditions/Comments |

||

PROPAGATION DELAY (From Digital Input |

|

|

|

|

OUT 1 Load = 100 Ω, CEXT = 13 pF. |

|

|

Change to 90% of Final Analog Output) |

All |

100 |

— |

ns typ |

Digital Inputs = 0 V to VDD or VDD to 0 V. |

DIGITAL TO ANALOG GLITCH |

|

|

|

|

VREF = 0 V. All digital inputs 0 V to VDD or |

|

|

IMPULSE |

|

|

|

|

VDD to 0 V. |

|

|

All |

1000 |

— |

nV-sec typ |

Measured using Model 50K as output amplifier. |

|

|

|

|

|

|

|

MULTIPLYING FEEDTHROUGH ERROR3 |

|

|

|

|

VREF = ± 10 V, 10 kHz sine wave. |

|

|

(VREF to OUT1) |

All |

1.0 |

— |

mV p-p typ |

|

OUTPUT CURRENT SETTLING TIME |

All |

0.6 |

— |

μs typ |

To 0.01% of full-scale range. |

|

|

|

|

|

|

|

OUT 1 Load = 100 Ω, CEXT = 13 pF. |

|

|

|

|

|

|

Digital Inputs = 0 V to VDD or VDD to 0 V. |

|

OUTPUT CAPACITANCE |

|

|

|

|

|

|

COUT1 (Pin 1) |

All |

200 |

200 |

pF max |

Digital Inputs |

|

COUT2 (Pin 2) |

All |

70 |

70 |

pF max |

= VIH |

|

COUT1 (Pin 1) |

All |

70 |

70 |

pF max |

Digital Inputs |

|

COUT2 (Pin 2) |

All |

200 |

200 |

pF max |

= VIL |

NOTES

1Temperature range as follows: J, K versions, 0°C to +70°C; A, B versions, –25°C to +85°C; S, T versions, –55°C to +125°C. 2Guaranteed by design but not production tested.

3To minimize feedthrough in the ceramic package (Suffix D) the user must ground the metal lid.

Specifications subject to change without notice.

–2– |

REV. B |

AD7541A

ABSOLUTE MAXIMUM RATINGS*

(TA = +25°C unless otherwise noted)

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +17 V VREF to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 25 V VRFB to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 25 V Digital Input Voltage to GND . . . . . . . . –0.3 V, VDD + 0.3 V

OUT 1, OUT 2 to GND . . . . . . . . . . . . –0.3 V, VDD + 0.3 V Power Dissipation (Any Package)

To +75°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 450 mW Derates above +75°C . . . . . . . . . . . . . . . . . . . . . . 6 mW/°C

Operating Temperature Range

Commercial (J, K Versions) . . . . . . . . . . . . . 0°C to +70°C Industrial (A, B Versions) . . . . . . . . . . . . . –25°C to +85°C Extended (S, T Versions) . . . . . . . . . . . . . –55°C to +125°C Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . +300°C

*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7541A features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

TERMINOLOGY

RELATIVE ACCURACY

Relative accuracy or endpoint nonlinearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero and full scale and is expressed in % of fullscale range or (sub)multiples of 1 LSB.

DIFFERENTIAL NONLINEARITY

Differential nonlinearity is the difference between the measured change and the ideal l LSB change between any two adjacent codes. A specified differential nonlinearity of ±1 LSB max over the operating temperature range insures monotonicity.

GAIN ERROR

Gain error is a measure of the output error between an ideal DAC and the actual device output. For the AD7541A, ideal maximum output is

æ |

4095 |

ö |

|

– ç |

|

÷ (VREF ). |

|

4096 |

|||

è |

ø |

Gain error is adjustable to zero using external trims as shown in Figures 4, 5 and 6.

OUTPUT LEAKAGE CURRENT

Current which appears at OUTI with the DAC loaded to all 0s or at OUT2 with the DAC loaded to all 1s.

MULTIPLYING FEEDTHROUGH ERROR

AC error due to capacitive feedthrough from VREF terminal to OUT1 with DAC loaded to all 0s.

OUTPUT CURRENT SETTLING TIME

Time required for the output function of the DAC to settle to within 1/2 LSB for a given digital input stimulus, i.e., 0 to full scale.

PROPAGATION DELAY

This is a measure of the internal delay of the circuit and is measured from the time a digital input changes to the point at which the analog output at OUT1 reaches 90% of its final value.

DIGITAL-TO-ANALOG CHARGE INJECTION (QDA)

This is a measure of the amount of charge injected from the digital inputs to the analog outputs when the inputs change state. It is usually specified as the area of the glitch in nV secs

and is measured with VREF = GND and a Model 50K as the output op amp, C1 (phase compensation) = 0 pF.

|

|

|

|

|

|

|

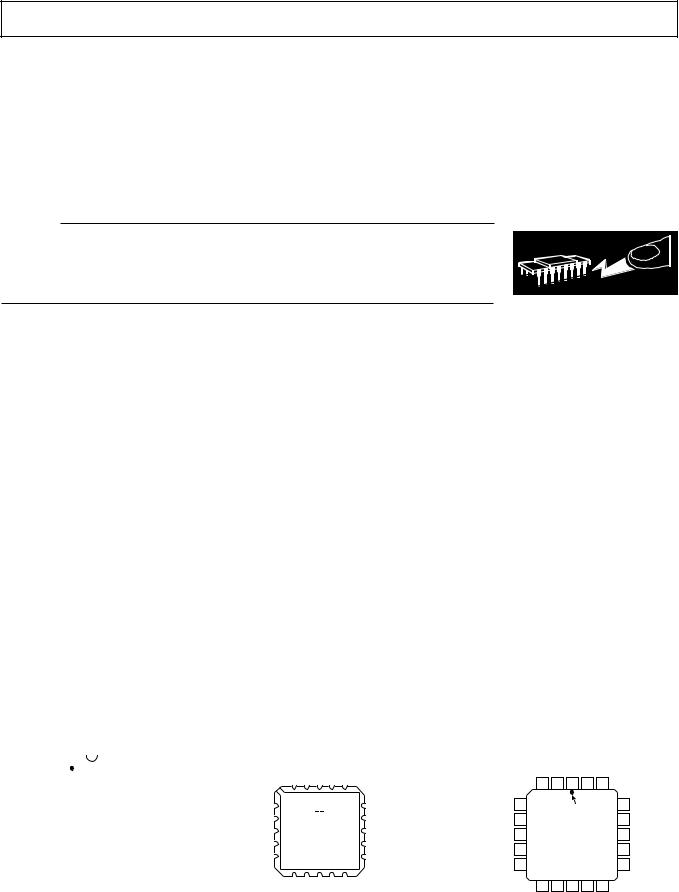

PIN CONFIGURATIONS |

|||||||||

|

|

DIP/SOIC |

|

|

|

|

|

LCCC |

|

|

||||||

|

|

|

|

|

|

|

|

2 |

1 |

|

|

|

REF |

|

|

|

|

|

|

|

|

|

|

|

OUT |

OUT |

NC |

FB |

|

|

|||

OUT1 |

1 |

|

|

|

18 |

RFEEDBACK |

|

|

|

|||||||

|

|

|

|

R |

V |

|

|

|||||||||

|

|

|

|

|

|

VREF IN |

|

3 |

2 |

1 |

|

20 |

19 |

|

|

|

OUT2 |

2 |

|

|

|

17 |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

3 |

|

|

|

16 |

VDD (+) |

GND 4 |

|

|

|

|

|

|

|

18 VDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

BIT 1 (MSB) |

4 |

AD7541A |

15 |

BIT 12 (LSB) |

BIT 1 (MSB) 5 |

|

AD7541A |

|

|

17 |

BIT 12 (LSB) |

|||||

BIT 2 |

|

|

|

|

|

|

||||||||||

5 |

TOP VIEW |

14 |

BIT 11 |

BIT 2 6 |

|

TOP VIEW |

|

|

16 |

BIT 11 |

||||||

BIT 3 |

|

(Not to Scale) |

|

BIT 10 |

BIT 3 7 |

(Not to Scale) |

|

15 |

BIT 10 |

|||||||

6 |

|

|

|

13 |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

BIT 4 |

|

|

|

|

|

|

BIT 4 8 |

|

|

|

|

|

|

|

14 |

BIT 9 |

7 |

|

|

|

12 |

BIT 9 |

|

|

|

|

|

|

|

|

|

|

|

BIT 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

|

11 |

BIT 8 |

|

9 |

10 |

11 |

12 |

13 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||||

BIT 6 |

|

|

|

|

|

|

|

BIT5 |

BIT6 |

NC |

BIT7 |

BIT8 |

|

|

||

9 |

|

|

|

10 |

BIT 7 |

NC = NO CONNECT |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PLCC |

|

|||

|

|

|

2 |

1 |

|

|

REF |

|

|

|

|

|

OUT |

OUT |

NC |

FB |

|

||

|

|

|

R |

V |

|

||||

|

|

|

3 |

2 |

1 |

20 |

19 |

|

|

|

|

|

|

|

|

|

|

|

|

GND |

4 |

|

|

|

|

PIN 1 |

18 |

VDD |

|

|

|

|

|

|

|

IDENTIFIER |

|

||

BIT 1 (MSB) |

5 |

|

|

AD7541A |

17 |

BIT 12 (LSB) |

|||

BIT 2 |

|

|

|

|

|

|

|||

6 |

|

|

TOP VIEW |

16 |

BIT 11 |

||||

BIT 3 |

7 |

|

|

(Not to Scale) |

15 |

BIT 10 |

|||

|

|

|

|

|

|||||

BIT 4 |

8 |

|

|

|

|

|

14 |

BIT 9 |

|

|

|

|

9 |

10 |

11 |

12 |

13 |

|

|

NC = NO CONNECT |

BIT5 |

BIT6 |

NC |

BIT7 |

BIT8 |

|

|||

REV. B |

–3– |

Loading...

Loading...