Texas Instruments TMS320F243PGEA, TMS320F243PGE, TMS320F241PGS, TMS320F241PGA, TMS320F241PG Datasheet

...

TMS320F243, TMS320F241

DSP CONTROLLERS

SPRS064B ± DECEMBER 1997 ± REVISED FEBRUARY 1999

D High-Performance Static CMOS Technology |

D |

|

D Includes the T320C2xx Core CPU |

D |

|

± Object-Compatible With the TMS320C2xx |

|

|

± Source-Code-Compatible With |

D |

|

TMS320C25 |

||

D |

||

± Upwardly Compatible With TMS320C5x |

||

|

||

± 50-ns Instruction Cycle Time |

|

Controller Area Network (CAN) Module

26 Individually Programmable, Multiplexed

General-Purpose I/O (GPIO) Pins

Six Dedicated GPIO Pins ('F243 only)

Phase-Locked-Loop (PLL)-Based Clock

Module

DCommercial and Industrial Temperature Available

DMemory

±544 Words x 16 Bits of On-Chip Data/Program Dual-Access RAM (DARAM)

±8K Words x 16 Bits of Flash EEPROM

±224K Words x 16 Bits of Total Memory Address Reach ('F243 only)

DExternal Memory Interface ('F243 only)

DEvent-Manager Module

±Eight Compare/Pulse-Width Modulation (PWM) Channels

±Two 16-Bit General-Purpose Timers With Six Modes, Including Continuous Upand Up/Down Counting

±Three 16-Bit Full Compare Units With Deadband

±Three Capture Units (Two With Quadrature Encoder-Pulse Interface Capability)

DSingle 10-Bit Analog-to-Digital Converter (ADC) Module With 8 Multiplexed Input Channels

DWatchdog (WD) Timer Module

DSerial Communications Interface (SCI) Module

D16-Bit Serial Peripheral Interface (SPI) Module

DFive External Interrupts (Power Drive Protection, Reset, NMI, and Two Maskable Interrupts)

DThree Power-Down Modes for Low-Power Operation

DScan-Based Emulation

DDevelopment Tools Available:

±Texas Instruments (TI ) ANSI C

Compiler, Assembler/Linker, and C-Source Debugger

±Full Range of Emulation Products

± Self-Emulation (XDS510 )

±Third-Party Digital Motor Control and Fuzzy-Logic Development Support

D144-Pin QFP PGE Package ('F243)

D68-Pin PLCC FN Package ('F241)

D64-Pin QFP PG Package ('F241)

description

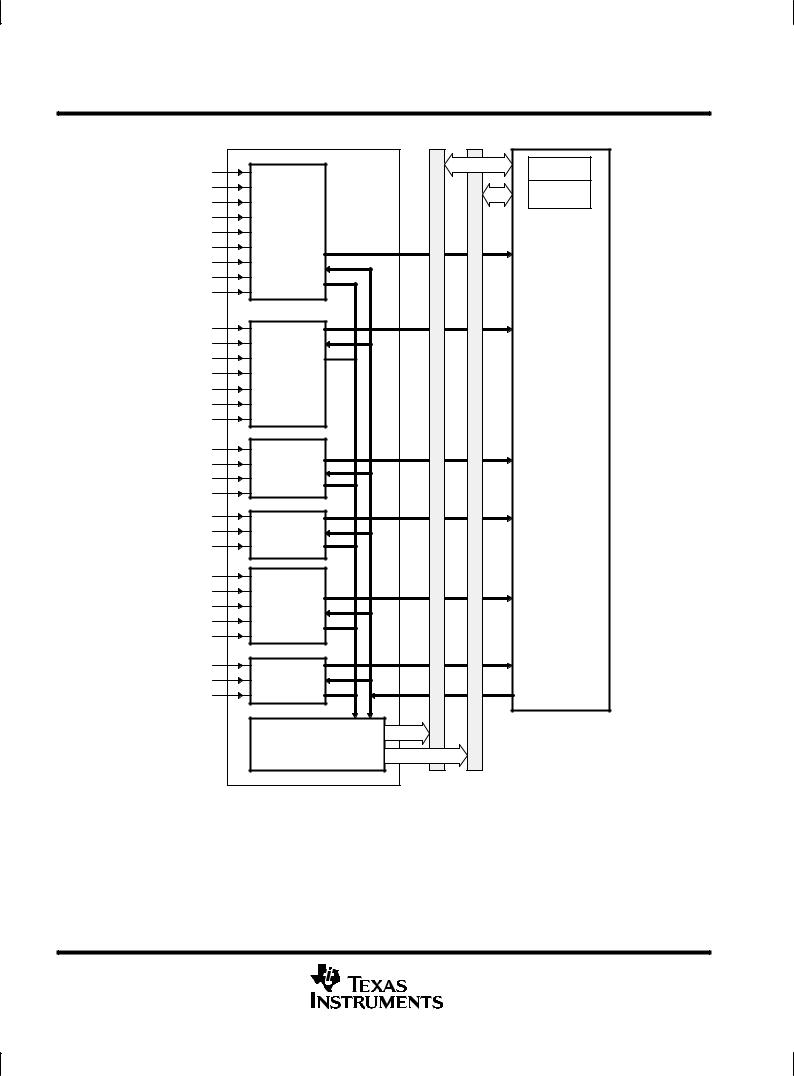

The TMS320F243 and TMS320F241 devices are members of the '24x family of digital signal processor (DSP) controllers based on the TMS320C2xx generation of 16-bit fixed-point DSPs. The 'F243 is a superset of the 'F241. These two devices share similar core and peripherals with some exceptions. For example, the 'F241 does not have an external memory interface. This new family is optimized for digital motor/motion control applications. The DSP controllers combine the enhanced TMS320 architectural design of the 'C2xx core CPU for low-cost, high-performance processing capabilities and several advanced peripherals optimized for motor/motion control applications. These peripherals include the event manager module, which provides general-purpose timers and PWM registers to generate PWM outputs, and a single,10-bit analog-to-digital converter (ADC), which can perform conversion within 1 μs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI and XDS510 are trademarks of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. |

Copyright 1999, Texas Instruments Incorporated |

Products conform to specifications per the terms of Texas Instruments |

|

standard warranty. Production processing does not necessarily include |

|

testing of all parameters. |

|

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

1 |

TMS320F243, TMS320F241

DSP CONTROLLERS

SPRS064B ± DECEMBER 1997 ± REVISED FEBRUARY 1999

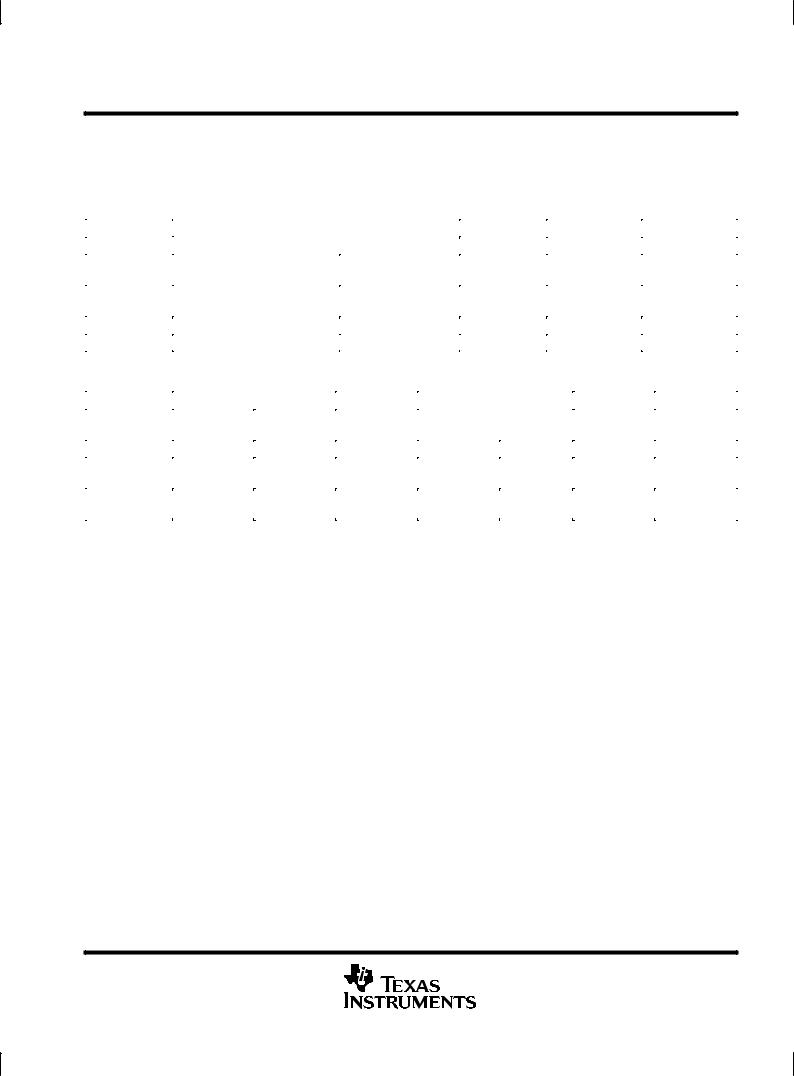

Table of Contents

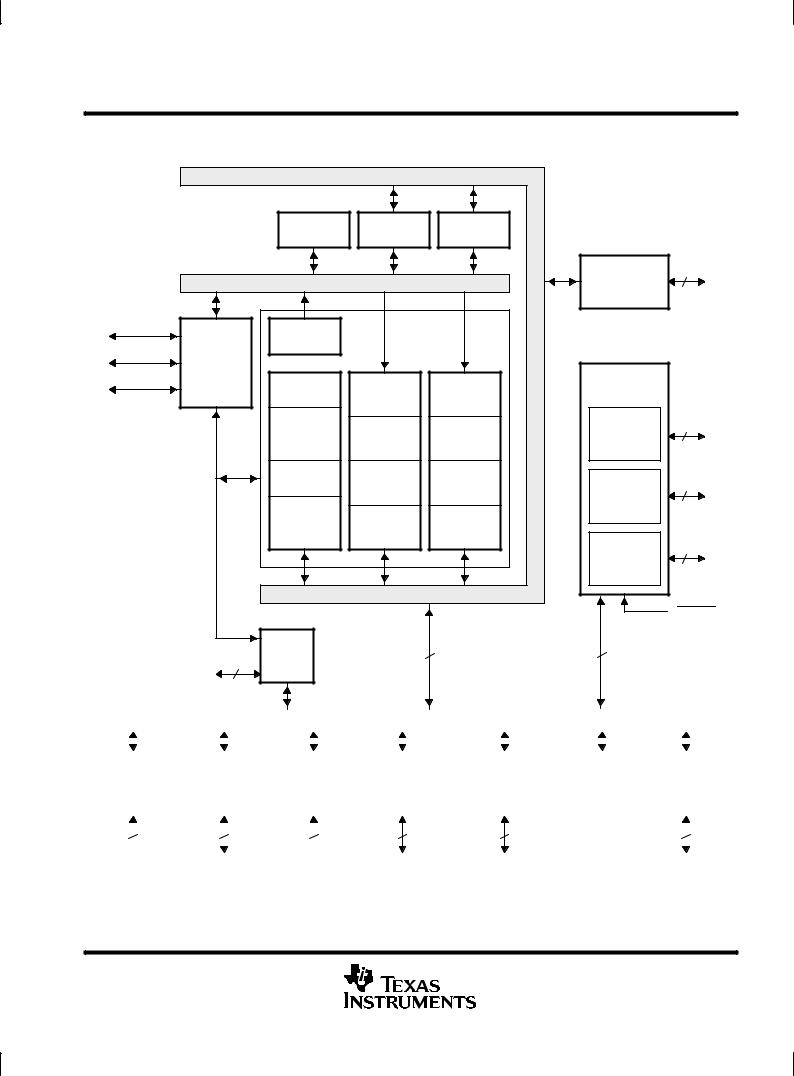

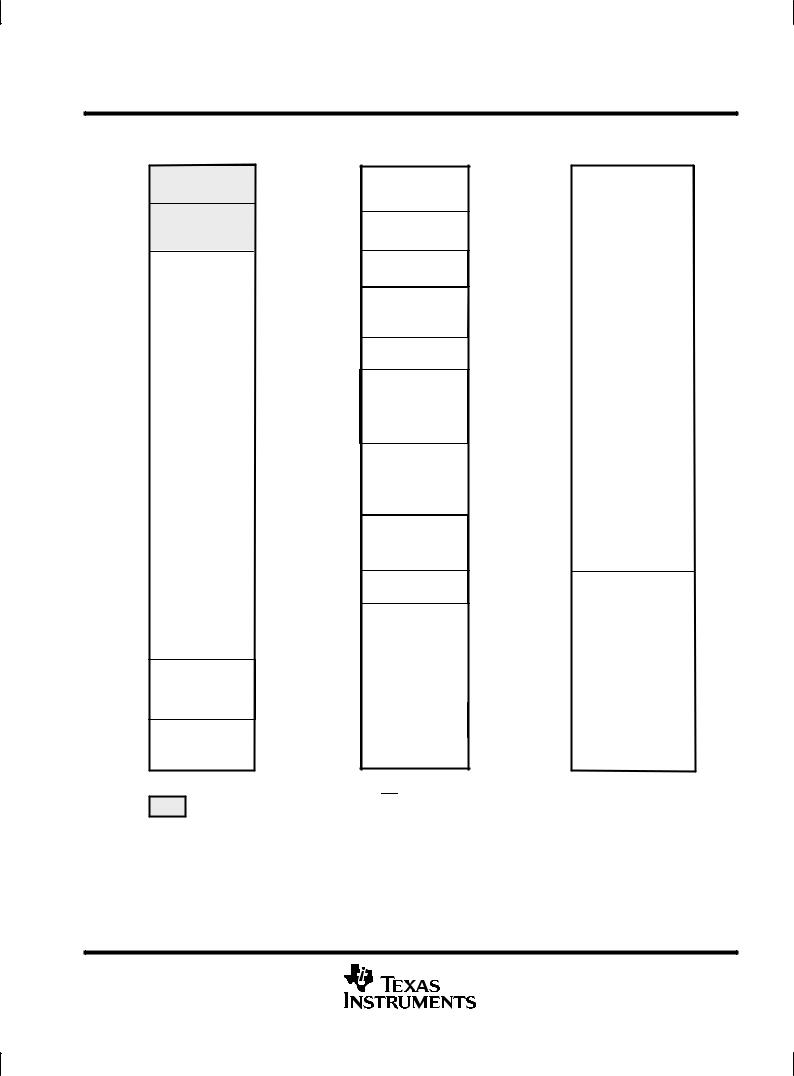

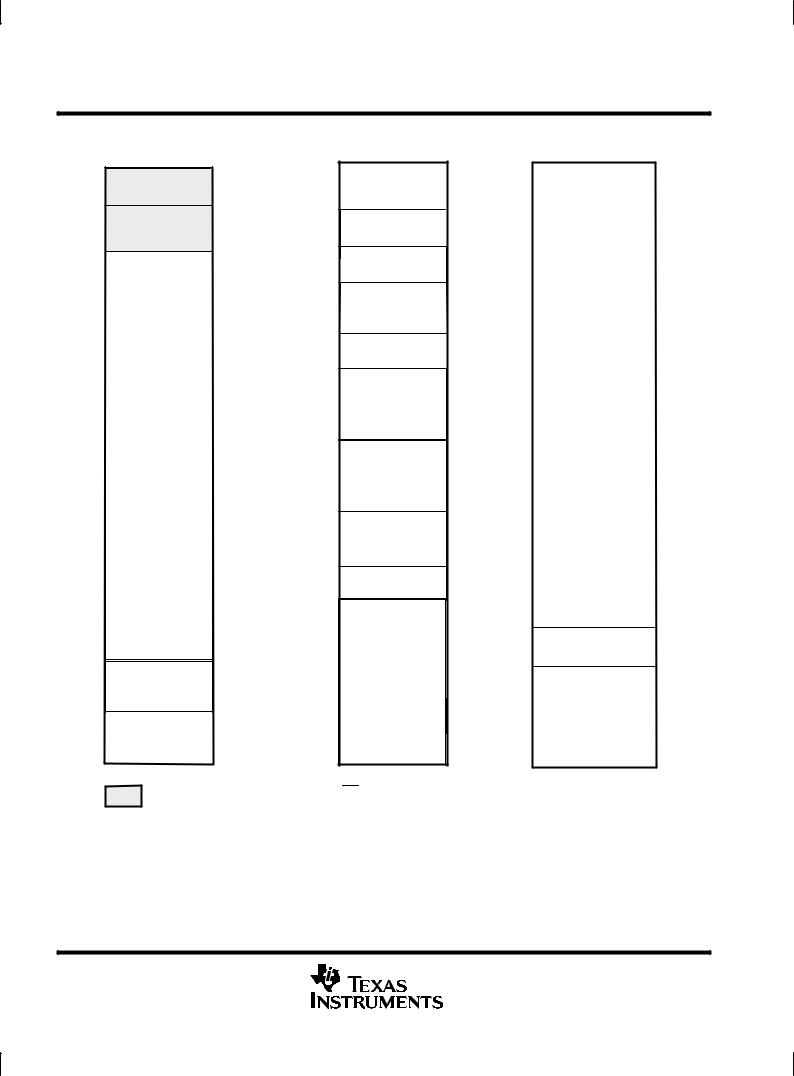

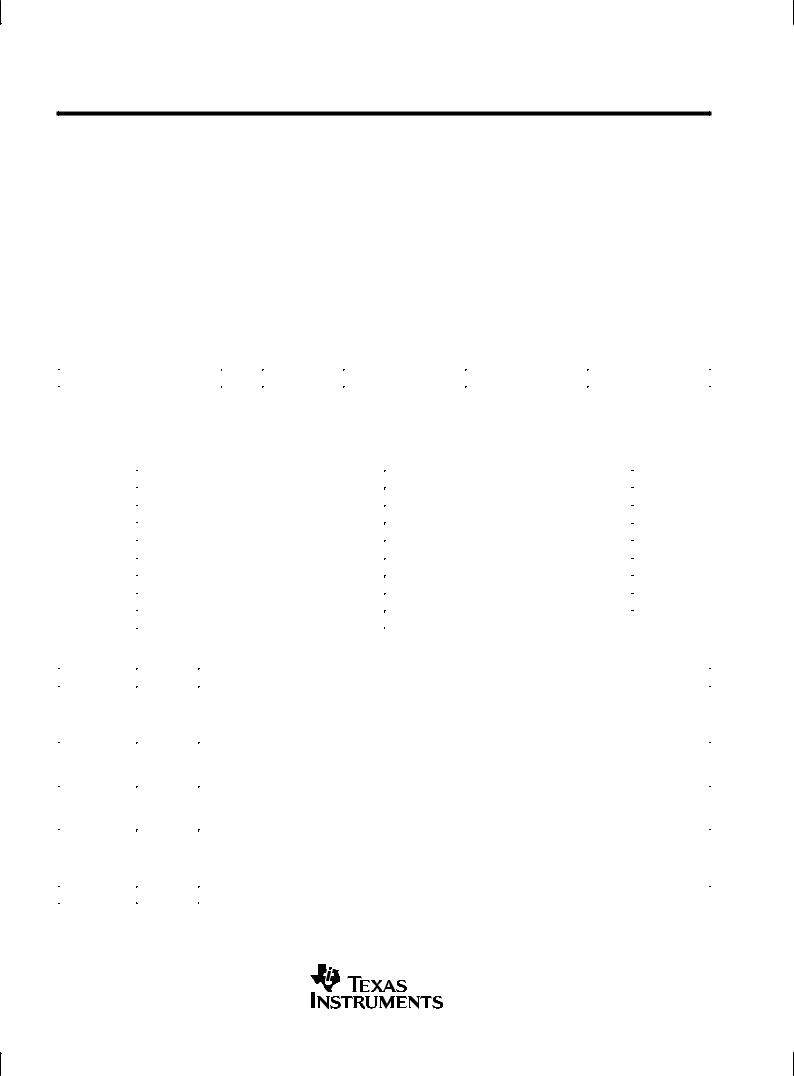

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Device Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 PGE Package, 144-Pin QFP, 'F243 . . . . . . . . . . . . . . . . 4 FN Package, 68-Pin PLCC, 'F241 . . . . . . . . . . . . . . . . . 5 PG Package, 64-Pin QFP, 'F241 . . . . . . . . . . . . . . . . . . . 6 Terminal Functions - 'F243 PGE Package . . . . . . . . . . . 7 Terminal Functions - 'F241 PG and FN Packages . . . 14 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . 17 Architectural Overview . . . . . . . . . . . . . . . . . . . . . . . . . . 18 System-Level Functions . . . . . . . . . . . . . . . . . . . . . . . . . 18

Device Memory Maps . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Memory Maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 Peripheral Memory Map . . . . . . . . . . . . . . . . . . . . . . . . 21 Software-Controlled Wait-State Generator . . . . . . . . 22 Digital I/O and Shared Pin Functions . . . . . . . . . . . . . 23 Digital I/O Control Registers . . . . . . . . . . . . . . . . . . . . 26 Device Reset and Interrupts . . . . . . . . . . . . . . . . . . . . 26 Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Functional Block Diagram of the '24x DSP CPU . . . . 37 '24x Legend for the Internal Hardware . . . . . . . . . . . 38 'F243/'F241 DSP Core CPU . . . . . . . . . . . . . . . . . . . . . 39 Internal Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 External Memory Interface ('F243 only) . . . . . . . . . . 45 Wait-State Generation ('F243 only) . . . . . . . . . . . . . . 46 Event-Manager (EV2) Module . . . . . . . . . . . . . . . . . . 47 Analog-to-Digital Converter (ADC) Module . . . . . . . . 50 A/D Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 Serial Peripheral Interface (SPI) Module . . . . . . . . . . 52 Serial Communications Interface (SCI) Module . . . . 54 Controller Area Network (CAN) Module . . . . . . . . . . 56 Watchdog (WD) Timer Module . . . . . . . . . . . . . . . . . . 60 Scan-Based Emulation . . . . . . . . . . . . . . . . . . . . . . . . . . 62 TMS320x24x Instruction Set . . . . . . . . . . . . . . . . . . . . . 62 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 Repeat Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . 63 Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 Nomenclature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Documentation Support . . . . . . . . . . . . . . . . . . . . . . . . . 72 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . 73 Recommended Operating Conditions . . . . . . . . . . . . . 73 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 73 Parameter Measurement Information . . . . . . . . . . . . . . 74

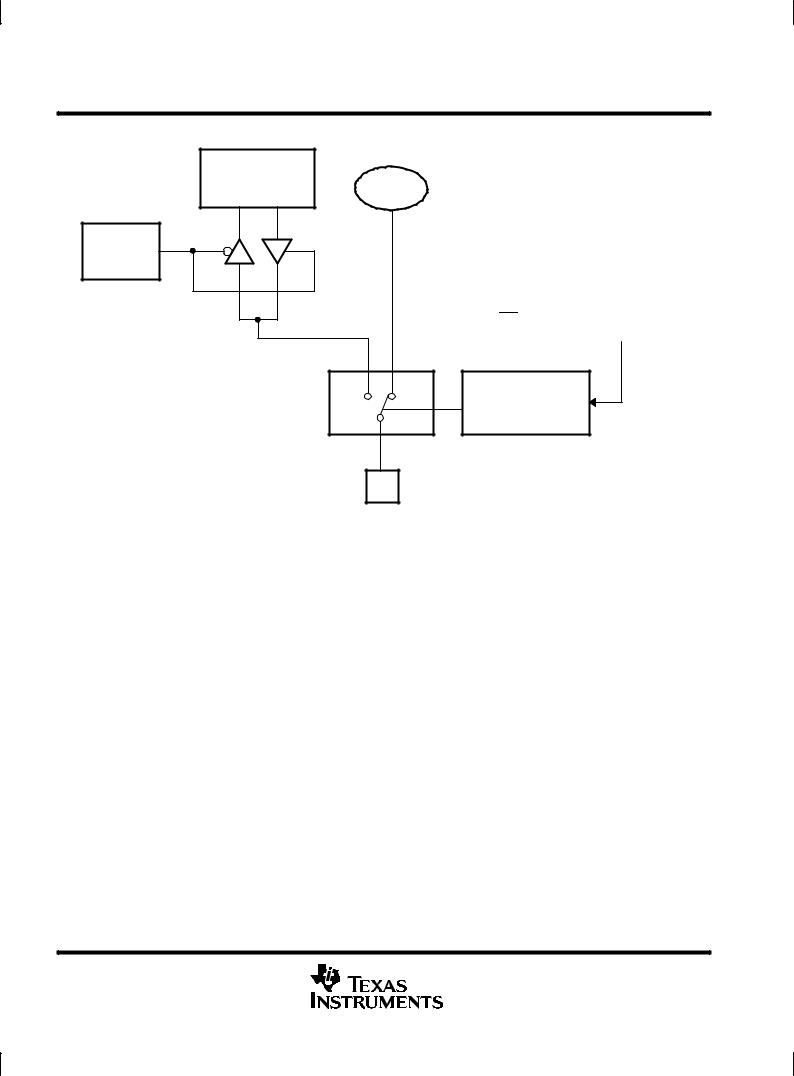

Signal Transition Levels . . . . . . . . . . . . . . . . . . . . . . . . 74 Timing Parameter Symbology . . . . . . . . . . . . . . . . . . . 75 General Notes on Timing Parameters . . . . . . . . . . . . 75 Clock Characteristics and Timings . . . . . . . . . . . . . . . . 76 Clock Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 Ext Reference Crystal/Clock w/PLL Circuit Enabled 77 Low-Power Mode Timings . . . . . . . . . . . . . . . . . . . . . . 78 RS Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79 XF, BIO, and MP/MC Timings . . . . . . . . . . . . . . . . . . . 80 Timing Event Manager Interface . . . . . . . . . . . . . . . . . . 81 PWM Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81 Capture and QEP Timings . . . . . . . . . . . . . . . . . . . . . . 82 Interrupt Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 General-Purpose Input/Output Timings . . . . . . . . . . . 84 SPI Master Mode Timing Parameters . . . . . . . . . . . . . 85 SPI Slave Mode Timing Parameters . . . . . . . . . . . . . . . 89 External Memory Interface Read Timings . . . . . . . . . . 93 External Memory Interface Write Timings . . . . . . . . . . 95 External Memory Interface Ready-on-Read . . . . . . . . 97 External Memory Interface Ready-on-Write . . . . . . . . 98 10-Bit Dual Analog-to-Digital Converter (ADC) . . . . . . 99 ADC Operating Frequency . . . . . . . . . . . . . . . . . . . . . 99 ADC Input Pin Circuit . . . . . . . . . . . . . . . . . . . . . . . . . 100 Internal ADC Module Timings . . . . . . . . . . . . . . . . . . 101 Flash EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102 Programming Operation . . . . . . . . . . . . . . . . . . . . . . . 102 Erase Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102 Flash-Write Operation . . . . . . . . . . . . . . . . . . . . . . . . 102 Register File Compilation . . . . . . . . . . . . . . . . . . . . . . . 103 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

2 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

TMS320F243, TMS320F241

DSP CONTROLLERS

SPRS064B ± DECEMBER 1997 ± REVISED FEBRUARY 1999

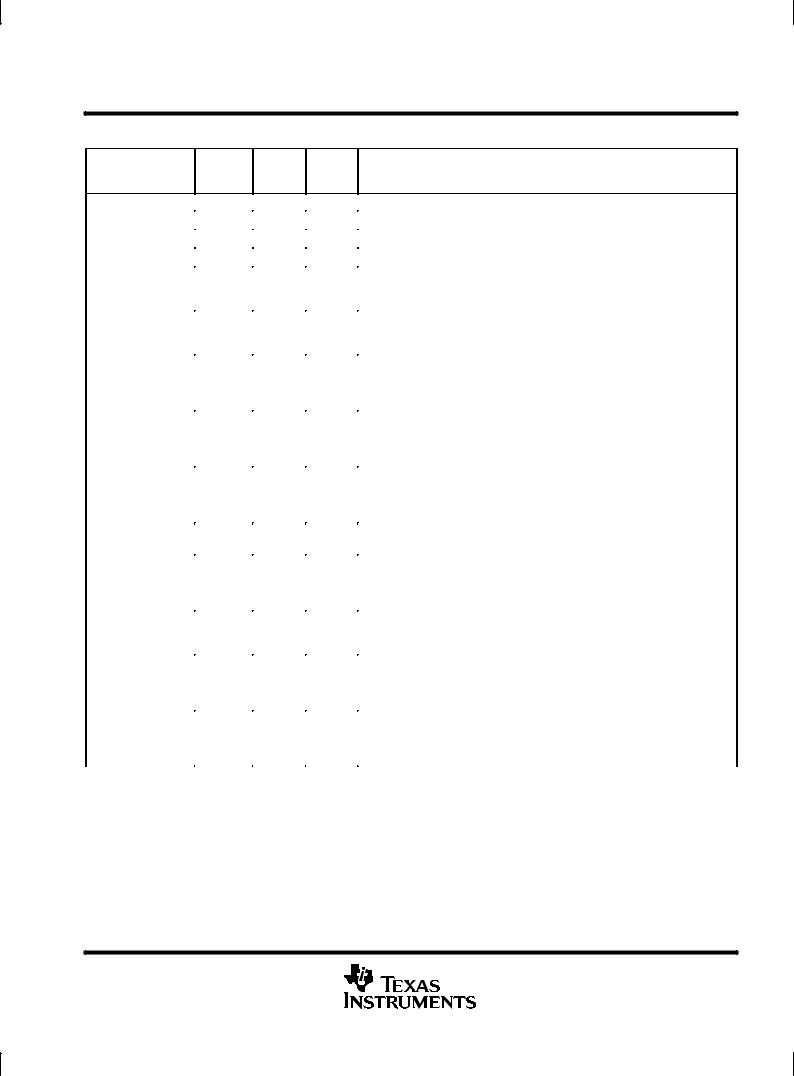

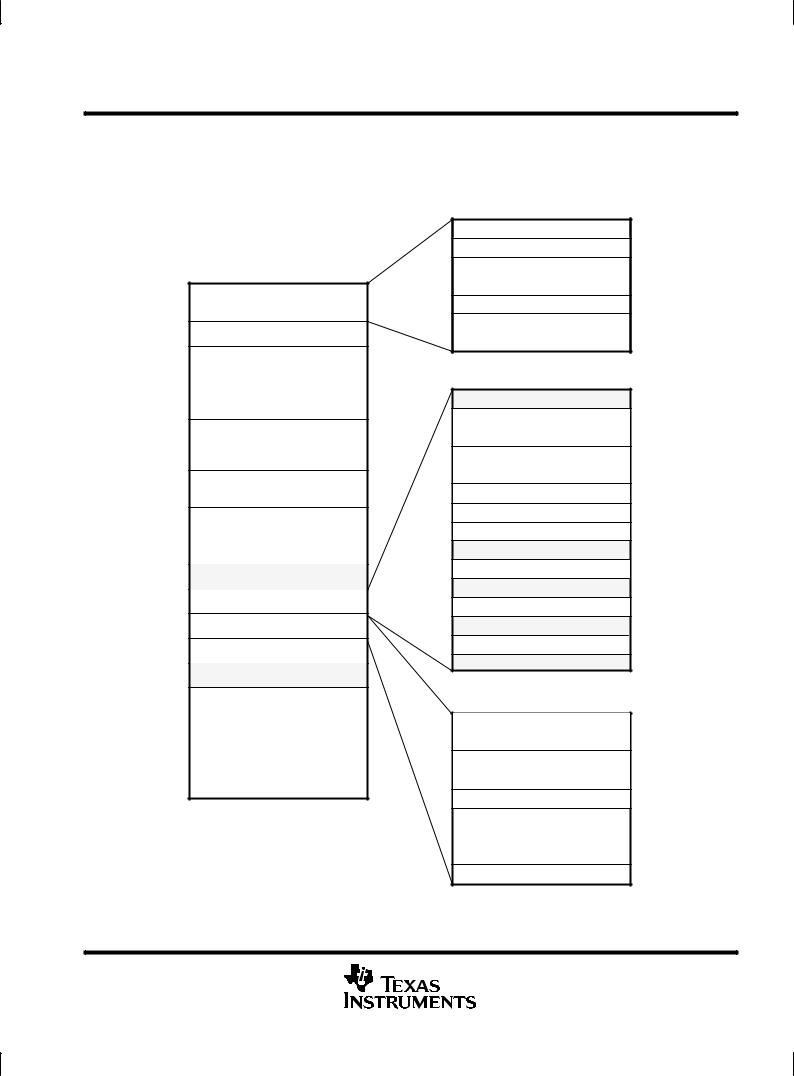

device features

Table 1 and Table 2 provide a comparison of the features of the 'F243 and 'F241. See the functional block diagram for '24x peripherals and memory.

Table 1. Hardware Features of the TMS320x24x DSP Controllers

|

ON-CHIP MEMORY (WORDS) |

|

|

|

||

|

|

|

|

|

|

|

|

RAM |

|

EXTERNAL |

POWER |

CYCLE |

|

|

|

|

||||

TMS320x24x |

|

CONFIGURABLE |

SUPPLY |

TIME |

||

DATA SPACE |

MEMORY |

|||||

DEVICES |

DATA / PROG SPACE |

(V) |

(ns) |

|||

|

INTERFACE |

|||||

|

|

|

|

|

||

|

(B1 RAM - 256 WORDS) |

(B0 RAM) |

|

|

|

|

|

(B2 RAM - 32 WORDS) |

|

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

TMS320F243 |

288 |

256 |

√ |

5 |

50 |

|

|

|

|||||

TMS320F241 |

± |

|||||

|

|

|

|

|||

Table 2. Device Specifications of the TMS320x24x DSP Controllers

|

ON-CHIP MEMORY (WORDS) |

|

|

|

|

PACKAGE |

||

TMS320x24x |

|

|

ADC |

PERIPHERALS |

|

|||

|

FLASH |

|

||||||

ROM |

GPIO |

TYPE |

||||||

DEVICES |

EEPROM |

CHANNELS |

|

|

||||

|

|

|

|

PIN COUNT |

||||

|

|

|

|

|

|

|

||

|

PROG |

PROG |

|

CAN |

SPI |

|

|

|

|

|

|

|

|

|

|

|

|

TMS320F243 |

± |

8K |

8 |

√ |

√ |

32 |

PGE |

|

144-PQFP |

||||||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

TMS320F241 |

± |

8K |

8 |

√ |

√ |

26 |

FN 68-PLCC |

|

PG 64-PQFP |

||||||||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

3 |

TMS320F243, TMS320F241

DSP CONTROLLERS

SPRS064B ± DECEMBER 1997 ± REVISED FEBRUARY 1999

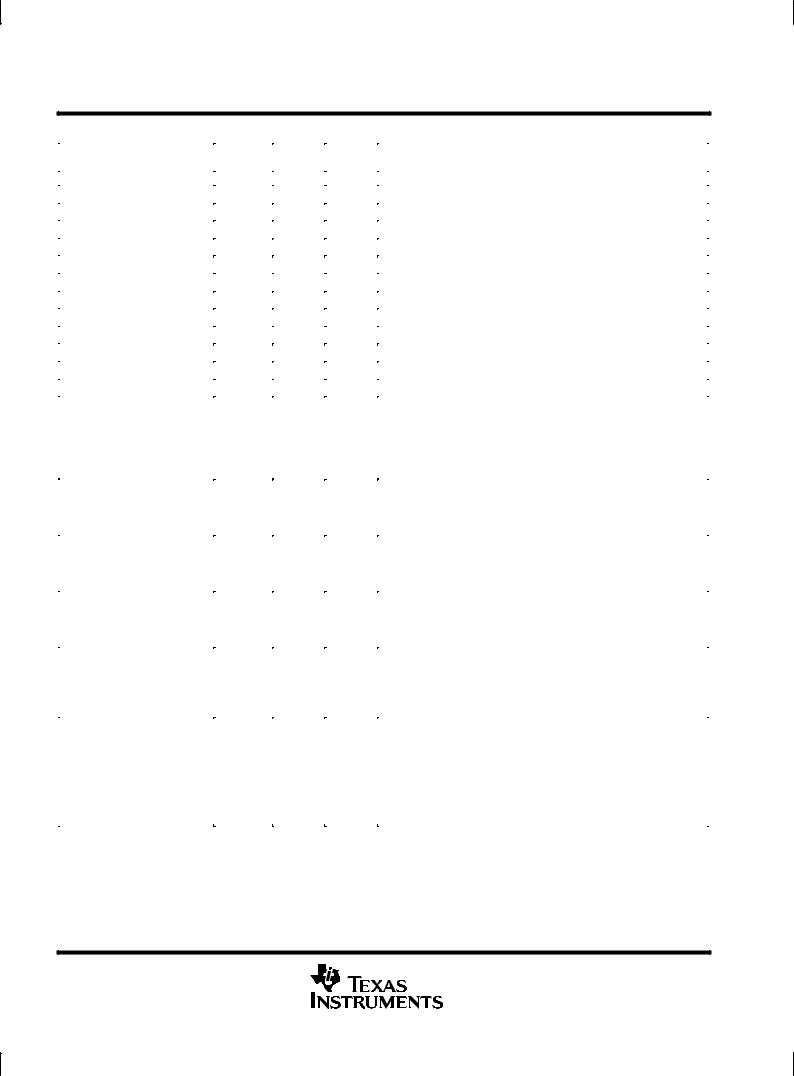

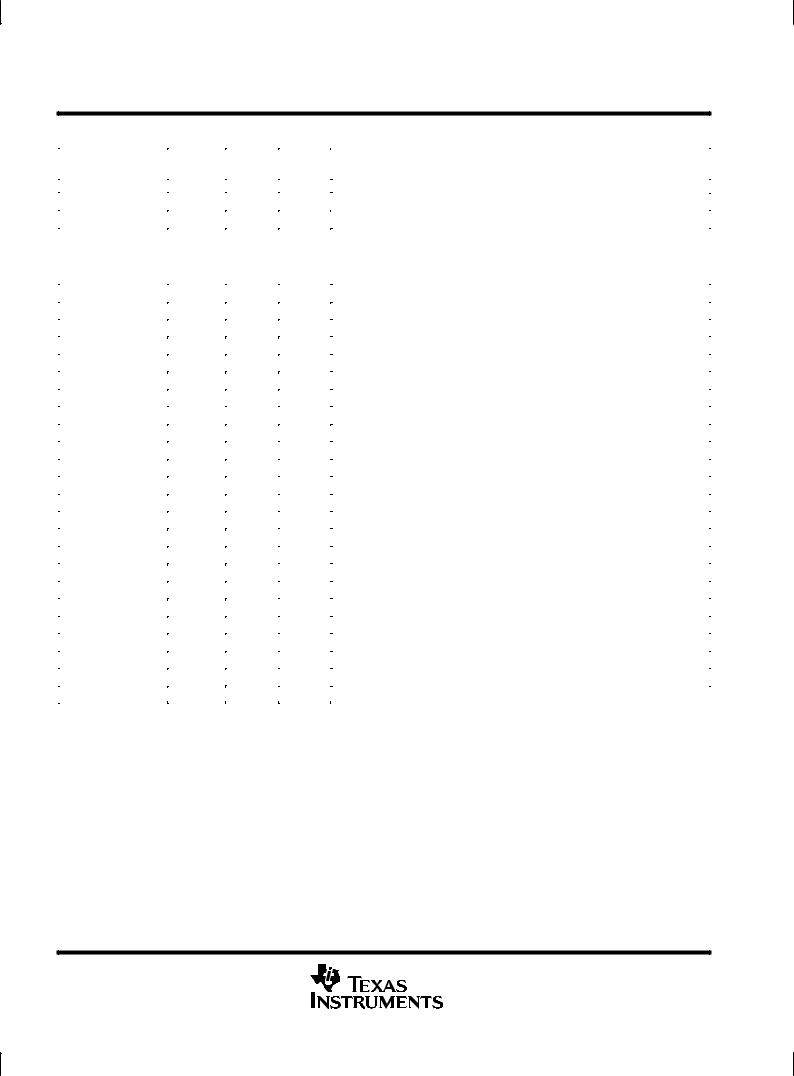

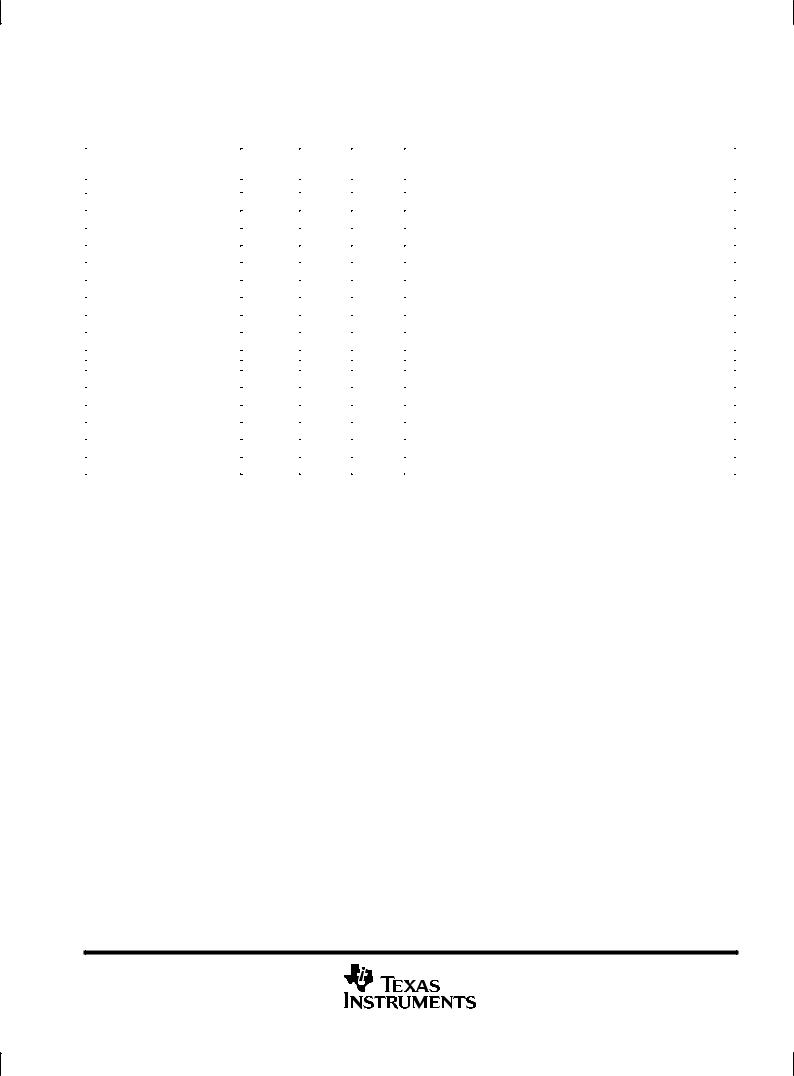

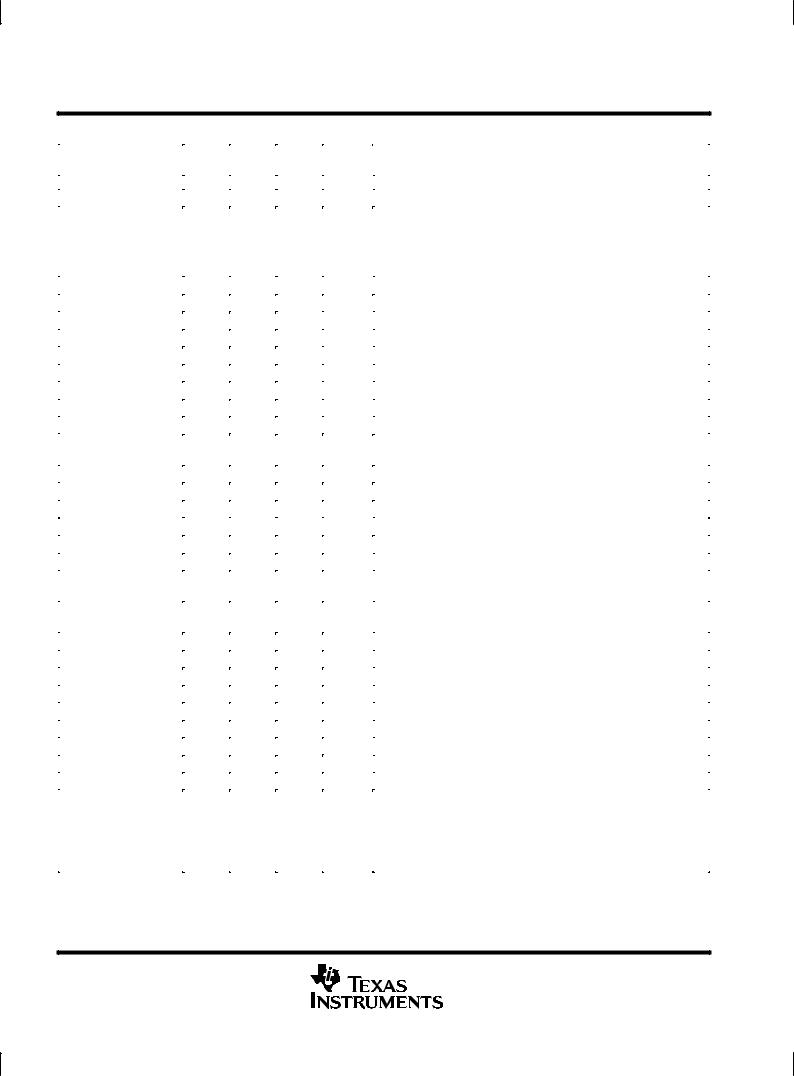

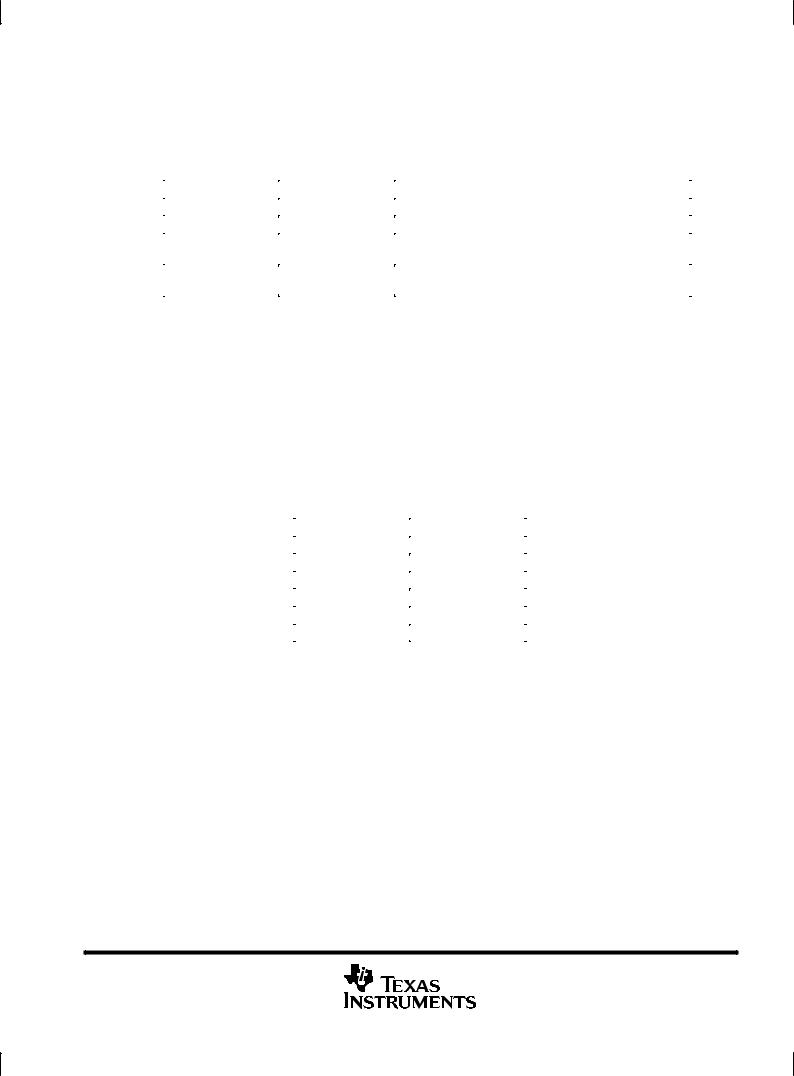

PGE PACKAGE²

(TOP VIEW)

|

|

|

|

|

ADCIN05 |

|

ADCIN06 |

|

V |

|

V |

|

NC |

|

ADCIN07 |

NC V |

|

NC |

|

V |

NC NC |

|

NC |

|

V |

|

T1PWM/T1CMP/IOPB4 |

V |

|

T2PWM/T2CMP/IOPB5 |

|

V |

_VISOE |

|

V |

|

V |

|

CAP1/QEP0/IOPA3 |

STRB |

|

CAP2/QEP1/IOPA4 |

BR |

|

CAP3/IOPA5 |

RD |

|

V |

|

CLKOUT/IOPD0 |

|

CANTX/IOPC6 |

R/W CANRX/IOPC7 |

WE V |

DS V |

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

REFLO |

|

REFHI |

|

|

|

|

|

|

|

|

|

|

|

|

CCA |

|

|

|

|

|

SSA |

|

|

|

|

|

|

|

|

|

|

|

|

SSO |

|

|

|

|

|

SSO |

|

|

|

|

|

SS |

|

|

|

|

DD SSO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSO |

|

|

|

|

DDO |

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

144 |

|

143 |

|

|

142 |

|

141 |

|

140 |

|

|

139 |

|

|

138 |

|

|

137 |

|

|

136 |

|

|

135 |

|

|

134 |

|

|

133 |

|

|

132 |

|

|

131 |

|

|

130 |

|

129 |

|

|

128 |

|

127 |

|

|

126 |

|

|

125 |

|

|

124 |

|

|

123 |

|

|

122 |

|

|

121 |

|

|

120 |

|

|

119 |

|

|

118 |

|

|

117 |

|

|

116 |

|

|

115 |

|

|

114 |

|

|

113 |

|

|

112 |

111 |

|

|

110 |

|

|

109 |

|

|

|

|

VSSO |

|||||||||||||||||||||||||||||||||||||||

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

NC |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

108 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

NC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

107 |

|

|

PS |

|

|

|||||

ADCIN04 |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

106 |

|

|

VDDO |

||||||

ADCIN03 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

105 |

|

|

IS |

|

|

|

|||

NC |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

104 |

|

|

A0 |

||||||

ADCIN02 |

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

103 |

|

|

A1 |

||||||

NC |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

102 |

|

|

PWM1/IOPA6 |

||||||

ADCIN01 |

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

101 |

|

|

A2 |

||||||

NC |

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

PWM2/IOPA7 |

||||||

ADCIN00 |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

99 |

|

|

A3 |

|||||||

NC |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

98 |

|

|

PWM3/IOPB0 |

|||||||

DNC |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

97 |

|

|

DNC |

|||||||

NC |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

96 |

|

|

PWM4/IOPB1 |

|||||||

VSSO |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

95 |

|

|

A4 |

|||||||

VSSO |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

94 |

|

|

PWM5/IOPB2 |

|||||||

VSS |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

93 |

|

|

A5 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

VDD |

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TMS320F243 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

92 |

|

|

A6 |

|||||||||||||||||||||||||||||

ENA_144 |

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(144-Pin QFP) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

91 |

|

|

PWM6/IOPB3 |

||||||||||||||||||||||||||||||||||||

RS |

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

90 |

|

|

A7 |

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

IOPD2 |

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

89 |

|

|

PDPINT |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

IOPD3 |

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

88 |

|

|

A8 |

|||||||

TCK |

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

87 |

|

|

TCLKIN/IOPB7 |

|||||||

IOPD4 |

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86 |

|

|

A9 |

|||||||

TDI |

|

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

85 |

|

|

TDIR/IOPB6 |

|||||||

IOPD5 |

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

84 |

|

|

A10 |

|||||||

TDO |

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

83 |

|

|

XINT1/IOPA2 |

|||||||

IOPD6 |

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

82 |

|

|

A11 |

|||||||

TMS |

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

81 |

|

|

XINT2/ADCSOC/IOPD1 |

|||||||

IOPD7 |

|

29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

80 |

|

|

A12 |

|||||||

TRST |

|

30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

79 |

|

|

NMI |

|||||||

VIS_CLK |

|

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

78 |

|

|

A13 |

|||||||

V |

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

77 |

|

|

VCCP/WDDIS |

|||||||

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A14 |

||||

D0 |

|

33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

76 |

|

|

||||||||

V |

|

34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

75 |

|

|

VDDO |

|||||||

DDO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A15 |

||||

D1 |

|

35 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74 |

|

|

||||||||

V |

|

36 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

73 |

|

|

VSSO |

|||||||

SSO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

38 |

|

|

39 |

|

|

40 |

|

|

41 |

|

|

42 |

|

|

43 |

|

|

44 |

|

|

45 |

|

|

46 |

|

|

47 |

|

|

48 |

|

|

49 |

|

|

50 |

|

|

51 |

|

|

52 |

|

|

53 |

|

|

54 |

|

|

55 |

|

|

56 |

|

|

57 |

|

|

58 |

|

|

59 |

|

|

60 |

|

|

61 |

|

|

62 |

|

|

63 |

|

|

64 |

|

|

65 |

|

|

66 |

|

|

67 |

|

|

68 |

|

|

69 |

70 |

|

|

71 |

|

|

72 |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSO |

|

|

|

|

|

DDO |

|

SSO |

|

XTAL1/CLKIN |

|

|

|

|

MP/MC |

|

|

|

|

|

EMU0 |

|

|

|

|

EMU1/OFF |

|

|

|

|

|

XF/IOPC0 |

|

|

|

|

|

SS |

|

|

|

|

|

DD |

|

|

|

|

BIO/IOPC1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SPISIMO/IOPC2 |

|

|

|

|

SPISOMI/IOPC3 |

|

|

|

|

SPICLK/IOPC4 |

|

|

|

|

|

SPISTE/IOPC5 |

|

|

|

|

PMT |

|

|

|

|

SSO |

|

|

|

|

DDO |

|

|

|

|

||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

XTAL2 |

|

READY |

|

|

|

|

|

|

|

|

|

|

|

D5 |

|

|

|

|

|

D6 |

|

|

|

|

|

D7 |

|

SCITXD/IOPA0 |

|

D8 |

|

SCIRXD/IOPA1 |

|

|

|

|

D10 |

|

|

|

|

|

|

D12 |

|

D13 |

|

D14 |

|

|

|

D15 |

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

D2 |

|

|

|

|

|

|

|

D3 |

|

D4 |

|

|

|

V |

|

V |

|

|

|

|

D9 |

|

|

D11 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

V |

|

V |

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

V |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|