Texas instruments TMS320F28031, TMS320F28032, TMS320F28034, TMS320F28033, TMS320F28035 Data Manual

...

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

www.ti.com |

SPRS584D –APRIL 2009 –REVISED JUNE 2010 |

Piccolo Microcontrollers

Check for Samples: TMS320F28030, TMS320F28031, TMS320F28032, TMS320F28033, TMS320F28034, TMS320F28035

1 TMS320F2803x ( Piccolo™ ) MCUs

1.1Features

•Highlights

–High-Efficiency 32-Bit CPU ( TMS320C28x™ )

–60-MHz Device

–Single 3.3-V Supply

–Integrated Power-on and Brown-out Resets

–Two Internal Zero-pin Oscillators

–Up to 45 Multiplexed GPIO Pins

–Three 32-Bit CPU Timers

–On-Chip Flash, SARAM, OTP Memory

–Code-Security Module

–Serial Port Peripherals (SCI/SPI/I2C/LIN/eCAN)

–Enhanced Control Peripherals

•Enhanced Pulse Width Modulator (ePWM)

•High-Resolution PWM (HRPWM)

•Enhanced Capture (eCAP)

•Enhanced Quadrature Encoder Pulse (eQEP)

•Analog-to-Digital Converter (ADC)

•On-Chip Temperature Sensor

•Comparator

–64-Pin and 80-Pin Packages

•High-Efficiency 32-Bit CPU ( TMS320C28x™ )

–60 MHz (16.67-ns Cycle Time)

–16 x 16 and 32 x 32 MAC Operations

–16 x 16 Dual MAC

–Harvard Bus Architecture

–Atomic Operations

–Fast Interrupt Response and Processing

–Unified Memory Programming Model

–Code-Efficient (in C/C++ and Assembly)

•Programmable Control Law Accelerator (CLA)

–32-Bit Floating-Point Math Accelerator

–Executes Code Independently of the Main CPU

•Low Device and System Cost:

–Single 3.3-V Supply

–No Power Sequencing Requirement

–Integrated Power-on Reset and Brown-out Reset

–Low Power

–No Analog Support Pins

•Clocking:

–Two Internal Zero-pin Oscillators

–On-Chip Crystal Oscillator/External Clock Input

–Dynamic PLL Ratio Changes Supported

–Watchdog Timer Module

–Missing Clock Detection Circuitry

•Up to 45 Individually Programmable, Multiplexed GPIO Pins With Input Filtering

•Peripheral Interrupt Expansion (PIE) Block That Supports All Peripheral Interrupts

•Three 32-Bit CPU Timers

•Independent 16-Bit Timer in Each ePWM Module

•On-Chip Memory

–Flash, SARAM, OTP, Boot ROM Available

•128-Bit Security Key/Lock

–Protects Secure Memory Blocks

–Prevents Firmware Reverse Engineering

•Serial Port Peripherals

–One SCI (UART) Module

–Two SPI Modules

–One Inter-Integrated-Circuit (I2C) Bus

–One Local Interconnect Network (LIN) Bus

–One Enhanced Controller Area Network (eCAN) Bus

•Advanced Emulation Features

–Analysis and Breakpoint Functions

–Real-Time Debug via Hardware

•2803x Packages

–64-Pin PAG Thin Quad Flatpack (TQFP)

–80-Pin PN Low-Profile Quad Flatpack (LQFP)

•Community Resources

–TI E2E Community

–TI Embedded Processors Wiki

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Piccolo, TMS320C28x, C28x, TMS320C2000, Code Composer Studio, XDS510 are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

PRODUCTION DATA information is |

current as of publication date. |

Copyright © 2009–2010, Texas Instruments Incorporated |

Products conform to specifications |

per the terms of the Texas |

|

Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

SPRS584D–APRIL 2009 –REVISED JUNE 2010 |

www.ti.com |

1.2Description

The F2803x Piccolo™ family of microcontrollers provides the power of the C28x™ core and Control Law Accelerator (CLA) coupled with highly integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code, as well as providing a high level of analog integration.

An internal voltage regulator allows for single rail operation. Enhancements have been made to the HRPWM module to allow for dual-edge control (frequency modulation). Analog comparators with internal 10-bit references have been added and can be routed directly to control the PWM outputs. The ADC

converts from 0 to 3.3-V fixed full scale range and supports ratio-metric VREFHI/VREFLO references. The ADC interface has been optimized for low overhead/latency.

1.3Getting Started

This section gives a brief overview of the steps to take when first developing for a C28x device. For more detail on each of these steps, see the following:

•Getting Started With TMS320C28x Digital Signal Controllers (literature number SPRAAM0).

•C2000 Getting Started Website (http://www.ti.com/c2000getstarted)

•TMS320F28x MCU Development and Experimenter'sKits (http://www.ti.com/f28xkits)

2 |

TMS320F2803x ( Piccolo™ ) MCUs |

Copyright © 2009–2010, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

www.ti.com |

|

|

|

SPRS584D –APRIL 2009 –REVISED JUNE 2010 |

|||

1 |

TMS320F2803x ( Piccolo™ ) MCUs .................. |

1 |

|

4.9 |

High-Resolution PWM (HRPWM) .................. |

78 |

|

|

1.1 |

Features .............................................. |

1 |

|

4.10 Enhanced Capture Module (eCAP1) ............... |

79 |

|

|

1.2 |

Description ........................................... |

2 |

|

4.11 Enhanced Quadrature Encoder Pulse (eQEP) ..... |

81 |

|

|

1.3 |

Getting Started ....................................... |

2 |

|

4.12 |

JTAG Port .......................................... |

83 |

2 |

Introduction .............................................. |

4 |

|

4.13 |

GPIO MUX |

84 |

|

|

|

|

|

|

|||

|

2.1 |

Pin Assignments ..................................... |

5 |

5 |

Device Support ......................................... |

89 |

|

|

2.2 |

Signal Descriptions .................................. |

7 |

|

5.1 |

Device and Development Support Tool |

|

3 |

Functional Overview .................................. |

14 |

|

|

Nomenclature ....................................... |

89 |

|

|

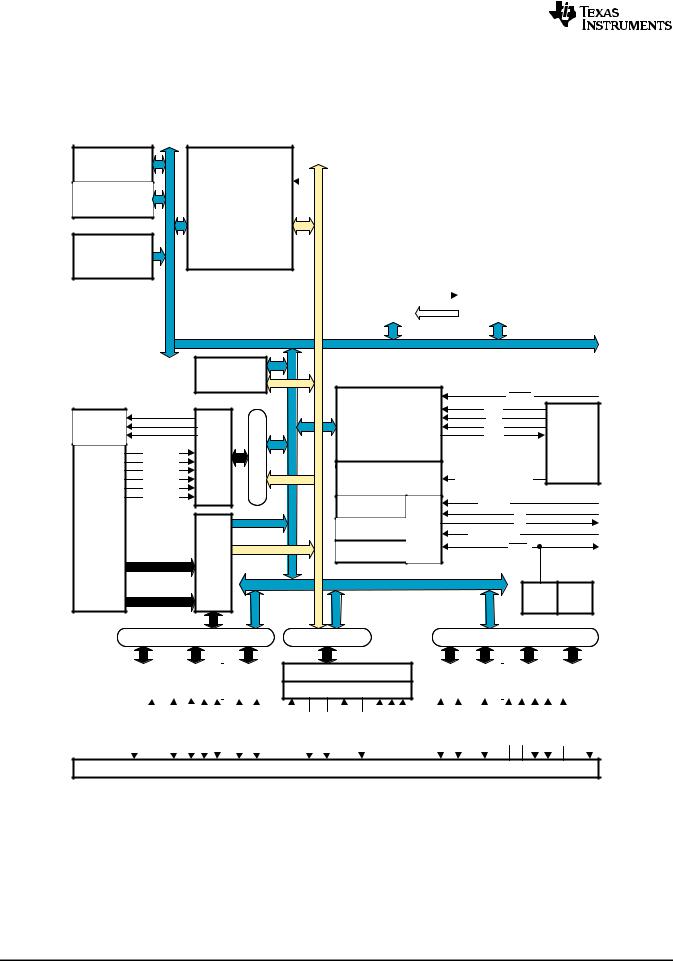

3.1 |

Block Diagram ...................................... |

14 |

|

5.2 |

Related Documentation ............................. |

91 |

|

3.2 |

Memory Maps ...................................... |

15 |

6 |

Electrical Specifications ............................. |

93 |

|

|

3.3 |

Brief Descriptions ................................... |

22 |

|

6.1 |

Absolute Maximum Ratings ........................ |

93 |

|

3.4 |

Register Map ....................................... |

30 |

|

6.2 |

Recommended Operating Conditions .............. |

93 |

|

3.5 |

Device Emulation Registers ........................ |

31 |

|

6.3 |

Electrical Characteristics ........................... |

94 |

|

3.6 |

Interrupts ............................................ |

32 |

|

6.4 |

Current Consumption ............................... |

95 |

|

3.7 |

VREG/BOR/POR ................................... |

36 |

|

6.5 |

Thermal Design Considerations .................... |

99 |

|

3.8 |

System Control ..................................... |

38 |

|

6.6 |

Emulator Connection Without Signal Buffering for |

|

|

3.9 |

Low-power Modes Block ........................... |

46 |

|

|

the MCU ............................................ |

99 |

4 |

Peripherals .............................................. |

47 |

|

6.7 |

Timing Parameter Symbology ..................... |

100 |

|

|

4.1 |

Control Law Accelerator (CLA) Overview .......... |

47 |

|

6.8 |

Clock Requirements and Characteristics ......... |

102 |

|

4.2 |

Analog Block ........................................ |

50 |

|

6.9 |

Power Sequencing ................................ |

103 |

|

4.3 |

Serial Peripheral Interface (SPI) Module ........... |

56 |

|

6.10 |

General-Purpose Input/Output (GPIO) ............ |

105 |

|

4.4 |

Serial Communications Interface (SCI) Module .... |

59 |

|

6.11 |

Enhanced Control Peripherals .................... |

112 |

|

4.5 |

Local Interconnect Network (LIN) .................. |

62 |

|

6.12 |

Detailed Descriptions .............................. |

129 |

|

4.6 |

Enhanced Controller Area Network (eCAN) Module |

|

|

6.13 |

Flash Timing ....................................... |

130 |

|

|

...................................................... |

65 |

7 |

C-to-D Revision History ............................. |

132 |

|

|

4.7 |

Inter-Integrated Circuit (I2C) ........................ |

69 |

8 |

B-to-C Revision History ............................. |

134 |

|

|

4.8 |

Enhanced PWM Modules (ePWM1/2/3/4/5/6/7) .... |

71 |

9 |

Thermal/Mechanical Data .......................... |

137 |

|

|

|

|

|

|

|

|

|

Copyright © 2009–2010, Texas Instruments Incorporated |

Contents |

3 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

SPRS584D–APRIL 2009 –REVISED JUNE 2010 |

www.ti.com |

2 Introduction

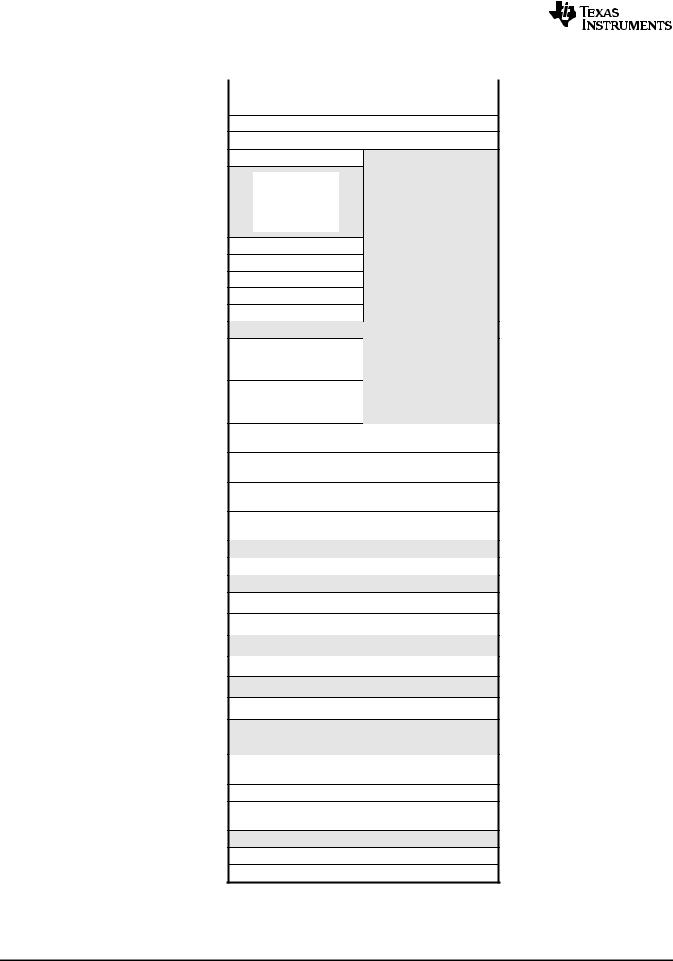

Table 2-1 lists the features of the TMS320F2803x devices.

Table 2-1. Hardware Features

FEATURE |

TYPE(1) |

28030 |

28031 |

28032 |

28033 |

28034 |

28035 |

||||||||||||||

|

|

|

|

(60 MHz) |

(60 MHz) |

(60 MHz) |

(60 MHz) |

(60 MHz) |

(60 MHz) |

||||||||||||

|

|

|

|

64-Pin |

|

80-Pin |

64-Pin |

|

80-Pin |

64-Pin |

|

80-Pin |

64-Pin |

|

80-Pin |

64-Pin |

|

80-Pin |

64-Pin |

|

80-Pin |

Package Type |

|

|

PAG |

|

PN |

PAG |

|

PN |

PAG |

|

PN |

PAG |

|

PN |

PAG |

|

PN |

PAG |

|

PN |

|

|

|

|

|

TQFP |

|

LQFP |

TQFP |

|

LQFP |

TQFP |

|

LQFP |

TQFP |

|

LQFP |

TQFP |

|

LQFP |

TQFP |

|

LQFP |

Instruction cycle |

– |

16.67 ns |

16.67 ns |

16.67 ns |

16.67 ns |

16.67 ns |

16.67 ns |

||||||||||||||

Control Law Accelerator |

0 |

|

No |

|

No |

|

No |

|

Yes |

|

No |

|

Yes |

||||||||

On-chip flash (16-bit word) |

– |

|

16K |

|

32K |

|

32K |

|

32K |

|

64K |

|

64K |

||||||||

On-chip SARAM (16-bit word) |

– |

|

6K |

|

8K |

|

10K |

|

10K |

|

10K |

|

10K |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Code security for on-chip |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||||

flash/SARAM/OTP blocks |

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Boot ROM (8K x 16) |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||||

One-time programmable (OTP) ROM |

– |

|

1K |

|

1K |

|

1K |

|

1K |

|

1K |

|

1K |

||||||||

(16-bit word) |

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

ePWM outputs |

|

1 |

12 |

|

14 |

12 |

|

14 |

12 |

|

14 |

12 |

|

14 |

12 |

|

14 |

12 |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

eCAP inputs |

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

eQEP modules |

|

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|||||||

Watchdog timer |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||||

|

|

MSPS |

|

|

2.0 |

|

2.0 |

|

4.6 |

|

4.6 |

|

4.6 |

|

4.6 |

||||||

|

|

Conversion Time |

|

500.00 ns |

500.00 ns |

216.67 ns |

216.67 ns |

216.67 ns |

216.67 ns |

||||||||||||

12-Bit ADC |

|

Channels |

3 |

14 |

|

16 |

14 |

|

16 |

14 |

|

16 |

14 |

|

16 |

14 |

|

16 |

14 |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Temperature Sensor |

|

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Dual |

|

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||

|

|

Sample-and-Hold |

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32-Bit CPU timers |

– |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

||||||||

HiRES ePWM Channels |

1 |

|

– |

|

– |

6 |

|

7 |

6 |

|

7 |

6 |

|

7 |

6 |

|

7 |

||||

Comparators with Integrated DACs |

0 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

Inter-integrated circuit (I2C) |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Enhanced Controller Area Network |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

||||||||

(eCAN) |

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Local Interconnect Network (LIN) |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

||||||||

Serial Peripheral Interface (SPI) |

1 |

1 |

|

2 |

1 |

|

2 |

1 |

|

2 |

1 |

|

2 |

1 |

|

2 |

1 |

|

2 |

||

Serial Communications Interface |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

||||||||

(SCI) |

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O pins |

|

GPIO |

– |

33 |

|

45 |

33 |

|

45 |

33 |

|

45 |

33 |

|

45 |

33 |

|

45 |

33 |

|

45 |

(shared) |

|

AIO |

– |

|

6 |

|

6 |

|

6 |

|

6 |

|

6 |

|

6 |

||||||

|

|

|

|

|

|

|

|

||||||||||||||

External interrupts |

– |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

||||||||

Supply voltage (nominal) |

– |

3.3 V |

3.3 V |

3.3 V |

3.3 V |

3.3 V |

3.3 V |

||||||||||||||

|

|

T: –40°C to 105°C |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||

Temperature |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S: –40°C to 125°C |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|||||||

options |

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q: –40°C to 125°C(2) |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||

Product status(3) |

– |

|

TMS |

|

TMS |

|

TMS |

|

TMS |

|

TMS |

|

TMS |

||||||||

(1)A type change represents a major functional feature difference in a peripheral module. Within a peripheral type, there may be minor differences between devices that do not affect the basic functionality of the module. These device-specific differences are listed in the TMS320x28xx, 28xxx DSP Peripheral Reference Guide (literature number SPRU566) and in the peripheral reference guides.

(2)"Q" refers to Q100 qualification for automotive applications.

(3)See Section 5.1 , Device and Development Support Tool Nomenclature, for descriptions of device stages. The "TMS" product status denotes a fully qualified production device.

4 |

Introduction |

Copyright © 2009–2010, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

www.ti.com |

SPRS584D –APRIL 2009 –REVISED JUNE 2010 |

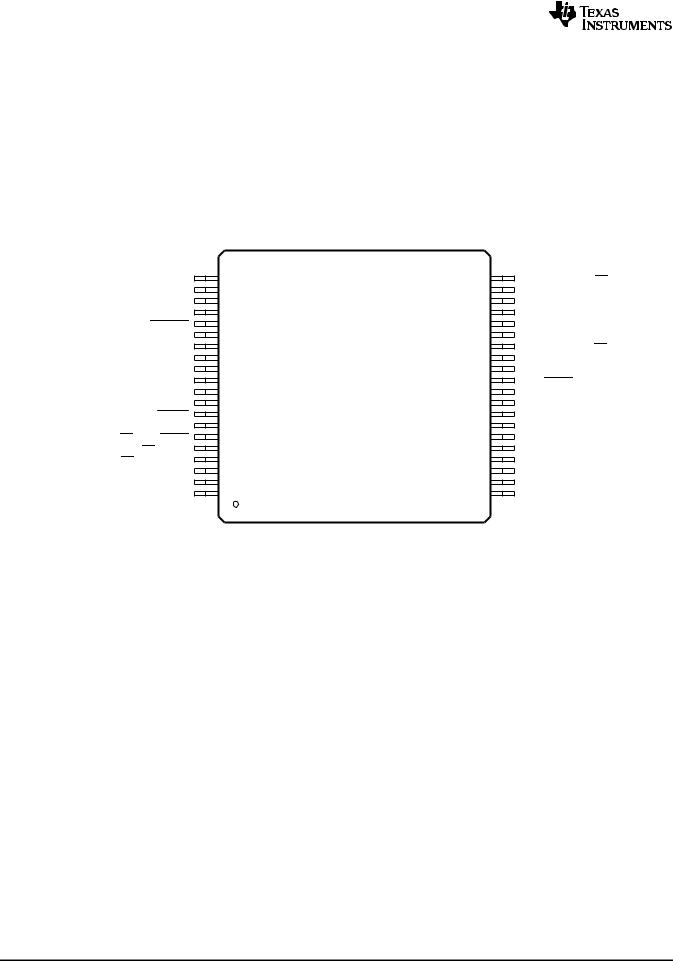

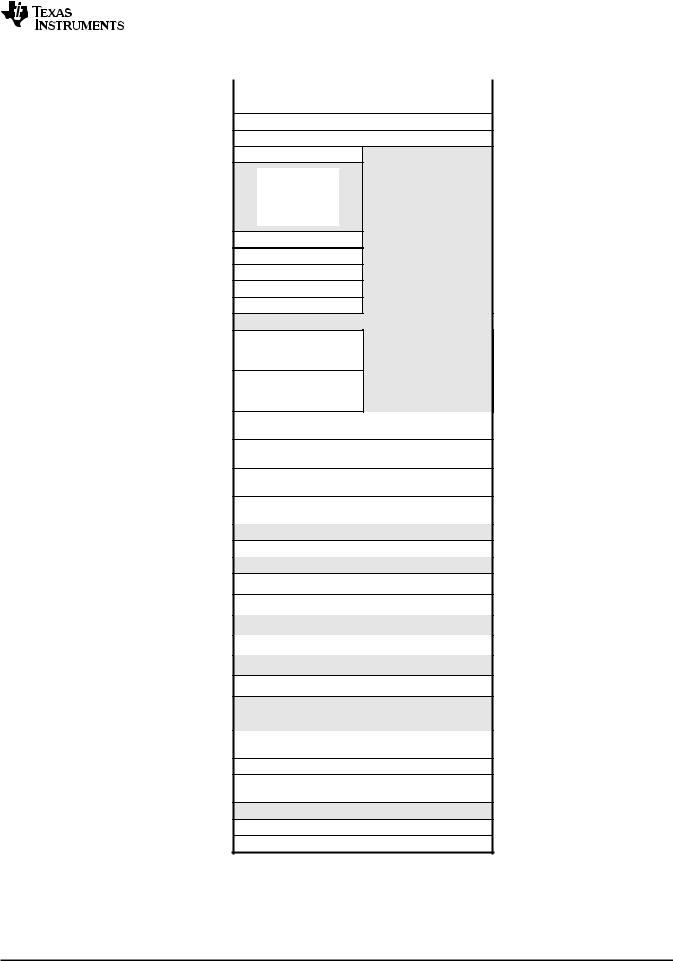

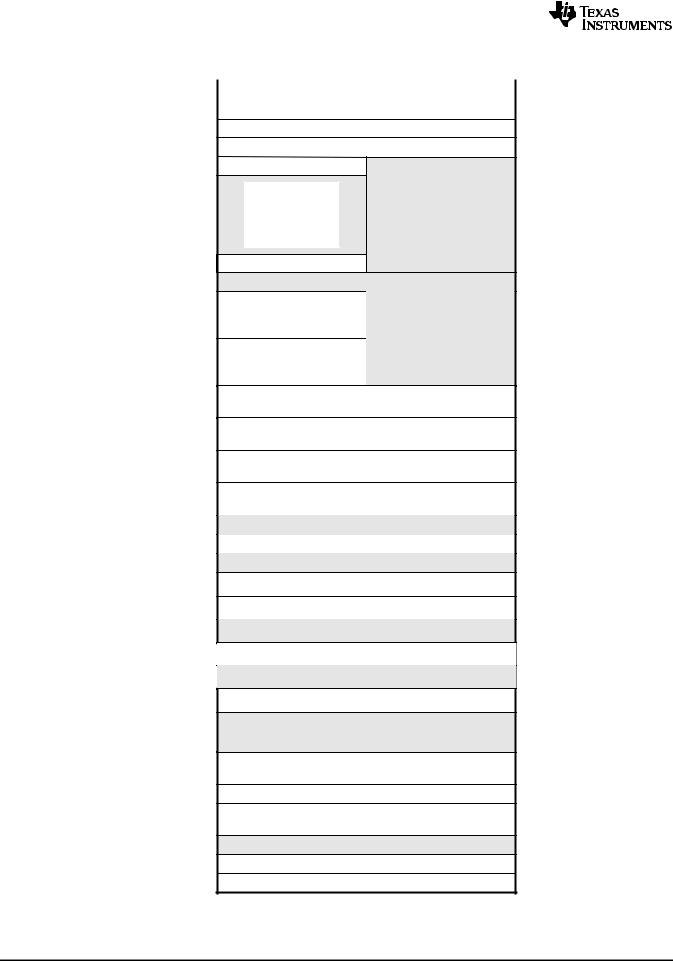

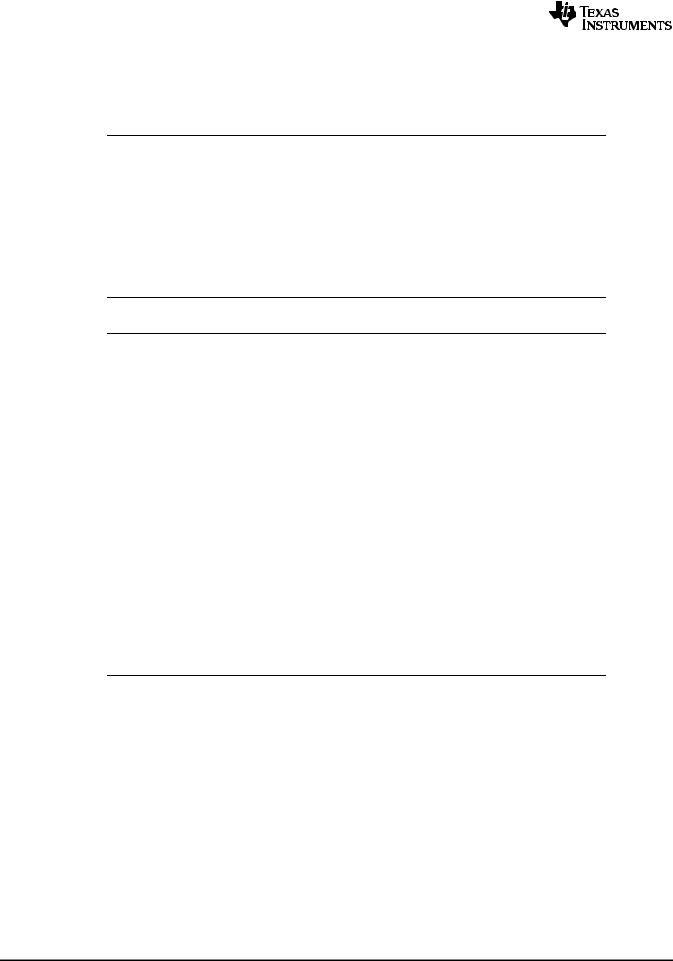

2.1Pin Assignments

Figure 2-1 shows the 64-pin PAG Thin Quad Flatpack (TQFP) pin assignments. Figure 2-2 shows the 80-pin PN Low-Profile Quad Flatpack (LQFP) pin assignments.

|

|

|

|

|

|

|

|

GPIO36/TMS |

GPIO35/TDI |

|

GPIO37/TDO |

|

GPIO38/TCK/XCLKIN |

|

GPIO19/XCLKIN/SPISTEA/LINRXA/ECAP1 |

V |

V |

X1 |

X2 |

GPIO6/EPWM4A/EPWMSYNCI/EPWMSYNCO |

GPIO7/EPWM4B/SCIRXDA |

|

GPIO12/TZ1/SCITXDA |

|

GPIO16/SPISIMOA/TZ2 |

|

GPIO8/EPWM5A/ADCSOCAO |

|

GPIO17/SPISOMIA/TZ3 |

GPIO18/SPICLKA/LINTXA/XCLKOUT |

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD |

|

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

47 |

|

46 |

|

45 |

|

44 |

|

43 |

|

42 |

41 |

|

40 |

39 |

38 |

37 |

36 |

|

35 |

|

34 |

|

33 |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

GPIO11/EPWM6B/LINRXA |

|

|

|

49 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GPIO28/SCIRXDA/SDAA/TZ2 |

||||||||||||

GPIO5/EPWM3B/SPSIMOA/ECAP1 |

|

50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

|

|

|

GPIO9/EPWM5B/LINTXA |

|||||||||||

GPIO4/EPWM3A |

|

51 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

|

|

TEST2 |

|||||||||||

|

|

|

|

|

|

52 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

|

|

|

VDDIO |

|||||||

GPIO10/EPWM6A/ADCSOCBO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

GPIO3/EPWM2B/SPISOMIA/COMP2OUT |

|

53 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

28 |

|

|

|

VSS |

|||||||||||

GPIO2/EPWM2A |

|

54 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

27 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GPIO29/SCITXDA/SCLA/TZ3 |

||||||||||||

GPIO1/EPWM1B/COMP1OUT |

|

55 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

26 |

|

|

|

GPIO30/CANRXA |

|||||||||||

GPIO0/EPWM1A |

|

56 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

|

|

|

GPIO31/CANTXA |

|||||||||||

|

|

VDDIO |

|

57 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|

|

ADCINB7 |

|||||||||

|

|

VSS |

|

58 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

|

ADCINB6/COMP3B/AIO14 |

|||||||||

|

|

VDD |

|

59 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

22 |

|

|

|

ADCINB4/COMP2B/AIO12 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

VREGENZ |

|

|

|

60 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

|

|

|

ADCINB3 |

|||||||

GPIO34/COMP2OUT/COMP3OUT |

|

61 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

|

|

ADCINB2/COMP1B/AIO10 |

|||||||||||

GPIO20/EQEP1A/COMP1OUT |

|

62 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

|

ADCINB1 |

|||||||||||

GPIO21/EQEP1B/COMP2OUT |

|

63 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

|

|

ADCINB0 |

|||||||||||

GPIO24/ECAP1 |

|

64 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

|

|

VSSA/VREFLO |

|||||||||||

|

|

|

|

|

1 |

|

2 |

3 |

4 |

5 |

6 |

|

7 |

8 |

|

9 |

|

10 |

|

11 |

|

12 |

|

13 |

|

14 |

|

15 |

|

16 |

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GPIO22/EQEP1S/LINTXA |

|

GPIO32/SDAA/EPWMSYNCI/ADCSOCAO |

|

GPIO33/SCLA/EPWMSYNCO/ADCSOCBO |

|

GPIO23/EQEP1I/LINRXA |

|

V |

|

V |

|

XRS |

|

TRST |

|

ADCINA7 |

|

ADCINA6/COMP3A/AIO6 |

|

ADCINA4/COMP2A/AIO4 |

|

ADCINA3 |

|

ADCINA2/COMP1A/AIO2 |

|

ADCINA1 |

|

ADCINA0/VREFHI |

|

V |

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD |

|

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DDA |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A.Pin 15: VREFHI and ADCINA0 share the same pin on the 64-pin PAG device and their use is mutually exclusive to one another.

B.Pin 17: VREFLO is always connected to VSSA on the 64-pin PAG device.

Figure 2-1. 2803x 64-Pin PAG TQFP (Top View)

Copyright © 2009–2010, Texas Instruments Incorporated |

Introduction |

5 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

SPRS584D–APRIL 2009 –REVISED JUNE 2010 |

www.ti.com |

GPIO11/EPWM6B/LINRXA

GPIO5/EPWM3B/SPISIMOA/ECAP1

GPIO4/EPWM3A

GPIO40/EPWM7A

GPIO10/EPWM6A/ADCSOCBO

GPIO3/EPWM2B/SPISOMIA/COMP2OUT

GPIO2/EPWM2A

GPIO1/EPWM1B/COMP1OUT

GPIO0/EPWM1A

VDDIO

VSS

VDD

VREGENZ

GPIO34/COMP2OUT/COMP3OUT

GPIO15/TZ1/LINRXA/SPISTEB

GPIO13/TZ2/SPISOMIB

GPIO14/TZ3/LINTXA/SPICLKB

GPIO20/EQEP1A/COMP1OUT

GPIO21/EQEP1B/COMP2OUT

GPIO24/ECAP1/SPISIMOB

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

GPIO36/TMS |

GPIO35/TDI |

|

GPIO37/TDO |

GPIO38/TCK/XCLKIN |

GPIO39 |

|

GPIO19/XCLKIN/SPISTEA/LINRXA/ECAP1 |

V |

V |

X1 |

|

X2 |

GPIO6/EPWM4A/EPWMSYNCI/EPWMSYNCO |

GPIO7/EPWM4B/SCIRXDA |

|

GPIO41/EPWM7B |

|

GPIO12/TZ1/SCITXDA/SPISIMOB |

|

GPIO16/SPISIMOA/TZ2 |

GPIO44 |

|

GPIO25/SPISOMIB |

|

GPIO8/EPWM5A/ADCSOCAO |

|

GPIO17/SPISOMIA/TZ3 |

|

GPIO18/SPICLKA/LINTXA/XCLKOUT |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

DD |

SS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

|

59 |

58 |

|

57 |

|

56 |

55 |

|

54 |

|

53 |

|

52 |

51 |

|

50 |

|

49 |

48 |

|

|

47 |

|

|

46 |

|

45 |

44 |

|

|

43 |

|

|

42 |

41 |

||||||

1 |

|

|

2 |

3 |

|

4 |

|

5 |

6 |

|

7 |

|

8 |

|

9 |

10 |

|

11 |

|

12 |

13 |

|

14 |

|

15 |

|

16 |

17 |

|

18 |

|

19 |

|

20 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GPIO22/EQEP1S/LINTXA |

|

|

|

|

|

GPIO23/EQEP1I/LINRXA |

GPIO42/COMP1OUT |

|

|

|

DD |

|

XRS |

|

TRST |

ADCINA7 |

|

|

|

|

|

|

|

|

|

|

ADCINA1 |

|

|

REFHI |

DDA |

||||||||

|

GPIO32/SDAA/EPWMSYNCI/ADCSOCAO |

|

GPIO33/SCLA/EPWMSYNCO/ADCSOCBO |

|

GPIO43/COMP2OUT |

SS |

|

ADCINA6/COMP3A/AIO6 |

|

ADCINA5 |

ADCINA4/COMP2A/AIO4 |

ADCINA3 |

ADCINA2/COMP1A/AIO2 |

|

ADCINA0 |

||||||||||||||||||||||||

|

|

|

V |

V |

|

|

|

V |

V |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

GPIO28/SCIRXDA/SDAA/TZ2

GPIO9/EPWM5B/LINTXA

TEST2

GPIO26/SPICLKB

VDDIO

VSS

GPIO29/SCITXDA/SCLA/TZ3

GPIO30/CANRXA

GPIO31/CANTXA

GPIO27/SPISTEB

ADCINB7

ADCINB6/COMP3B/AIO14

ADCINB5

ADCINB4/COMP2B/AIO12

ADCINB3

ADCINB2/COMP1B/AIO10

ADCINB1

ADCINB0

VREFLO

VSSA

Figure 2-2. 2803x 80-Pin PN LQFP (Top View)

6 |

Introduction |

Copyright © 2009–2010, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

www.ti.com |

SPRS584D –APRIL 2009 –REVISED JUNE 2010 |

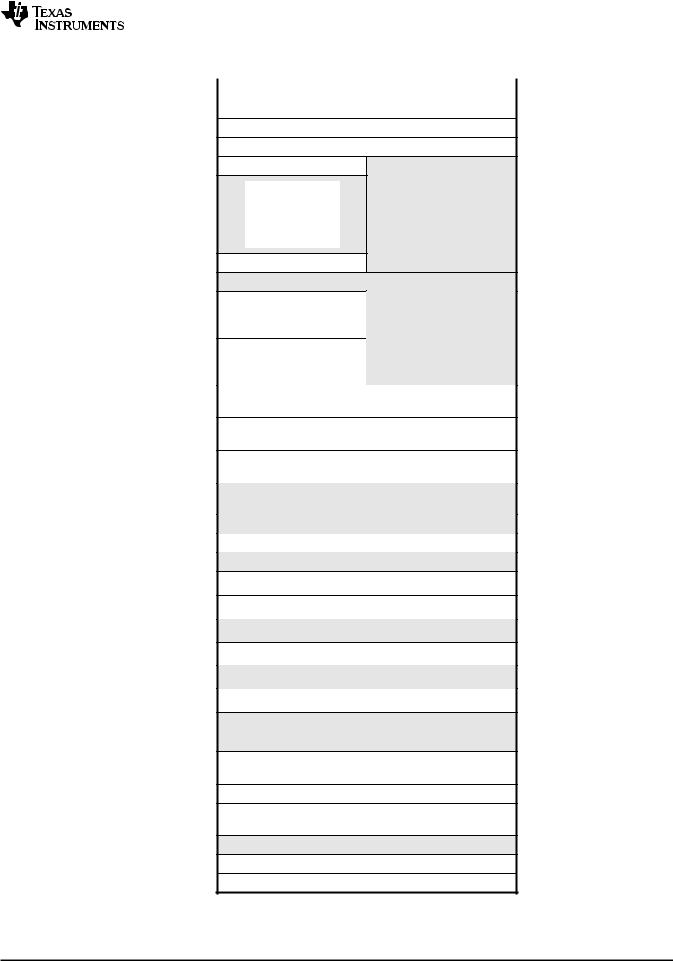

2.2Signal Descriptions

Table 2-2 describes the signals. With the exception of the JTAG pins, the GPIO function is the default at reset, unless otherwise mentioned. The peripheral signals that are listed under them are alternate functions. Some peripheral functions may not be available in all devices. See Table 2-1 for details. Inputs are not 5-V tolerant. All GPIO pins are I/O/Z and have an internal pullup, which can be selectively enabled/disabled on a per-pin basis. This feature only applies to the GPIO pins. The pullups on the PWM pins are not enabled at reset. The pullups on other GPIO pins are enabled upon reset. The AIO pins do not have an internal pullup.

|

|

|

|

|

|

|

Table 2-2. Terminal Functions(1) |

|||

|

|

|

TERMINAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O/Z |

|

DESCRIPTION |

||

|

NAME |

|

PN |

PAG |

|

|||||

|

|

PIN # |

PIN # |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

JTAG |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

JTAG test reset with internal pulldown. |

TRST, |

when driven high, gives the scan |

|

|

|

|

|

|

|

|

system control of the operations of the device. If this signal is not connected or driven |

||

|

|

|

|

|

|

|

|

low, the device operates in its functional mode, and the test reset signals are ignored. |

||

|

|

|

|

|

|

|

|

NOTE: TRST is an active high test pin and must be maintained low at all times during |

||

|

TRST |

|

|

10 |

8 |

I |

|

normal device operation. An external pull-down resistor is required on this pin. The |

||

|

|

|

|

|

|

|

|

value of this resistor should be based on drive strength of the debugger pods |

||

|

|

|

|

|

|

|

|

applicable to the design. A 2.2-kΩ resistor generally offers adequate protection. Since |

||

|

|

|

|

|

|

|

|

this is application-specific, it is recommended that each target board be validated for |

||

|

|

|

|

|

|

|

|

proper operation of the debugger and the application. (↓) |

||

|

TCK |

|

See GPIO38 |

I |

|

See GPIO38. JTAG test clock with internal pullup (↑) |

||||

|

TMS |

|

See GPIO36 |

I |

|

See GPIO36. JTAG test-mode select (TMS) with internal pullup. This serial control |

||||

|

|

|

input is clocked into the TAP controller on the rising edge of TCK. (↑) |

|||||||

|

|

|

|

|

|

|

|

|||

|

TDI |

|

See GPIO35 |

I |

|

See GPIO35. JTAG test data input (TDI) with internal pullup. TDI is clocked into the |

||||

|

|

|

selected register (instruction or data) on a rising edge of TCK. (↑) |

|||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

See GPIO37. JTAG scan out, test data output (TDO). The contents of the selected |

||

|

TDO |

|

See GPIO37 |

O/Z |

|

register (instruction or data) are shifted out of TDO on the falling edge of TCK. (8 mA |

||||

|

|

|

|

|

|

|

|

drive) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FLASH |

||

|

|

|

|

|

|

|

|

|

|

|

|

TEST2 |

|

38 |

30 |

I/O |

|

Test Pin. Reserved for TI. Must be left unconnected. |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLOCK |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

See GPIO18. Output clock derived from SYSCLKOUT. XCLKOUT is either the same |

||

|

|

|

|

|

|

|

|

frequency, one-half the frequency, or one-fourth the frequency of SYSCLKOUT. This |

||

|

XCLKOUT |

|

See GPIO18 |

O/Z |

|

is controlled by bits 1:0 (XCLKOUTDIV) in the XCLK register. At reset, XCLKOUT = |

||||

|

|

|

SYSCLKOUT/4. The XCLKOUT signal can be turned off by setting XCLKOUTDIV |

|||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

to 3. The mux control for GPIO18 must also be set to XCLKOUT for this signal to |

||

|

|

|

|

|

|

|

|

propogate to the pin. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

See GPIO19 and GPIO38. External oscillator input. Pin source for the clock is |

||

|

|

|

|

|

|

|

|

controlled by the XCLKINSEL bit in the XCLK register, GPIO38 is the default |

||

|

|

|

|

|

|

|

|

selection. This pin feeds a clock from an external 3.3-V oscillator. In this case, the X1 |

||

|

|

|

|

|

|

|

|

pin, if available, must be tied to GND and the on-chip crystal oscillator must be |

||

|

|

|

|

See GPIO19 and |

|

|

disabled via bit 14 in the CLKCTL register. If a crystal/resonator is used, the XCLKIN |

|||

|

XCLKIN |

|

I |

|

path must be disabled by bit 13 in the CLKCTL register. |

|||||

|

|

GPIO38 |

|

|||||||

|

|

|

|

|

|

NOTE: Designs that use the GPIO38/TCK/XCLKIN pin to supply an external clock for |

||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

normal device operation may need to incorporate some hooks to disable this path |

||

|

|

|

|

|

|

|

|

during debug using the JTAG connector. This is to prevent contention with the TCK |

||

|

|

|

|

|

|

|

|

signal, which is active during JTAG debug sessions. The zero-pin internal oscillators |

||

|

|

|

|

|

|

|

|

may be used during this time to clock the device. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On-chip crystal-oscillator input. To use this oscillator, a quartz crystal or a ceramic |

||

|

X1 |

|

52 |

41 |

I |

|

resonator must be connected across X1 and X2. In this case, the XCLKIN path must |

|||

|

|

|

be disabled by bit 13 in the CLKCTL register. If this pin is not used, it must be tied to |

|||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

GND. (I) |

||

|

|

|

|

|

|

|

|

|

|

|

|

X2 |

|

51 |

40 |

O |

|

On-chip crystal-oscillator output. A quartz crystal or a ceramic resonator must be |

|||

|

|

|

connected across X1 and X2. If X2 is not used, it must be left unconnected. (O) |

|||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

(1)I = Input, O = Output, Z = High Impedance, OD = Open Drain, ↑ = Pullup, ↓ = Pulldown

Copyright © 2009–2010, Texas Instruments Incorporated |

Introduction |

7 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

SPRS584D–APRIL 2009 –REVISED JUNE 2010 www.ti.com

Table 2-2. Terminal Functions (1) (continued)

|

|

|

TERMINAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O/Z |

|

|

DESCRIPTION |

|

|

NAME |

|

PN |

PAG |

|

|

||||

|

|

PIN # |

PIN # |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

RESET |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Device Reset (in) and Watchdog Reset (out). Piccolo devices have a built-in |

||

|

|

|

|

|

|

|

|

power-on-reset (POR) and brown-out-reset (BOR) circuitry. As such, no external |

||

|

|

|

|

|

|

|

|

circuitry is needed to generate a reset pulse. During a power-on or brown-out |

||

|

|

|

|

|

|

|

|

condition, this pin is driven low by the device. See the electrical section for thresholds |

||

|

|

|

|

|

|

|

|

of the POR/BOR block. This pin is also driven low by the MCU when a watchdog reset |

||

|

|

|

|

|

|

|

|

occurs. During watchdog reset, the |

XRS |

pin is driven low for the watchdog reset |

|

|

|

|

|

|

|

|

duration of 512 OSCCLK cycles. If need be, an external circuitry may also drive this |

||

|

XRS |

|

9 |

7 |

I/O |

|

||||

|

|

|

pin to assert a device reset. In this case, it is recommended that this pin be driven by |

|||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

an open-drain device. An R-C circuit must be connected to this pin for noise immunity |

||

|

|

|

|

|

|

|

|

reasons. Regardless of the source, a device reset causes the device to terminate |

||

|

|

|

|

|

|

|

|

execution. The program counter points to the address contained at the location |

||

|

|

|

|

|

|

|

|

0x3FFFC0. When reset is deactivated, execution begins at the location designated by |

||

|

|

|

|

|

|

|

|

the program counter. The output buffer of this pin is an open-drain with an internal |

||

|

|

|

|

|

|

|

|

pullup. (I/OD) |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADC, COMPARATOR, ANALOG I/O |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINA7 |

|

11 |

9 |

I |

|

ADC Group A, Channel 7 input |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINA6 |

|

|

|

I |

|

ADC Group A, Channel 6 input |

|||

|

COMP3A |

|

12 |

10 |

|

Comparator Input 3A |

||||

|

|

I/O |

|

|||||||

|

AIO6 |

|

|

|

|

Digital AIO 6 |

||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINA5 |

|

13 |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADCINA4 |

|

|

|

I |

|

ADC Group A, Channel 4 input |

|||

|

COMP2A |

|

14 |

11 |

I |

|

Comparator Input 2A |

|||

|

AIO4 |

|

|

|

I/O |

|

Digital AIO 4 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINA3 |

|

15 |

12 |

I |

|

ADC Group A, Channel 3 input |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINA2 |

|

|

|

I |

|

ADC Group A, Channel 2 input |

|||

|

COMP1A |

|

16 |

13 |

I |

|

Comparator Input 1A |

|||

|

AIO2 |

|

|

|

I/O |

|

Digital AIO 2 |

|||

|

ADCINA1 |

|

17 |

14 |

I |

|

ADC Group A, Channel 1 input |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADC Group A, Channel 0 input. |

||

|

ADCINA0 |

|

18 |

15 |

I |

|

NOTE: VREFHI and ADCINA0 share the same pin on the 64-pin PAG device and their |

|||

|

|

|

|

|

|

|

|

use is mutually exclusive to one another. |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADC External Reference – only used when in ADC external reference mode. See |

||

|

VREFHI |

|

19 |

15 |

|

|

ADC Section.. |

|||

|

|

|

|

NOTE: VREFHI and ADCINA0 share the same pin on the 64-pin PAG device and their |

||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

use is mutually exclusive to one another. |

||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB7 |

|

30 |

24 |

I |

|

ADC Group B, Channel 7 input |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB6 |

|

|

|

I |

|

ADC Group B, Channel 6 input |

|||

|

COMP3B |

|

29 |

23 |

|

Comparator Input 3B |

||||

|

|

I/O |

|

|||||||

|

AIO14 |

|

|

|

|

Digital AIO 14 |

||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB5 |

|

28 |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB4 |

|

|

|

I |

|

ADC Group B, Channel 4 input |

|||

|

COMP2B |

|

27 |

22 |

I |

|

Comparator Input 2B |

|||

|

AIO12 |

|

|

|

I/O |

|

Digital AIO12 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB3 |

|

26 |

21 |

I |

|

ADC Group B, Channel 3 input |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB2 |

|

|

|

I |

|

ADC Group B, Channel 2 input |

|||

|

COMP1B |

|

25 |

20 |

I |

|

Comparator Input 1B |

|||

|

AIO10 |

|

|

|

I/O |

|

Digital AIO 10 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB1 |

|

24 |

19 |

I |

|

ADC Group B, Channel 1 input |

|||

|

|

|

|

|

|

|

|

|

|

|

|

ADCINB0 |

|

23 |

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VREFLO |

|

22 |

17 |

|

|

NOTE: VREFLO is always connected to VSSA on the 64-pin PAG device. |

|||

8 |

Introduction |

Copyright © 2009–2010, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

|

TMS320F28030, TMS320F28031, TMS320F28032 |

|

TMS320F28033, TMS320F28034, TMS320F28035 |

www.ti.com |

SPRS584D –APRIL 2009 –REVISED JUNE 2010 |

Table 2-2. Terminal Functions (1) (continued)

|

|

|

TERMINAL |

|

|

|

|

|

|

|

|

|

|

|

I/O/Z |

|

DESCRIPTION |

|

NAME |

|

PN |

PAG |

|

|||

|

|

PIN # |

PIN # |

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPU AND I/O POWER |

|

|

|

|

|

|

|

||

|

VDDA |

|

20 |

16 |

|

|

Analog Power Pin. Tie with a 2.2-mF capacitor (typical) close to the pin. |

|

|

VSSA |

|

21 |

17 |

|

|

Analog Ground Pin. |

|

|

|

|

|

NOTE: VREFLO is always connected to VSSA on the 64-pin PAG device. |

||||

|

|

|

|

|

|

|

|

|

|

VDD |

|

7 |

5 |

|

|

CPU and Logic Digital Power Pins – no supply source needed when using internal |

|

|

VDD |

|

54 |

43 |

|

|

VREG. Tie with 1.2 µF (minimum) ceramic capacitor (10% tolerance) to ground when |

|

|

|

|

|

using internal VREG. Higher value capacitors may be used, but could impact |

||||

|

VDD |

|

72 |

59 |

|

|

||

|

|

|

|

supply-rail ramp-up time. |

||||

|

VDDIO |

|

36 |

29 |

|

|

Digital I/O and Flash Power Pin – Single Supply source when VREG is enabled |

|

|

VDDIO |

|

70 |

57 |

|

|

||

|

|

|

|

|

||||

|

VSS |

|

8 |

6 |

|

|

|

|

|

VSS |

|

35 |

28 |

|

|

Digital Ground Pins |

|

|

VSS |

|

53 |

42 |

|

|

||

|

|

|

|

|

||||

|

VSS |

|

71 |

58 |

|

|

|

|

|

|

|

|

|

|

VOLTAGE REGULATOR CONTROL SIGNAL |

||

|

|

|

|

|

|

|

|

|

|

VREGENZ |

|

|

73 |

60 |

I |

|

Internal VREG Enable/Disable – pull low to enable VREG, pull high to disable VREG |

|

|

|

|

|

|

|

GPIO AND PERIPHERAL SIGNALS (1) |

|

|

GPIO0 |

|

69 |

56 |

I/O/Z |

|

General purpose input/output 0 |

|

|

EPWM1A |

|

|

|

O |

|

Enhanced PWM1 Output A and HRPWM channel |

|

|

– |

|

|

|

– |

|

– |

|

|

– |

|

|

|

– |

|

– |

|

|

|

|

|

|

|

|

|

|

|

GPIO1 |

|

68 |

55 |

I/O/Z |

|

General purpose input/output 1 |

|

|

EPWM1B |

|

|

|

O |

|

Enhanced PWM1 Output B |

|

|

– |

|

|

|

|

|

– |

|

|

COMP1OUT |

|

|

|

O |

|

Direct output of Comparator 1 |

|

|

|

|

|

|

|

|

|

|

|

GPIO2 |

|

67 |

54 |

I/O/Z |

|

General purpose input/output 2 |

|

|

EPWM2A |

|

|

|

O |

|

Enhanced PWM2 Output A and HRPWM channel |

|

|

– |

|

|

|

|

|

– |

|

|

– |

|

|

|

|

|

– |

|

|

|

|

|

|

|

|

|

|

|

GPIO3 |

|

66 |

53 |

I/O/Z |

|

General purpose input/output 3 |

|

|

EPWM2B |

|

|

|

O |

|

Enhanced PWM2 Output B |

|

|

SPISOMIA |

|

|

|

I/O |

|

SPI-A slave out, master in |

|

|

COMP2OUT |

|

|

|

O |

|

Direct output of Comparator 2 |

|

|

|

|

|

|

|

|

|

|

|

GPIO4 |

|

63 |

51 |

I/O/Z |

|

General purpose input/output 4 |

|

|

EPWM3A |

|

|

|

O |

|

Enhanced PWM3 output A and HRPWM channel |

|

|

– |

|

|

|

|

|

– |

|

|

– |

|

|

|

|

|

– |

|

|

|

|

|

|

|

|

|

|

|

GPIO5 |

|

62 |

50 |

I/O/Z |

|

General purpose input/output 5 |

|

|

EPWM3B |

|

|

|

O |

|

Enhanced PWM3 output B |

|

|

SPISIMOA |

|

|

|

I/O |

|

SPI-A slave in, master out |

|

|

ECAP1 |

|

|

|

I/O |

|

Enhanced Capture input/output 1 |

|

|

|

|

|

|

|

|

|

|

(1)The GPIO function (shown in bold italics) is the default at reset. The peripheral signals that are listed under them are alternate functions. For JTAG pins that have the GPIO functionality multiplexed, the input path to the GPIO block is always valid. The output path from the GPIO block and the path to the JTAG block from a pin is enabled/disabled based on the condition of the TRST signal. See the

TMS320x2803x Piccolo System Control and Interrupts Reference Guide (literature number SPRUGL8) for details.

Copyright © 2009–2010, Texas Instruments Incorporated |

Introduction |

9 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28030 TMS320F28031 TMS320F28032 TMS320F28033 TMS320F28034

TMS320F28035

TMS320F28030, TMS320F28031, TMS320F28032

TMS320F28033, TMS320F28034, TMS320F28035

SPRS584D–APRIL 2009 –REVISED JUNE 2010 www.ti.com

Table 2-2. Terminal Functions (1) (continued)

|

|

|

|

TERMINAL |

|

|

|

|

|

|

|

|

|

|

|

I/O/Z |

DESCRIPTION |

|

|

NAME |

PN |

PAG |

||||

|

|

PIN # |

PIN # |

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|||

|

GPIO6 |

50 |

39 |

I/O/Z |

General purpose input/output 6 |

|||

|

EPWM4A |

|

|

O |

Enhanced PWM4 output A and HRPWM channel |

|||

|

EPWMSYNCI |

|

|

I |

External ePWM sync pulse input |

|||

|

EPWMSYNCO |

|

|

O |

External ePWM sync pulse output |

|||

|

|

|

|

|

|

|||

|

GPIO7 |

49 |

38 |

I/O/Z |

General purpose input/output 7 |

|||

|

EPWM4B |

|

|

O |

Enhanced PWM4 output B |

|||

|

SCIRXDA |

|

|

I |

SCI-A receive data |

|||

|

– |

|

|

|

– |

|||

|

|

|

|

|

|

|||

|

GPIO8 |

43 |

35 |

I/O/Z |

General purpose input/output 8 |

|||

|

EPWM5A |

|

|

O |

Enhanced PWM5 output A and HRPWM channel |

|||

|

– |

|

|

|

– |

|||

|

|

|

|

|

O |

ADC start-of-conversion A |

||

|

ADCSOCAO |

|

|

|||||

|

GPIO9 |

39 |

31 |

I/O/Z |

General purpose input/output 9 |

|||

|

EPMW5B |

|

|

O |

Enhanced PWM5 output B |

|||

|

LINTXA |

|

|

|

LIN transmit A |

|||

|

– |

|

|

|

– |

|||

|

|

|

|

|

|

|||

|

GPIO10 |

65 |

52 |

I/O/Z |