Fairchild Semiconductor 29F52SPC, 29F52SCX, 29F52SC Datasheet

April 1988

Revised August 1999

29F52•29F53

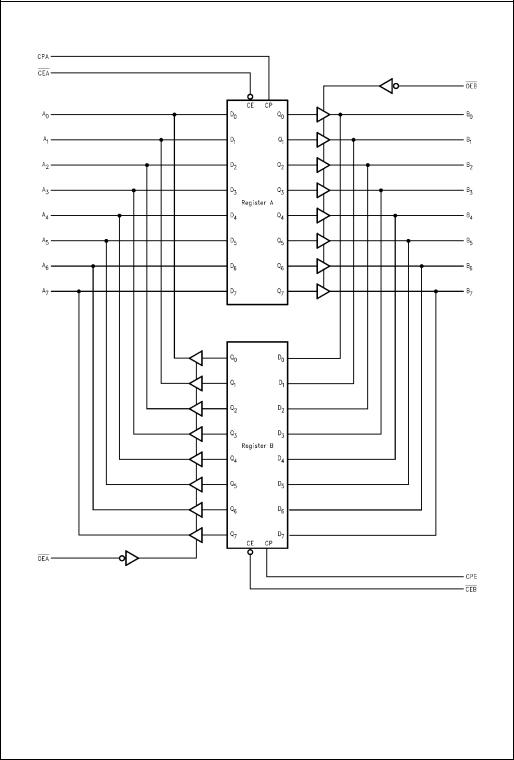

8-Bit Registered Transceiver

General Description

The 29F52 and 29F53 are 8-bit registered transceivers. Two 8-bit back to back registers store data flowing in both directions between two bidirectional buses. Separate clock, clock enable and 3-STATE output enable signals are provided for each register. The A0–A7 output pins are guaranteed to sink 24 mA while the B0–B7 output pins are designed for 64 mA.

The 29F53 is an inverting option of the 29F52. Both transceivers are AMD Am2952/2953 functional equivalents.

Features

■8-bit registered transceivers

■Separate clock, clock enable and 3-STATE output enable provided for each register

■AMD Am2952/2953 functional equivalents

■Both inverting and non-inverting options available

■24-Pin slimline package

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

29F52SC |

M24B |

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

29F52SPC |

N24C |

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide |

|

|

|

29F53SPC |

N24C |

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-100, 0.300 Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Logic Symbols

29F52 29F53

IEEE/IEC |

IEEE/IEC |

29F52 |

29F53 |

Transceiver Registered Bit-8 29F52•29F53

© 1999 Fairchild Semiconductor Corporation |

DS009606 |

www.fairchildsemi.com |

29F52•29F53

Connection Diagrams

Pin Assignment for DIP and SOIC |

Pin Assignment for DIP |

29F52 |

29F53 |

Unit Loading/Fan Out

Pin Names |

Description |

U.L. |

Input IIH/IIL |

|||||

HIGH/LOW |

Output IOH/IOL |

|||||||

|

|

|

|

|

|

|||

|

|

A0–A7 |

A-Register Inputs/ |

3.5/1.083 |

70 μA/0.65 mA |

|||

|

|

|

|

|

B-Register 3-STATE Outputs |

150/40 (33.3) |

−3 mA/24 mA (20 mA) |

|

|

B0–B7 |

B Register Inputs/ |

3.5/1.083 |

70 μA/0.65 mA |

||||

|

|

|

|

|

A-Register 3-STATE Outputs |

600/106.6 (80) |

−12 mA/64 mA (48 mA) |

|

|

|

|

Output Enable A-Register |

1.0/1.0 |

20 μA/−0.6 mA |

|||

|

|

OEA |

|

|||||

|

CPA |

A-Register Clock |

1.0/1.0 |

20 μA/−0.6 mA |

||||

|

|

A-Register Clock Enable |

1.0/1.0 |

20 μA/−0.6 mA |

||||

|

CEA |

|

||||||

|

|

Output Enable B-Register |

1.0/1.0 |

20 μA/−0.6 mA |

||||

|

OEB |

|

||||||

|

CPB |

B-Register Clock |

1.0/1.0 |

20 μA/−0.6 mA |

||||

|

|

B-Register Clock Enable |

1.0/1.0 |

20 μA/−0.6 mA |

||||

|

CEB |

|

||||||

|

|

|

|

|

|

|

|

|

Output Control |

|

|

Register Function Table |

|||||||||

|

|

|

|

|

|

|

(Applies to A or B Register) |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|

Internal |

Y-Output |

Function |

|

|

Inputs |

|

Internal |

Function |

|

|

|

|

Q |

29F52 |

29F53 |

|

|

D |

CP |

CE |

Q |

|

|

H |

|

X |

Z |

Z |

Disable Outputs |

|

|

|

|

|

|

|

|

|

X |

X |

H |

NC |

Hold Data |

|||||

|

|

|

|

|

|

|

|

|||||

|

L |

|

L |

L |

H |

|

|

|

|

|

|

|

|

|

Enable Outputs |

|

L |

N |

L |

L |

Load Data |

||||

|

|

|

|

|

|

|

||||||

|

L |

|

H |

H |

L |

|

H |

N |

L |

H |

||

|

|

|

|

|

||||||||

H = |

HIGH Voltage Level |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||||

L = LOW Voltage Level |

|

|

|

|

|

|

|

|

|

|||

X = Immaterial |

|

|

|

|

|

|

|

|

|

|

||

Z = HIGH Impedance |

|

|

|

|

|

|

|

|

|

|||

N = LOW-to-HIGH Transition |

|

|

|

|

|

|

|

|

||||

NC = No Change |

|

|

|

|

|

|

|

|

|

|||

www.fairchildsemi.com |

2 |

Block Diagrams

29F52

29F52•29F53

3 |

www.fairchildsemi.com |

Loading...

Loading...