Fairchild Semiconductor 100302SCX, 100302SC, 100302QIX, 100302QI, 100302QCX Datasheet

...

© 2000 Fairchild Semiconductor Corporation DS010580 www.fairchildsemi.com

August 1989

Revised August 2000

100302 Low Power Quint 2-Input OR/NOR Gate

100302

Low Power Quint 2-Input OR/NOR Gate

General Description

The 100302 is a monolithic quint 2-input OR/NOR gate with

common enable. All inputs have 50 k

Ω pull-down resistors

and all outputs are buffered.

Features

■ 43% power reduction of the 100102

■ 2000V ESD protection

■ Pin/function compatible with 100102

■ Voltage compensated operating range

= −4.2V to −5.7V

■ Available to industrial grade temperature range

(PLCC package only)

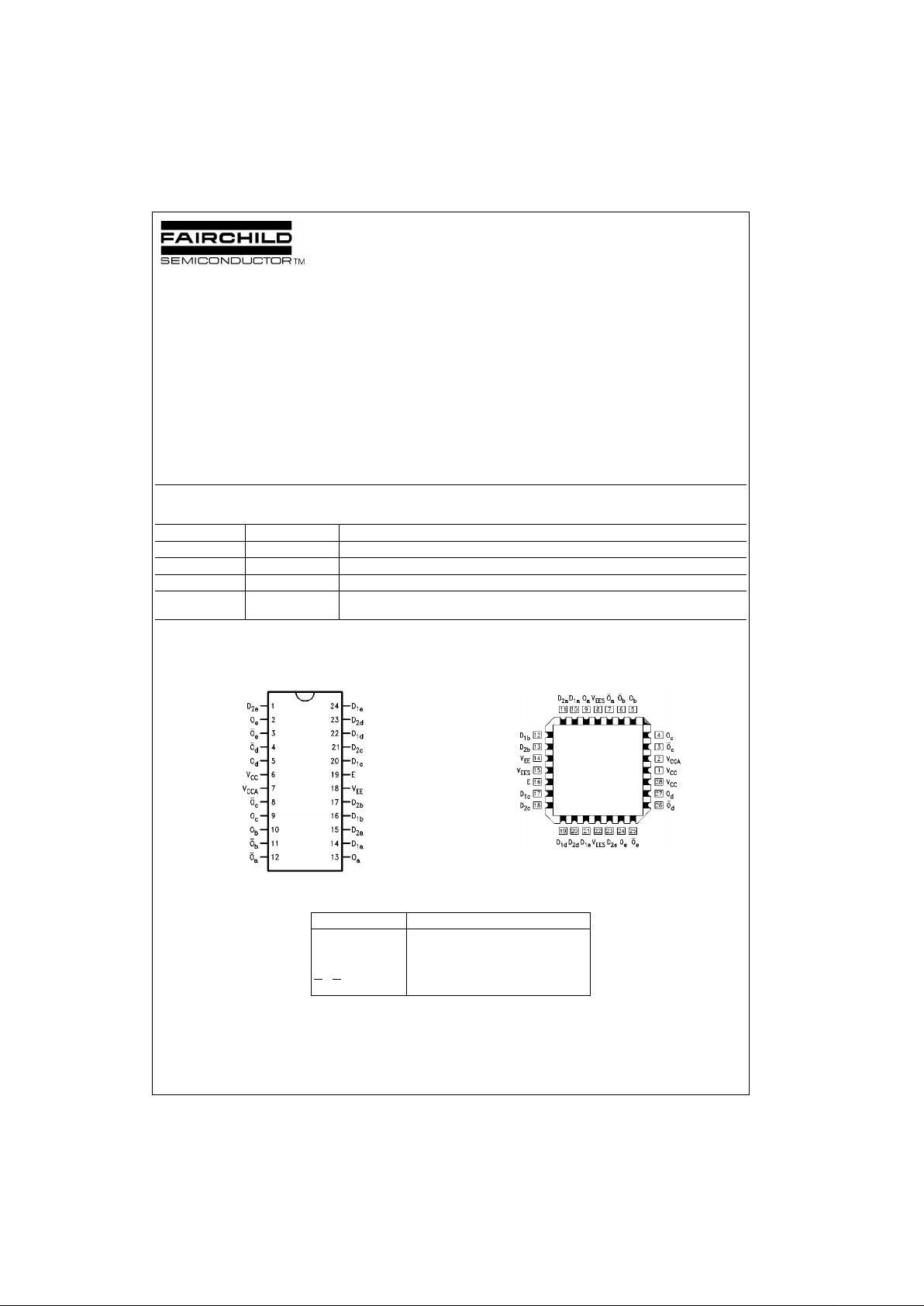

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

Connection Diagrams

24-Pin DIP/SOIC 28-Pin PLCC

Pin Descriptions

Order Number Package Number Package Description

100302SC M24B 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

100302PC N24E 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.400 Wide

100302QC V28A 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square

100302QI V28A 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square

Industrial Temperature Range (

−40°C to +85°C)

Pin Names Description

D

na–Dne

Data Inputs

E Enable Input

O

a–Oe

Data Outputs

O

a–Oe

Complementary Data Outpu ts

www.fairchildsemi.com 2

100302

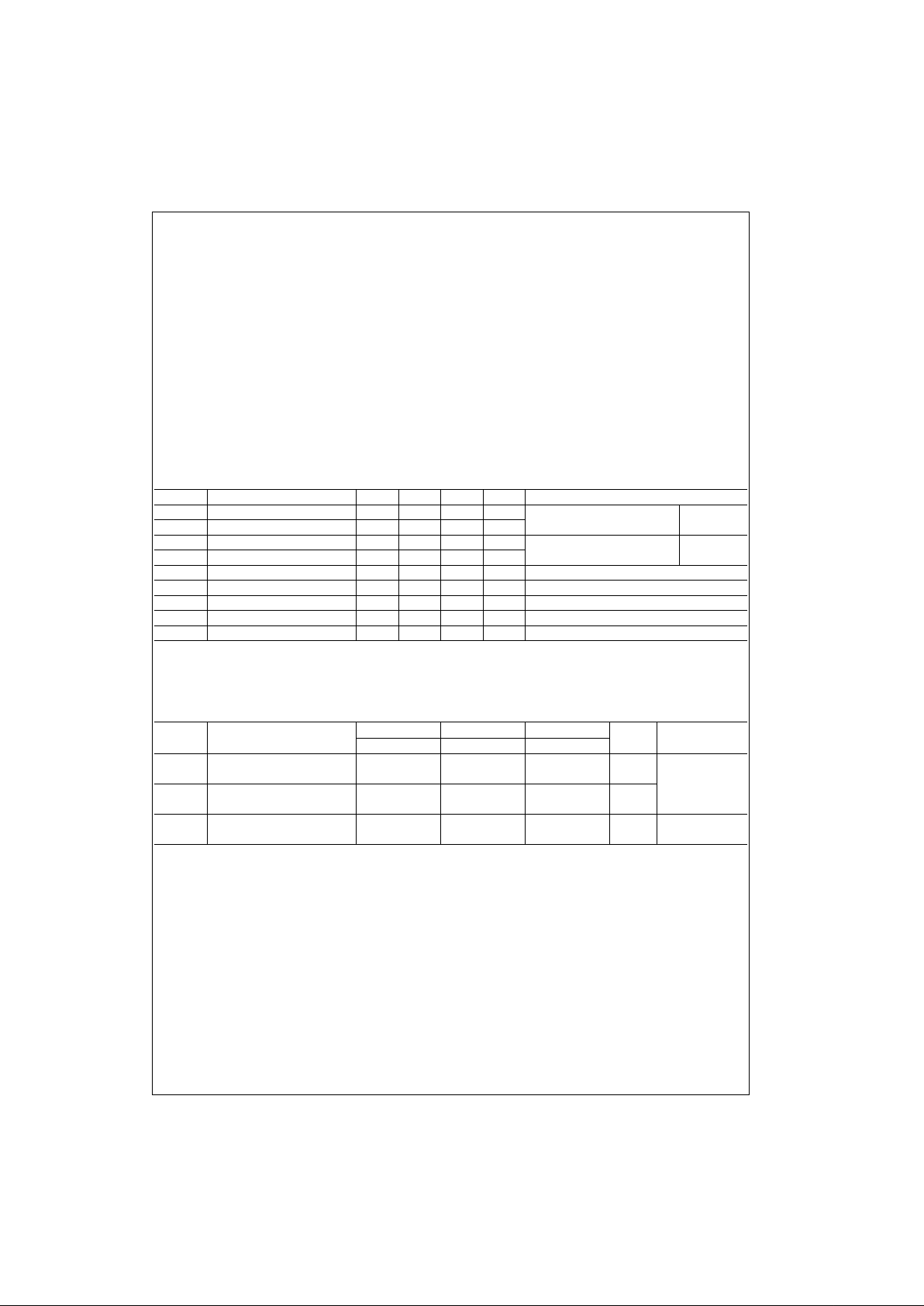

Logic Symbol Truth Table

H = HIGH Voltage Level L = LOW Voltage Level

D

1X

D

2X

E

O

X

O

X

LLLLH

LLHHL

LHLHL

LHHHL

HLLHL

HLHHL

HHLHL

HHHHL

3 www.fairchildsemi.com

100302

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

Note 1: The “Absolute Maximum Ratings” are those value s beyond which

the safety of the dev ice cannot b e guaranteed . The device sh ould not be

operated at these limit s. The parametric values defi ned in the Electrical

Characteristics tables are not guaranteed at the absolute maximum rating.

The “Recomm ended O peratin g Cond itions ” table will defin e the condition s

for actual device operation.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

Commercial Version

DC Electrical Characteristics

(Note 3)

V

EE

= −4.2V to −5.7V, VCC = V

CCA

= GND, T

C

= 0°C to +85°C

Note 3: The specified limits represent the “worst case” value for the parameter. Since these values normally occur at the temperature extremes, additional

noise immunity and guardbanding can be achieved by decreasin g the al l owable syste m opera ti ng ran ge s. Cond it i ons fo r t estin g sho w n in the tabl es are chosen to guarantee operation under “worst case” conditions.

DIP AC Electrical Characteristics

V

EE

= −4.2V to −5.7V, VCC = V

CCA

= GND

Note 4: The propagation delay s pec ified is for single output swit c hing. Delays may vary up to 100 ps with multiple outpu ts s witching.

Storage Temperature (T

STG

) −65°C to +150°C

Maximum Junction Temperature (T

J

) +150°C

V

EE

Pin Potential to Ground Pin −7.0V to +0.5V

Input Voltage (DC) V

EE

to +0.5V

Output Current (DC Output HIGH)

−50 mA

ESD (Note 2)

≥2000V

Case Temperature (T

C

)

Commercial 0

°C to +85°C

Industrial

−40°C to +85°C

Supply Voltage (V

EE

) −5.7V to −4.2V

Symbol Parameter Min Typ Max Units Conditions

V

OH

Output HIGH Voltage −1025 −955 −870 mV

VIN = V

IH(Max)

or V

IL(Min)

Loading with

V

OL

Output LOW Voltage −1830 −1705 −1620 mV 50Ω to −2.0V

V

OHC

Output HIGH Voltage −1035 mV

VIN = V

IH(Min)

or V

IL(Max)

Loading with

V

OLC

Output LOW Voltage −1610 mV 50Ω to −2.0V

V

IH

Input HIGH Voltage −1165 −870 mV Guaranteed HIGH Signal for All Inputs

V

IL

Input LOW Voltage −1830 −1475 mV Guaranteed LOW Signal for All Inputs

I

IL

Input LOW Current 0.50 µAVIN = V

IL(Min)

I

IH

Input HIGH Current 240 µAVIN = V

IH(Max)

I

EE

Power Supply Current −45 −36 −20 mA Inputs OPEN

Symbol Parameter

TC = 0°CT

C

= +25°CT

C

= +85°C

Units Conditions

Min Max Min Max Min Max

t

PLH

Propagation Delay

0.50 1.15 0.50 1.15 0.50 1.25 ns

t

PHL

Data to Output Figures 1, 2

t

PLH

Propagation Delay

0.70 1.90 0.70 1.90 0.80 2.00 ns

(Note 4)

t

PHL

Enable to Output

t

TLH

Transition Time

0.40 1.20 0.40 1.20 0.40 1.20 ns Figures 1, 2

t

THL

20% to 80%, 80% to 20%

Loading...

Loading...