Fairchild Semiconductor 100325SCX, 100325SC, 100325QIX, 100325QI, 100325QCX Datasheet

...

July 1988

Revised August 2000

100325

Low Power Hex ECL-to-TTL Translator

General Description

The 100325 is a hex translator for converting F100K logic levels to TTL logic levels. Differential inputs allow each circuit to be used as an inverting, non-inverting or differential receiver. An internal reference voltage generator provides VBB for single-ended operation, or for use in Schmitt trigger applications. All inputs have 50kΩ pull-down resistors. When the inputs are either unconnected or at the same potential the outputs will go LOW.

When used in single-ended operation the apparent input threshold of the true inputs is 20mV to 40mV higher (positive) than the threshold of the complementary inputs. The VEE and VTTL power may be applied in either order.

Features

■Pin/function compatible with 100125

■Meets 100125 AC specifications

■50% power reduction of the 100125

■Differential inputs with built in offset

■Standard FAST outputs

■2000V ESD protection

■− 4.2V to − 5.7V operating range

■Available to industrial grade temperature range

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

100325SC |

M24B |

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

100325PC |

N24E |

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.400 Wide |

|

|

|

100325QI |

V28A |

28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square |

|

|

|

100325QC |

V28A |

28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square |

|

|

Industrial Temperature Range (− 40° C to + 85° C) |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

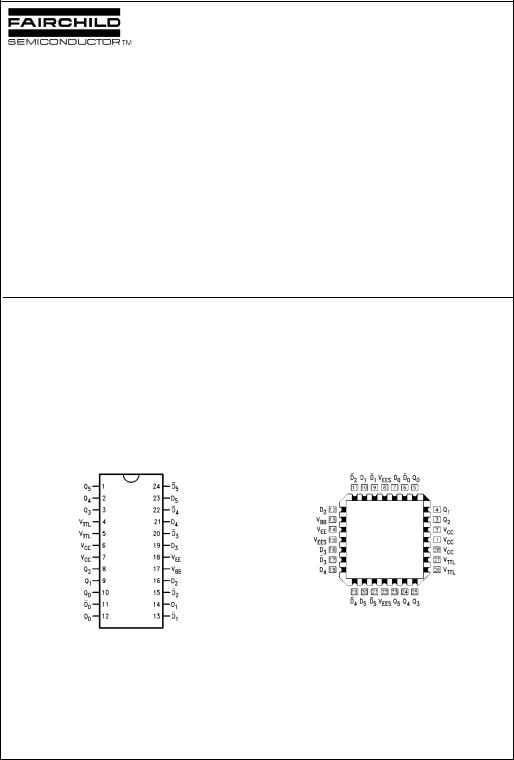

Connection Diagrams

24-Pin DIP/SOIC 28-Pin PLCC

Pin Descriptions

|

|

|

Pin Names |

Description |

|

|

|

|

|||

|

D0–D5 |

Data Inputs |

|||

|

|

|

|

|

|

|

D |

0–D |

5 |

Inverting Data Inputs |

|

|

Q0–Q5 |

Data Outputs |

|||

FAST is a registered trademark of Fairchild Semiconductor Corporation.

Translator TTL-to-ECL Hex Power Low 100325

© 2000 Fairchild Semiconductor Corporation |

DS009879 |

www.fairchildsemi.com |

100325

Truth Table |

|

|

|

|

|

Logic Diagram |

|

|

|

|

|

|

|

||

|

|

Inputs |

Outputs |

|

|||

|

|

|

|

|

|

|

|

|

Dn |

|

|

Dn |

Qn |

|

|

|

L |

|

|

H |

L |

|

|

|

H |

|

|

L |

H |

|

|

|

L |

|

|

L |

L |

|

|

|

H |

|

|

H |

L |

|

|

|

OPEN |

|

OPEN |

L |

|

||

|

VEE |

|

VEE |

L |

|

||

|

L |

|

VBB |

L |

|

||

|

H |

|

VBB |

H |

|

||

|

VBB |

|

|

L |

H |

|

|

|

VBB |

|

|

H |

L |

|

|

H = HIGH Voltage Level |

|

|

|

|

|

|

|

L = LOW Voltage Level |

|

|

|

|

|

|

|

www.fairchildsemi.com |

2 |

Absolute Maximum Ratings(Note 1)

Storage Temperature (TSTG) |

− 65° C to + 150° C |

Maximum Junction Temperature (TJ) |

+ 150° C |

VEE Pin Potential to Ground Pin |

− 7.0V to + 0.5V |

VTTL Pin Potential to Ground Pin |

− 0.5V to + 6.0V |

Input Voltage (DC) |

VEE to + 0.5V |

Voltage Applied to Output |

|

in HIGH State (with VCC = 0V) |

− 0.5V to VCC |

Current Applied to Output |

|

in LOW State (Max) |

twice the rated IOL (mA) |

ESD (Note 2) |

≥ 2000V |

Recommended Operating

Conditions

Case Temperature (TC) |

|

Commercial |

0° C to + 85° C |

Industrial |

− 40° C to + 85° C |

Supply Voltage (VEE) |

− 5.7V to − 4.2V |

Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The “Recommended Operating Conditions” table will define the conditions for actual device operation.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

Commercial Version

DC Electrical Characteristics

VEE = − 4.2V to − 5.7V, VCC = GND, VTTL = + 4.5V to 5.5V, TC = |

0° C to + 85° C (Note 3) |

|

|

|

|

|||||||||

Symbol |

Parameter |

Min |

Typ |

|

Max |

Units |

|

|

|

|

|

Conditions |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

VBB |

Output Reference Voltage |

− 1380 |

− 1320 |

|

− 1260 |

mV |

|

IVBB = |

− |

2.1 mA |

|

|

||

VIH |

Single-Ended Input |

− 1165 |

|

|

− 870 |

mV |

|

Guaranteed HIGH Signal for All Inputs |

||||||

|

HIGH Voltage |

|

|

|

(with One Input Tied to VBB) |

|||||||||

|

|

|

|

|

|

|

||||||||

VIL |

Single-Ended Input |

− 1830 |

|

|

− 1475 |

mV |

|

Guaranteed LOW Signal for All Inputs |

||||||

|

LOW Voltage |

|

|

|

(with One Input Tied to VBB) |

|||||||||

|

|

|

|

|

|

|

||||||||

VOH |

Output HIGH Voltage |

2.5 |

|

|

|

V |

|

IOH = |

− 2.0 mA |

|

VIN = VIH (Max) |

|||

VOL |

Output LOW Voltage |

|

|

|

0.5 |

V |

|

IOL = |

20 mA |

|

or VIL (Min) |

|||

VDIFF |

Input Voltage Differential |

150 |

|

|

|

mV |

|

Required for Full Output Swing |

||||||

VCM |

Common Mode Voltage |

VCC − 2.0 |

|

VCC − 0.5 |

V |

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

|

|

350 |

µ A |

|

VIN = |

VIH (Max), D0–D5 = |

VBB, |

||||

|

|

|

|

|

|

|

|

|

|

|

5 = |

|

|

|

|

|

|

|

|

|

|

|

D |

0–D |

VIL (Min) |

|

|

||

IIL |

Input LOW Current |

0.5 |

|

|

|

µ A |

|

VIN = |

VIL (Min), D0–D5 = |

VBB |

||||

IOS |

Output Short-Circuit Current |

− 150 |

|

|

− 60 |

mA |

|

VOUT = |

GND (Note 4) |

|

|

|||

IEE |

VEE Power Supply Current |

− 37 |

− 27 |

|

− 17 |

mA |

|

D0–D5 = |

VBB |

|

|

|||

ITTL |

VTTL Power Supply Current |

|

45 |

|

65 |

mA |

D0–D5 = |

VBB |

|

|

||||

Note 3: The specified limits represent the “worst case” value for the parameter. Since these values normally occur at the temperature extremes, additional noise immunity and guardbanding can be achieved by decreasing the allowable system operating ranges. Conditions for testing shown in the tables are chosen to guarantee operation under “worst case” conditions.

Note 4: Test one output at a time.

DIP AC Electrical Characteristics

VEE = − 4.2V to − 5.7V, VCC = GND, VTTL = + |

4.5V to + 5.5V |

|

|

|

|

|

|

|

|||

Symbol |

Parameter |

TC = 0° C |

TC = + 25° C |

TC = + 85° C |

Units |

|

Conditions |

||||

Min |

Max |

Min |

Max |

Min |

Max |

|

|||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

tPLH |

Propagation Delay |

0.80 |

3.50 |

0.90 |

3.70 |

1.00 |

4.00 |

ns |

CL = |

15 pF |

|

tPHL |

Data to Output |

Figures 1, 2 |

|||||||||

|

|

|

|

|

|

|

|||||

tPLH |

Propagation Delay |

1.60 |

4.30 |

1.70 |

4.50 |

1.80 |

4.80 |

ns |

CL = |

50 pF |

|

tPHL |

Data to Output |

Figures 1, 3 |

|||||||||

|

|

|

|

|

|

|

|||||

100325

3 |

www.fairchildsemi.com |

Loading...

Loading...