Fairchild Semiconductor 74ABT125CSJX, 74ABT125CSJ, 74ABT125CSCX, 74ABT125CSC, 74ABT125CMTCX Datasheet

...

March 1994

Revised November 1999

74ABT125

Quad Buffer with 3-STATE Outputs

General Description

The ABT125 contains four independent non-inverting buffers with 3-STATE outputs.

Features

■Non-inverting buffers

■Output sink capability of 64 mA, source capability of 32 mA

■Guaranteed latchup protection

■High impedance glitch free bus loading during entire power up and power down cycle

■Nondestructive hot insertion capability

■Disable time less than enable time to avoid bus contention

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

74ABT125CSC |

M14A |

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150” Narrow Body |

|

|

|

74ABT125CSJ |

M14D |

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

74ABT125CMTC |

MTC14 |

14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153,4.4mm Wide |

|

|

|

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

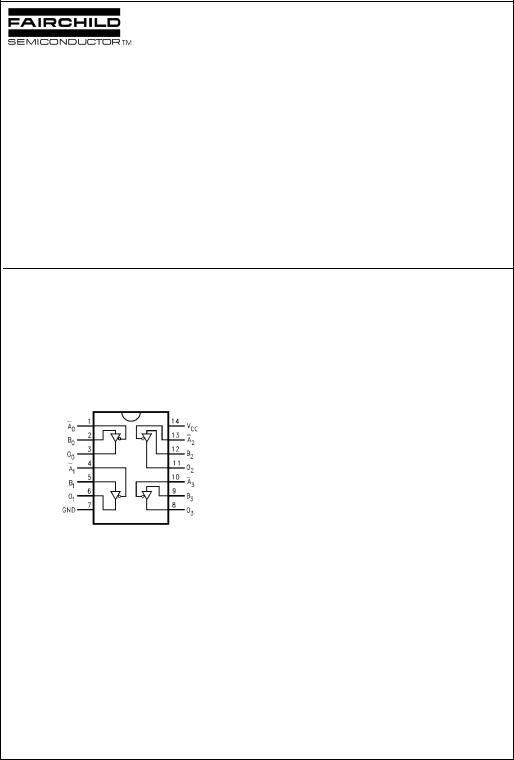

Connection Diagram |

Pin Descriptions |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

Pin Names |

|

Descriptions |

|

|

|

|

|

|

|

|

|

|

|

|

|

n, Bn |

|

|

Inputs |

|

|

|

A |

|

|

||

|

|

|

On |

|

|

Outputs |

|

|

Function Table |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

Inputs |

|

|

Output |

|

|

|

|

|

|

|

|

|

|

|

|

An |

Bn |

|

On |

|

|

|

|

L |

L |

|

L |

|

|

|

|

L |

H |

|

H |

|

|

|

|

H |

X |

|

Z |

|

|

|

|

|

|

|

|

H = |

HIGH Voltage Level |

L = |

LOW Voltage Level |

Z = |

HIGH Impedance |

X = |

Immaterial |

Outputs STATE-3 with Buffer Quad 74ABT125

© 1999 Fairchild Semiconductor Corporation |

DS011667 |

www.fairchildsemi.com |

74ABT125

Absolute Maximum Ratings(Note 1)

Storage Temperature |

− 65° C to + 150° C |

Ambient Temperature under Bias |

− 55° C to + 125° C |

Junction Temperature under Bias |

− 55° C to + 150° C |

VCC Pin Potential to |

|

Ground Pin |

− 0.5V to + 7.0V |

Input Voltage (Note 2) |

− 0.5V to + 7.0V |

Input Current (Note 2) |

− 30 mA to + 5.0 mA |

Voltage Applied to Any Output |

|

in the Disabled or |

|

Power-Off State |

− 0.5V to 5.5V |

in the HIGH State |

− 0.5V to VCC |

Current Applied to Output |

|

in LOW State (Max) |

twice the rated IOL (mA) |

DC Latchup Source Current |

|

(Across Comm Operating Range) |

− 300 mA |

Over Voltage Latchup (I/O) |

10V |

Recommended Operating

Conditions

Free Air Ambient Temperature |

− 40° C to + 85° C |

Supply Voltage |

+ 4.5V to + 5.5V |

Minimum Input Edge Rate (∆ V/∆ t) |

|

Data Input |

50 mV/ns |

Enable Input |

20 mV/ns |

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

DC Electrical Characteristics

Symbol |

Parameter |

Min |

Typ |

Max |

Units |

VCC |

|

|

|

|

Conditions |

||||

VIH |

Input HIGH Voltage |

|

|

|

|

V |

|

|

Recognized HIGH Signal |

||||||

VIL |

Input LOW Voltage |

|

|

|

0.8 |

V |

|

|

Recognized LOW Signal |

||||||

VCD |

Input Clamp Diode Voltage |

|

|

− 1.2 |

V |

Min |

|

IIN = |

− 18 mA |

|

|||||

VOH |

Output HIGH Voltage |

|

2.5 |

|

|

V |

Min |

|

IOH = |

− |

3 mA |

|

|||

|

|

|

2.0 |

|

|

V |

Min |

|

IOH = |

− |

32 mA |

|

|||

VOL |

Output LOW Voltage |

|

|

|

0.55 |

V |

Min |

|

IOL = |

64 mA |

|

||||

IIH |

Input HIGH Current |

|

|

|

1 |

µ A |

Max |

|

VIN = |

2.7V (Note 3) |

|

||||

|

|

|

|

|

1 |

|

VIN = |

VCC |

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

IBVI |

Input HIGH Current Breakdown Test |

|

|

7 |

µ A |

Max |

|

VIN = |

7.0V |

|

|||||

IIL |

Input LOW Current |

|

|

|

− 1 |

µ A |

Max |

|

VIN = |

0.5V (Note 3) |

|

||||

|

|

|

|

|

− 1 |

|

VIN = |

0.0V |

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

VID |

Input Leakage Test |

|

|

|

|

V |

0.0 |

IID = |

1.9 µ A, All Other Pin Grounded |

||||||

IOZH |

Output Leakage Current |

|

|

10 |

µ A |

0− 5.5V |

|

VOUT = |

2.7V; |

|

n = |

|

|||

|

|

|

OE |

2.0V |

|||||||||||

IOZL |

Output Leakage Current |

|

|

− 10 |

µ A |

0− 5.5V |

|

VOUT = |

0.5V; |

|

n = |

|

|||

|

|

|

OE |

2.0V |

|||||||||||

IOS |

Output Short-Circuit Current |

|

|

− 275 |

mA |

Max |

|

VOUT = |

0.0V |

|

|||||

ICEX |

Output HIGH Leakage Current |

|

|

50 |

µ A |

Max |

|

VOUT = |

VCC |

|

|||||

IZZ |

Bus Drainage Test |

|

|

|

100 |

µ A |

0.0 |

|

VOUT = |

5.5V; All Others GND |

|||||

ICCH |

Power Supply Current |

|

|

|

50 |

µ A |

Max |

All Outputs HIGH |

|

||||||

ICCL |

Power Supply Current |

|

|

|

15 |

mA |

Max |

All Outputs LOW |

|

||||||

ICCZ |

Power Supply Current |

|

|

|

50 |

µ A |

Max |

|

|

n = |

VCC; |

|

|||

|

|

|

|

OE |

|

||||||||||

|

|

|

|

|

|

|

|

|

All Others at VCC or Ground |

||||||

ICCT |

Additional ICC /Input |

Outputs Enabled |

|

|

1.5 |

mA |

|

|

VI = |

V CC − 2.1V |

|

||||

|

|

Outputs 3-STATE |

|

|

1.5 |

mA |

Max |

|

Enable Input VI = VCC − 2.1V |

||||||

|

|

Outputs 3-STATE |

|

|

50 |

µ A |

|

Data Input V I = VCC − 2.1V |

|||||||

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

All Others at VCC or Ground |

||||||

ICCD |

Dynamic ICC |

No Load |

|

|

|

mA/ |

|

|

Outputs Open |

|

|||||

|

(Note 3) |

|

|

|

0.1 |

MHz |

Max |

|

|

n = |

GND, (Note 4) |

||||

|

|

|

|

|

OE |

||||||||||

|

|

|

|

|

|

|

|

|

One Bit Toggling, 50% Duty Cycle |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 3: Guaranteed, but not tested. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 4: For 8 bits toggling, ICCD < 0.8 mA/MHz. |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

www.fairchildsemi.com |

2 |

Loading...

Loading...