ANALOG DEVICES AD7170 Service Manual

Data Sheet

12-Bit Low Power Sigma-Delta ADC

AD7170

FEATURES

Output data rate: 125 Hz Pin-programmable power-down and reset Status function

Internal clock oscillator Current: 135 μA

Power supply: 2.7 V to 5.25 V –40°C to +105°C temperature range

Package: 10-lead 3 mm x 3 mm LFCSP

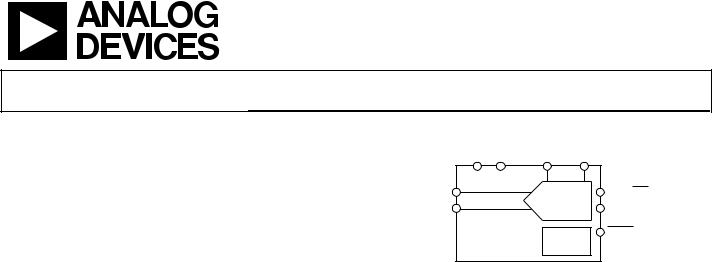

FUNCTIONAL BLOCK DIAGRAM

GND |

VDD |

REFIN(+) REFIN(–) |

|

|

AIN(+) |

|

12-BIT Σ-∆ |

DOUT/RDY |

|

|

|

|

||

AIN(–) |

|

ADC |

SCLK |

|

AD7170 |

INTERNAL |

PDRST |

||

08416-001 |

||||

|

|

CLOCK |

||

|

|

|

||

Figure 1.

INTERFACE

2-wire serial (read-only device) SPI compatible

Schmitt trigger on SCLK

APPLICATIONS

Pressure measurement

Industrial process control

Portable instrumentation

GENERAL DESCRIPTION

The AD7170 is a very low power 12-bit analog-to-digital converter (ADC). It contains a precision 12-bit sigma-delta (Σ-Δ) ADC and an on-chip oscillator. Consuming only 135 μA, the AD7170 is particularly suitable for portable or battery operated products where very low power is a requirement. The AD7170 also has a power-down mode in which the device consumes 5 μA, thus increasing the battery life of the product.

For ease-of-use, all the features of the AD7170 are controlled by dedicated pins. Each time a data read occurs, eight status bits are appended to the 12-bit conversion. These status bits contain a pattern sequence that can be used to confirm the validity of the serial transfer.

Table 1.

|

|

|

P-P |

|

VREF = VDD |

RMS Noise |

P-P Noise |

Resolution |

ENOB |

|

|

|

|

|

5 V |

11.5 μV |

76 μV |

12 bits |

12 bits |

3 V |

6.9 μV |

45 μV |

12 bits |

12 bits |

The output data rate of the AD7170 is 125 Hz, whereas the settling time is 24 ms. The AD7170 has one differential input and a gain of 1. This is useful in applications where the user needs to use an external amplifier to implement system-specific filtering or gain requirements.

The AD7170 operates with a power supply from 2.7 V to 5.25 V. It is available in a 10-lead LFCSP package.

The AD7171 is a 16-bit version of the AD7170. It has the same feature set as the AD7170 and is pin-for-pin compatible.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibilityisassumedbyAnalogDevicesforitsuse,norforanyinfringementsofpatentsorother rightsofthirdpartiesthatmayresultfromitsuse.Specificationssubjecttochangewithoutnotice.No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2009–2011 Analog Devices, Inc. All rights reserved.

AD7170 |

Data Sheet |

|

|

TABLE OF CONTENTS |

|

Features .............................................................................................. |

1 |

Interface ............................................................................................. |

1 |

Applications....................................................................................... |

1 |

Functional Block Diagram .............................................................. |

1 |

General Description ......................................................................... |

1 |

Revision History ............................................................................... |

2 |

Specifications..................................................................................... |

3 |

Timing Characteristics..................................................................... |

5 |

Timing Diagrams.......................................................................... |

5 |

Absolute Maximum Ratings............................................................ |

6 |

Thermal Resistance ...................................................................... |

6 |

ESD Caution.................................................................................. |

6 |

Pin Configuration and Function Descriptions............................. |

7 |

Typical Performance Characteristics ............................................. |

8 |

Output Noise and Resolution Specifications ................................ |

9 |

ADC Circuit Information.............................................................. |

10 |

REVISION HISTORY |

|

9/11—Rev. 0 to Rev. A |

|

Changes to Digital Interface Section............................................ |

11 |

Updated Outline Dimensions ....................................................... |

14 |

Changes to Ordering Guide .......................................................... |

14 |

10/09—Revision 0: Initial Version |

|

Overview ..................................................................................... |

10 |

Filter, Data Rate, and Settling Time......................................... |

10 |

Gain.............................................................................................. |

10 |

Power-Down/Reset (PDRST) ................................................... |

10 |

Analog Input Channel ............................................................... |

10 |

Bipolar Configuration................................................................ |

10 |

Data Output Coding .................................................................. |

11 |

Reference ..................................................................................... |

11 |

Digital Interface.......................................................................... |

11 |

Grounding and Layout .............................................................. |

12 |

Applications Information .............................................................. |

13 |

Temperature System................................................................... |

13 |

Signal Conditioning Circuit...................................................... |

13 |

Outline Dimensions ....................................................................... |

14 |

Ordering Guide .......................................................................... |

14 |

Rev. A | Page 2 of 16

Data Sheet |

AD7170 |

|

|

SPECIFICATIONS

VDD = 2.7 V to 5.25 V, VREF = VDD, GND = 0 V, all specifications TMIN to TMAX, unless otherwise noted.

Table 1.

|

|

|

|

AD7170B1 |

|

|

|

Parameter |

Min |

Typ |

Max |

Unit |

Test Conditions/Comments |

||

ADC CHANNEL |

|

|

|

|

|

||

Output Data Rate (fADC) |

|

125 |

|

Hz |

Settling time = 3/fADC |

||

No Missing Codes2 |

12 |

|

|

Bits |

|

||

Noise Free Resolution |

|

12 |

|

Bits |

VINx = 0 V, VREF = VDD |

||

Resolution Peak-to-Peak (p-p) |

|

12 |

|

Bits |

VINx = 0 V, VREF = VDD |

||

Effective Resolution (ENOB) |

|

12 |

|

Bits |

VINx = 0 V, VREF = VDD |

||

RMS Noise |

|

See Table 6 |

|

μV |

VINx = 0 V, VREF = VDD |

||

Integral Nonlinearity |

|

±0.1 |

|

LSB |

|

||

Offset Error |

|

±200 |

|

μV |

|

||

Offset Error Drift vs. Temperature |

|

±250 |

|

nV/°C |

|

||

Full-Scale Error |

|

±0.015 |

|

% of FS |

|

||

Gain Drift vs. Temperature |

|

±0.07 |

|

LSB/°C |

|

||

Power Supply Rejection |

|

85 |

|

dB |

VINx = 1 V |

||

|

|

|

|

|

|

|

|

ANALOG INPUTS |

|

|

|

|

|

||

Differential Input Voltage Range |

|

±VREF |

|

V |

VREF = REFIN(+) − REFIN(−) |

||

Absolute AINx Voltage Limits2 |

GND − 0.03 |

|

VDD + 0.03 |

V |

|

||

Average Input Current2 |

|

±400 |

|

nA/V |

Input current varies with input |

||

|

|

|

|

|

|

|

voltage |

Average Input Current Drift |

|

±60 |

|

pA/V/°C |

|

||

DC Common-Mode Rejection |

|

90 |

|

dB |

VINx = 1 V |

||

REFERENCE |

|

|

|

|

|

||

External REFIN Voltage |

|

VDD |

|

V |

REFIN = REFIN(+) − REFIN(−) |

||

Reference Voltage Range2 |

0.5 |

|

VDD |

V |

|

||

Absolute REFIN Voltage Limits2 |

GND − 0.03 |

|

VDD + 0.03 |

V |

|

||

Average Reference Input Current |

|

400 |

|

nA/V |

|

||

Average Reference Input Current |

|

±0.15 |

|

nA/V/°C |

|

||

Drift |

|

|

|

|

|

||

DC Common-Mode Rejection |

|

110 |

|

dB |

|

||

INTERNAL CLOCK |

|

|

|

|

|

||

Frequency2 |

64 − 5% |

|

64 + 5% |

kHz |

|

||

LOGIC INPUTS |

|

|

|

|

|

||

|

|

|

|

|

|

||

SCLK, |

PDRST |

2 |

|

|

|

|

|

Input Low Voltage, VINL |

|

|

0.4 |

V |

VDD = 3 V |

||

|

|

|

|

|

0.8 |

V |

VDD = 5 V |

Input High Voltage, VINH |

1.8 |

|

|

V |

VDD = 3 V |

||

|

|

|

2.4 |

|

|

V |

VDD = 5 V |

SCLK (Schmitt-Triggered Input)2 |

|

|

|

|

|

||

Hysteresis |

|

100 |

|

mV |

VDD = 3 V |

||

|

|

|

|

140 |

|

mV |

VDD = 5 V |

Input Currents |

|

±2 |

|

μA |

VIN = VDD or GND |

||

Input Capacitance |

|

5 |

|

pF |

All digital inputs |

||

Rev. A | Page 3 of 16

AD7170 |

|

|

|

|

|

Data Sheet |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7170B1 |

|

|

|

|

Parameter |

Min |

Typ |

Max |

Unit |

Test Conditions/Comments |

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

LOGIC OUTPUT (DOUT/RDY) |

|

|

|

|

|

|

|

|

Output High Voltage, VOH2 |

VDD − 0.6 |

|

|

V |

VDD = 3 V, ISOURCE = 100 μA |

|||

|

|

|

4 |

|

|

V |

VDD = 5 V, ISOURCE = 200 μA |

|

Output Low Voltage, VOL2 |

|

|

0.4 |

V |

VDD = 3 V, ISINK = 100 μA |

|||

|

|

|

|

|

0.4 |

V |

VDD = 5 V, ISINK = 1.6 mA |

|

Floating-State Leakage Current |

|

±2 |

|

μA |

|

|||

Floating-State Output |

|

5 |

|

pF |

|

|||

Capacitance |

|

|

|

|

|

|

||

Data Output Coding |

Offset binary |

|

|

|

|

|

||

POWER REQUIREMENTS3 |

|

|

|

|

|

|

||

Power Supply Voltage |

|

|

|

|

|

|

||

VDD – GND |

2.7 |

|

5.25 |

V |

|

|||

Power Supply Currents |

|

|

|

|

|

|

||

IDD Current |

|

110 |

130 |

μA |

VDD = 3 V |

|||

|

|

|

|

135 |

150 |

μA |

VDD = 5 V |

|

IDD (Power-Down/Reset Mode) |

|

5 |

|

μA |

|

|||

|

|

|

|

|

|

|

|

|

1 Temperature range is –40°C to +105°C.

2 Specification is not production tested but is supported by characterization data at initial product release. 3 Digital inputs equal to VDD or GND.

Rev. A | Page 4 of 16

Data Sheet |

AD7170 |

|

|

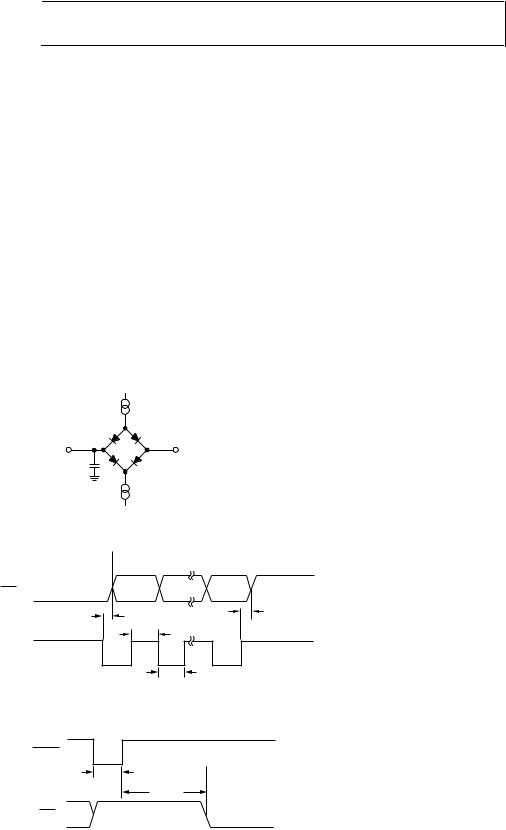

TIMING CHARACTERISTICS

VDD = 2.7 V to 5.25 V, GND = 0 V, Input Logic 0 = 0 V, Input Logic 1 = VDD, unless otherwise noted.

Table 2.

Parameter1, 2 |

Limit at TMIN, TMAX |

Unit |

|

Conditions/Comments |

||||

READ |

|

|

|

|

|

|

|

|

t1 |

100 |

ns min |

|

SCLK high pulse width |

||||

t2 |

100 |

ns min |

|

SCLK low pulse width |

||||

t33 |

0 |

ns min |

|

SCLK active edge to data valid delay4 |

||||

|

60 |

ns max |

|

VDD = 4.75 V to 5.25 V |

||||

|

80 |

ns max |

|

VDD = 2.7 V to 3.6 V |

||||

t4 |

10 |

ns min |

|

|

|

|

|

|

|

SCLK inactive edge to DOUT/RDY |

high |

||||||

|

|

|

|

|

|

|

|

|

RESET |

|

|

|

|

|

|

|

|

t5 |

100 |

ns min |

|

|

low pulse width |

|||

|

PDRST |

|

||||||

t6 |

25 |

ms typ |

|

|

||||

|

PDRST |

high to data valid delay |

||||||

|

|

|

|

|

|

|

|

|

1 Sample tested during initial release to ensure compliance. All input signals are specified with tR = tF = 5 ns (10% to 90% of VDD) and timed from a voltage level of 1.6 V. 2 See Figure 3.

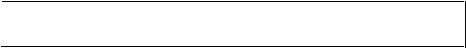

3 These numbers are measured with the load circuit shown in Figure 2 and defined as the time required for the output to cross the VOL or VOH limits. 4 SCLK active edge is the falling edge of SCLK.

|

ISINK (1.6mA WITH VDD = 5V, |

|

|

|

100µA WITH VDD = 3V) |

|

|

TO |

|

|

|

OUTPUT |

1.6V |

|

|

PIN |

50pF |

|

|

|

|

|

|

|

ISOURCE (200µA WITH VDD = 5V, |

-002 |

|

|

100µA WITH VDD = 3V) |

|

08416 |

Figure 2. Load Circuit for Timing Characterization |

|

||

TIMING DIAGRAMS |

|

|

|

DOUT/RDY (O) |

MSB |

LSB |

|

|

t4 |

|

|

|

t3 |

|

|

t1

SCLK (I)

t2

I = INPUT, O = OUTPUT

Figure 3. Read Cycle Timing Diagram

PDRST (I)

t5

t6

DOUT/RDY (O)

I = INPUT, O = OUTPUT

Figure 4. Resetting the AD7170

08416-004

08416-003

Rev. A | Page 5 of 16

Loading...

Loading...