Analog Devices AD7224LP, AD7224LN, AD7224KR-18, AD7224KR-1, AD7224KP Datasheet

...

a |

LC2MOS |

|

8-Bit DAC with Output Amplifiers |

||

|

|

|

|

|

AD7224 |

|

|

|

FEATURES

8-Bit CMOS DAC with Output Amplifiers Operates with Single or Dual Supplies Low Total Unadjusted Error:

Less Than 1 LSB Over Temperature Extended Temperature Range Operation mP-Compatible with Double Buffered Inputs

Standard 18-Pin DIPs, and 20-Terminal Surface Mount Package and SOIC Package

GENERAL DESCRIPTION

The AD7224 is a precision 8-bit voltage-output, digital-to- analog converter, with output amplifier and double buffered interface logic on a monolithic CMOS chip. No external trims are required to achieve full specified performance for the part.

The double buffered interface logic consists of two 8-bit regis- ters–an input register and a DAC register. Only the data held in the DAC registers determines the analog output of the converter. The double buffering allows simultaneous update in a system containing multiple AD7224s. Both registers may be made transparent under control of three external lines, CS, WR and LDAC. With both registers transparent, the RESET line functions like a zero override; a useful function for system calibration cycles. All logic inputs are TTL and CMOS (5 V) level compatible and the control logic is speed compatible with most 8-bit microprocessors.

Specified performance is guaranteed for input reference voltages from +2 V to +12.5 V when using dual supplies. The part is also specified for single supply operation using a reference of +10 V. The output amplifier is capable of developing +10 V across a

2 kΩ load.

The AD7224 is fabricated in an all ion-implanted high speed Linear Compatible CMOS (LC2MOS) process which has been specifically developed to allow high speed digital logic circuits and precision analog circuits to be integrated on the same chip.

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

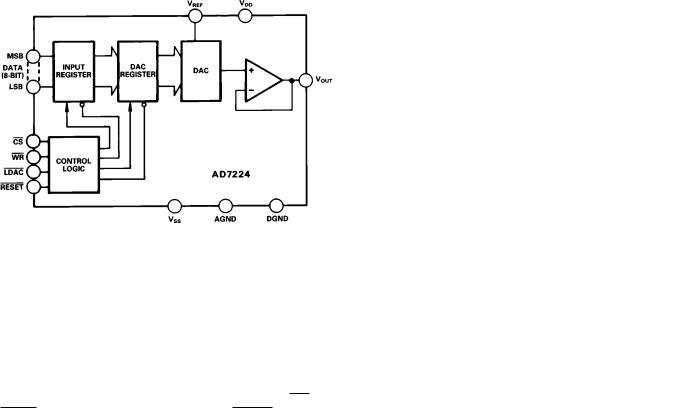

FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

1.DAC and Amplifier on CMOS Chip

The single-chip design of the 8-bit DAC and output amplifier is inherently more reliable than multi-chip designs. CMOS fabrication means low power consumption (35 mW typical with single supply).

2.Low Total Unadjusted Error

The fabrication of the AD7224 on Analog Devices Linear Compatible CMOS (LC2MOS) process coupled with a novel DAC switch-pair arrangement, enables an excellent total unadjusted error of less than 1 LSB over the full operating temperature range.

3.Single or Dual Supply Operation

The voltage-mode configuration of the AD7224 allows operation from a single power supply rail. The part can also be operated with dual supplies giving enhanced performance for some parameters.

4.Versatile Interface Logic

The high speed logic allows direct interfacing to most microprocessors. Additionally, the double buffered interface enables simultaneous update of the AD7224 in multiple DAC systems. The part also features a zero override function.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD7224–SPECIFICATIONS

DUAL SUPPLY |

(VDD = 11.4 V to 16.5 V, VSS = –5 V 6 10%; AGND = DGND = O V; VREF = +2 V to (VDD – 4 V)1 unless otherwise noted. |

||||

All specifications TMIN to TMAX unless otherwise noted.) |

|

|

|||

|

|

K, B, T |

L, C, U |

|

|

Parameter |

|

Versions2 |

Versions2 |

Units |

Conditions/Comments |

|

|

|

|

|

|

STATIC PERFORMANCE |

|

|

|

|

|

Resolution |

|

8 |

8 |

Bits |

|

Total Unadjusted Error |

|

±2 |

±1 |

LSB max |

VDD = +15 V ± 5%, VREF = +10 V |

Relative Accuracy |

|

±1 |

±1/2 |

LSB max |

|

Differential Nonlinearity |

|

±1 |

±1 |

LSB max |

Guaranteed Monotonic |

Full-Scale Error |

|

±3/2 |

±1 |

LSB max |

|

Full-Scale Temperature Coefficient |

±20 |

±20 |

ppm/°C max |

VDD = 14 V to 16.5 V, VREF = +10 V |

|

Zero Code Error |

|

±30 |

±20 |

mV max |

|

Zero Code Error Temperature Coefficient |

±50 |

±30 |

μV/°C typ |

|

|

|

|

|

|

|

|

REFERENCE INPUT |

|

|

|

|

|

Voltage Range |

|

2 to (VDD – 4) |

2 to (VDD – 4) |

V min to V max |

|

Input Resistance |

|

8 |

8 |

kΩ min |

|

Input Capacitance3 |

|

100 |

100 |

pF max |

Occurs when DAC is loaded with all 1s. |

DIGITAL INPUTS |

|

|

|

|

|

Input High Voltage, VINH |

|

2.4 |

2.4 |

V min |

|

Input Low Voltage, VINL |

|

0.8 |

0.8 |

V max |

|

Input Leakage Current |

|

±1 |

±1 |

μA max |

VIN = 0 V or VDD |

Input Capacitance3 |

|

8 |

8 |

pF max |

|

Input Coding |

|

Binary |

Binary |

|

|

|

|

|

|

|

|

DYNAMIC PERFORMANCE |

|

|

V/μs min |

|

|

Voltage Output Slew Rate3 |

2.5 |

2.5 |

|

||

Voltage Output Settling Time3 |

|

|

μs max |

VREF = +10 V; Settling Time to ±1/2 LSB |

|

Positive Full-Scale Change |

5 |

5 |

|||

Negative Full-Scale Change |

7 |

7 |

μs max |

VREF = +10 V; Settling Time to ±1/2 LSB |

|

Digital Feedthrough |

|

50 |

50 |

nV secs typ |

VREF = 0 V |

Minimum Load Resistance |

2 |

2 |

kΩ min |

VOUT = +10 V |

|

POWER SUPPLIES |

|

|

|

|

|

VDD Range |

|

11.4/16.5 |

11.4/16.5 |

V min/V max |

For Specified Performance |

VSS Range |

|

4.5/5.5 |

4.5/5.5 |

V min/V max |

For Specified Performance |

IDD |

|

|

|

|

|

@ 25°C |

|

4 |

4 |

mA max |

Outputs Unloaded; VIN = VINL or VINH |

TMIN to TMAX |

|

6 |

6 |

mA max |

Outputs Unloaded; VIN = VINL or VINH |

ISS |

|

|

|

|

|

@ 25°C |

|

3 |

3 |

mA max |

Outputs Unloaded; VIN = VINL or VINH |

TMIN to TMAX |

|

5 |

5 |

mA max |

Outputs Unloaded; VIN = VINL or VINH |

SWITCHING CHARACTERISTICS3, 4 |

|

|

|

|

|

t1 |

|

|

|

|

|

@ 25°C |

|

90 |

90 |

ns min |

Chip Select/Load DAC Pulse Width |

TMIN to TMAX |

|

90 |

90 |

ns min |

|

t2 |

|

|

|

|

|

@ 25°C |

|

90 |

90 |

ns min |

Write/Reset Pulse Width |

TMIN to TMAX |

|

90 |

90 |

ns min |

|

t3 |

|

|

|

|

|

@ 25°C |

|

0 |

0 |

ns min |

Chip Select/Load DAC to Write Setup Time |

TMIN to TMAX |

|

0 |

0 |

ns min |

|

t4 |

|

|

|

|

|

@ 25°C |

|

0 |

0 |

ns min |

Chip Select/Load DAC to Write Hold Time |

TMIN to TMAX |

|

0 |

0 |

ns min |

|

t5 |

|

|

|

|

|

@ 25°C |

|

90 |

90 |

ns min |

Data Valid to Write Setup Time |

TMIN to TMAX |

|

90 |

90 |

ns min |

|

t6 |

|

|

|

|

|

@ 25°C |

|

10 |

10 |

ns min |

Data Valid to Write Hold Time |

TMIN to TMAX |

|

10 |

10 |

ns min |

|

NOTES

1Maximum possible reference voltage.

2Temperature ranges are as follows: K, L Versions: –40°C to +85°C B, C Versions: –40°C to +85°C T, U Versions: –55°C to +125°C

3Sample Tested at 25°C by Product Assurance to ensure compliance. 4Switching characteristics apply for single and dual supply operation.

Specifications subject to change without notice.

–2– |

REV. B |

AD7224

(VDD = +15 V 6 5%; VSS = AGND = DGND = O V; VREF = +10 V1 unless otherwise noted. |

|||||

SINGLE SUPPLY All specifications TMIN to TMAX unless otherwise noted.) |

|

|

|||

|

K, B, T |

L, C, U |

|

|

|

Parameter |

Versions2 |

Versions2 |

|

Units |

Conditions/Comments |

|

|

|

|

|

|

STATIC PERFORMANCE |

|

|

|

|

|

Resolution |

8 |

8 |

|

Bits |

|

Total Unadjusted Error |

±2 |

±2 |

|

LSB max |

|

Differential Nonlinearity |

±1 |

±1 |

|

LSB max |

Guaranteed Monotonic |

|

|

|

|

|

|

REFERENCE INPUT |

|

|

|

kΩ min |

|

Input Resistance |

8 |

8 |

|

|

|

Input Capacitance3 |

100 |

100 |

|

pF max |

Occurs when DAC is loaded with all 1s. |

DIGITAL INPUTS |

|

|

|

|

|

Input High Voltage, VINH |

2.4 |

2.4 |

|

V min |

|

Input Low Voltage, VINL |

0.8 |

0.8 |

|

V max |

|

Input Leakage Current |

±1 |

±1 |

|

μA max |

VIN = 0 V or VDD |

Input Capacitance3 |

8 |

8 |

|

pF max |

|

Input Coding |

Binary |

Binary |

|

|

|

|

|

|

|

|

|

DYNAMIC PERFORMANCE |

|

|

|

V/μs min |

|

Voltage Output Slew Rate4 |

2 |

2 |

|

|

|

Voltage Output Settling Time4 |

|

|

|

μs max |

Settling Time to ± 1/2 LSB |

Positive Full-Scale Change |

5 |

5 |

|

||

Negative Full-Scale Change |

20 |

20 |

|

μs max |

Settling Time to ± 1/2 LSB |

Digital Feedthrough3 |

50 |

50 |

|

nV secs typ |

VREF = 0 V |

Minimum Load Resistance |

2 |

2 |

|

kΩ min |

VOUT = +10 V |

|

|

|

|

|

|

POWER SUPPLIES |

|

|

|

|

|

VDD Range |

14.25/15.75 |

14.25/15.75 |

|

V min/V max |

For Specified Performance |

IDD |

|

|

|

|

|

@ 25°C |

4 |

4 |

|

mA max |

Outputs Unloaded; VIN = VINL or VINH |

TMIN to TMAX |

6 |

6 |

|

mA max |

Outputs Unloaded; VIN = VINL or VINH |

SWITCHING CHARACTERISTICS3, 4 |

|

|

|

|

|

t1 |

|

|

|

|

|

@ 25°C |

90 |

90 |

|

ns min |

Chip Select/Load DAC Pulse Width |

TMIN to TMAX |

90 |

90 |

|

ns min |

|

t2 |

|

|

|

|

|

@ 25°C |

90 |

90 |

|

ns min |

Write/Reset Pulse Width |

TMIN to TMAX |

90 |

90 |

|

ns min |

|

t3 |

|

|

|

|

|

@ 25°C |

0 |

0 |

|

ns min |

Chip Select/Load DAC to Write Setup Time |

TMIN to TMAX |

0 |

0 |

|

ns min |

|

t4 |

|

|

|

|

|

@ 25°C |

0 |

0 |

|

ns min |

Chip Select/Load DAC to Write Hold Time |

TMIN to TMAX |

0 |

0 |

|

ns min |

|

t5 |

|

|

|

|

|

@ 25°C |

90 |

90 |

|

ns min |

Data Valid to Write Setup Time |

TMIN to TMAX |

90 |

90 |

|

ns min |

|

t6 |

|

|

|

|

|

@ 25°C |

10 |

10 |

|

ns min |

Data Valid to Write Hold Time |

TMIN to TMAX |

10 |

10 |

|

ns min |

|

NOTES

1Maximum possible reference voltage.

2Temperature ranges are as follows: AD7224KN, LN: 0°C to +70°C AD7224BQ, CQ: –25°C to +85°C AD7224TD, UD: –55°C to +125°C 3See Terminology.

4Sample tested at 25°C by Product Assurance to ensure compliance.

Specifications subject to change without notice.

REV. B |

–3– |

Loading...

Loading...