Texas Instruments SN74AC32D, SN74AC32DBLE, SN74AC32DBR, SN74AC32DR, SN74AC32N Datasheet

...

|

|

|

|

|

|

|

|

SN54AC32, SN74AC32 |

||||

|

|

|

|

|

QUADRUPLE 2-INPUT POSITIVE-OR GATES |

|||||||

|

|

|

|

|

SCAS528B ± AUGUST 1995 ± REVISED SEPTEMBER 1996 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

D EPIC (Enhanced-Performance Implanted |

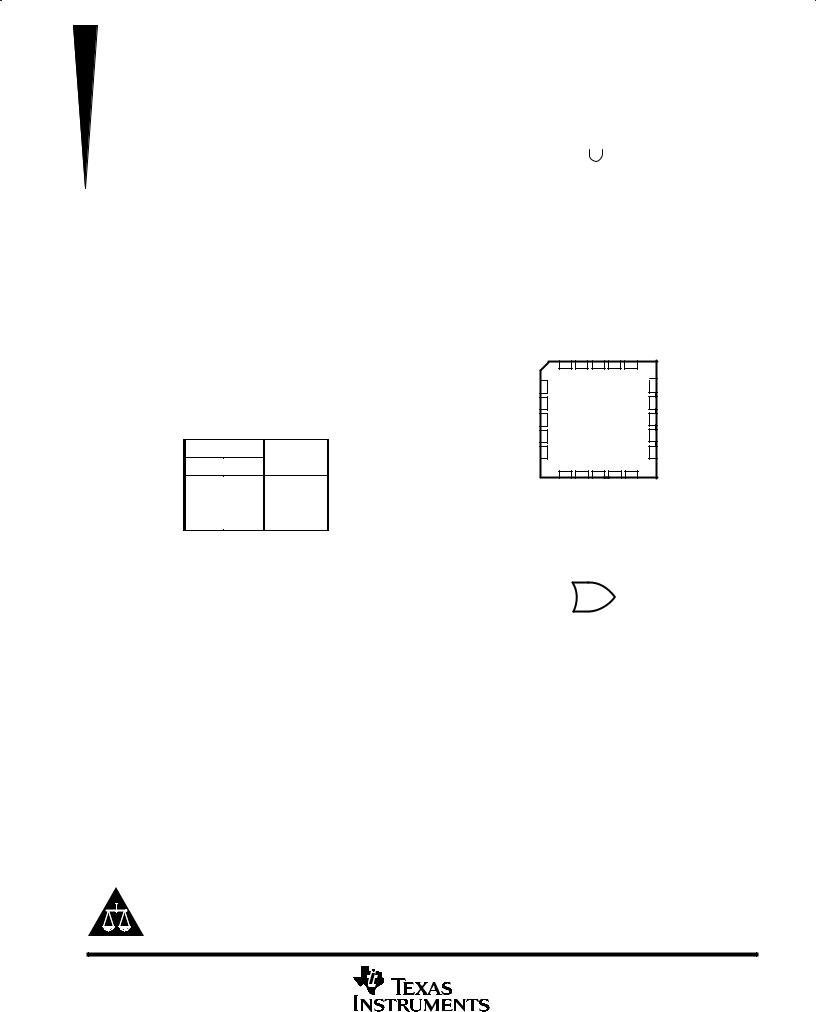

SN54AC32 . . . J OR W PACKAGE |

|||||||||||

CMOS) 1- m Process |

SN74AC32 . . . D, DB, N, OR PW PACKAGE |

|||||||||||

D Package Options Include Plastic |

|

(TOP VIEW) |

|

|

|

|||||||

|

|

|

|

|

|

|

||||||

Small-Outline (D), Shrink Small-Outline |

1A |

|

1 |

14 |

|

VCC |

||||||

|

|

|||||||||||

(DB), and Thin Shrink Small-Outline (PW) |

|

|

||||||||||

|

|

|||||||||||

1B |

|

2 |

13 |

|

4B |

|||||||

Packages, Ceramic Chip Carriers (FK) and |

|

|

||||||||||

1Y |

|

3 |

12 |

|

4A |

|||||||

|

|

|||||||||||

Flatpacks (W), and Standard Plastic (N) and |

|

|

||||||||||

2A |

|

4 |

11 |

|

4Y |

|||||||

|

|

|||||||||||

Ceramic (J) DIPS |

|

|

||||||||||

2B |

|

5 |

10 |

|

3B |

|||||||

|

|

|||||||||||

|

|

|

|

|

|

|

||||||

description |

2Y |

|

6 |

9 |

|

3A |

||||||

|

|

|||||||||||

GND |

|

7 |

8 |

|

3Y |

|||||||

|

|

|||||||||||

|

|

|

|

|

|

|

||||||

The 'AC32 are quadruple 2-input positive-OR |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

||||||

gates. The devices perform the Boolean function |

SN54AC32 . . . FK PACKAGE |

|||||||||||

|

|

|

|

|

||||||||

Y = A + B or Y = A •B in positive logic. |

||||||||||||

|

(TOP VIEW) |

|

|

|

||||||||

The SN54AC32 is characterized for operation |

|

1B |

1A |

NC |

CC |

4B |

|

|||

over the full military temperature range of ±55°C |

|

|

||||||||

|

V |

|

||||||||

|

|

|

|

|

|

|

||||

to 125°C. The SN74AC32 is characterized for |

|

3 |

2 |

1 |

20 19 |

|

||||

operation from ±40°C to 85°C. |

1Y |

4A |

||||||||

4 |

|

|

|

18 |

||||||

|

FUNCTION TABLE |

NC |

5 |

|

|

|

17 |

NC |

||

|

2A |

6 |

|

|

|

16 |

4Y |

|||

|

(each gate) |

|

|

|

||||||

|

NC |

7 |

|

|

|

15 |

NC |

|||

INPUTS |

|

|

|

|

||||||

OUTPUT |

2B |

8 |

|

|

|

14 |

3B |

|||

|

|

|

|

|

||||||

A |

B |

Y |

|

9 |

10 11 12 13 |

|

||||

H |

X |

H |

|

2Y |

GND |

NC |

3Y |

3A |

|

|

X |

H |

H |

|

|

||||||

L |

L |

L |

NC ± No internal connection |

|

||||||

|

|

|

|

|||||||

logic symbol² |

|

|

|

logic diagram, each gate (positive logic) |

|||||

1 |

|

|

|

A |

|

|

|

|

|

1A |

|

≥ 1 |

3 |

1Y |

|

|

|

|

Y |

|

|||||||||

|

|

|

|

|

|||||

2 |

|

|

B |

|

|

|

|

||

|

|

||||||||

|

|

|

|||||||

1B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

2A |

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

5 |

|

|

2Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

2B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

3A |

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

10 |

|

|

3Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

3B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

4A |

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

13 |

|

|

4Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

4B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

² This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the D, DB, J, N, PW, and W packages.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1996, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

SN54AC32, SN74AC32

QUADRUPLE 2-INPUT POSITIVE-OR GATES

SCAS528B ± AUGUST 1995 ± REVISED SEPTEMBER 1996

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . ±0.5 V to 7 |

V |

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±0.5 V to VCC + 0.5 |

V |

Output voltage range, VO (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±0.5 V to VCC + 0.5 |

V |

Input clamp current, IIK (VI < 0 or VI > VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . ± 20 mA |

|

Output clamp current, IOK (VO < 0 or VO > VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . ± 20 mA |

|

Continuous output current, IO (VO = 0 to VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . ± 50 mA |

|

Continuous current through VCC or GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ± 200 mA |

|

Maximum power dissipation at TA = 55°C (in still air) (see Note 2): D package . . . . . . |

. . . . . . . . . . . . . 1.25 W |

|

DB package . . . . . |

. . . . . . . . . . . . . . 0.5 W |

|

N package . . . . . . |

. . . . . . . . . . . . . . 1.1 W |

|

PW package . . . . . |

. . . . . . . . . . . . . . 0.5 W |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . ±65°C to 150°C |

|

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

2.The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils, except for the N package, which has a trace length of zero.

recommended operating conditions (see Note 3)

|

|

|

SN54AC32 |

SN74AC32 |

UNIT |

||

|

|

|

|

|

|

|

|

|

|

|

MIN |

MAX |

MIN |

MAX |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

VCC |

Supply voltage |

|

2 |

6 |

2 |

6 |

V |

|

|

VCC = 3 V |

2.1 |

|

2.1 |

|

|

VIH |

High-level input voltage |

VCC = 4.5 V |

3.15 |

|

3.15 |

|

V |

|

|

VCC = 5.5 V |

3.85 |

|

3.85 |

|

|

|

|

VCC = 3 V |

|

0.9 |

|

0.9 |

|

VIL |

Low-level input voltage |

VCC = 4.5 V |

|

1.35 |

|

1.35 |

V |

|

|

VCC = 5.5 V |

|

1.65 |

|

1.65 |

|

VI |

Input voltage |

|

0 |

VCC |

0 |

VCC |

V |

VO |

Output voltage |

|

0 |

VCC |

0 |

VCC |

V |

|

|

VCC = 3 V |

|

± 12 |

|

± 12 |

|

IOH |

High-level output current |

VCC = 4.5 V |

|

± 24 |

|

± 24 |

mA |

|

|

VCC = 5.5 V |

|

± 24 |

|

± 24 |

|

|

|

VCC = 3 V |

|

12 |

|

12 |

|

IOL |

Low-level output current |

VCC = 4.5 V |

|

24 |

|

24 |

mA |

|

|

VCC = 5.5 V |

|

24 |

|

24 |

|

t / v |

Input transition rise or fall rate |

|

0 |

8 |

0 |

8 |

ns / V |

|

|

|

|

|

|

|

|

TA |

Operating free-air temperature |

|

± 55 |

125 |

± 40 |

85 |

°C |

NOTE 3: Unused inputs must be held high or low to prevent them from floating. |

|

|

|

|

|

||

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...