Texas Instruments SN74ABT2245DBLE, SN74ABT2245DBR, SN74ABT2245DW, SN74ABT2245DWR, SN74ABT2245N Datasheet

...

SN54ABT2245, SN74ABT2245

OCTAL TRANSCEIVERS AND LINE/MOS DRIVERS

WITH 3-STATE OUTPUTS

|

SCBS234D ± SEPTEMBER 1992 ± REVISED MAY 1997 |

|||||||

|

|

|

|

|

|

|

||

D B-Port Outputs Have Equivalent 25-Ω |

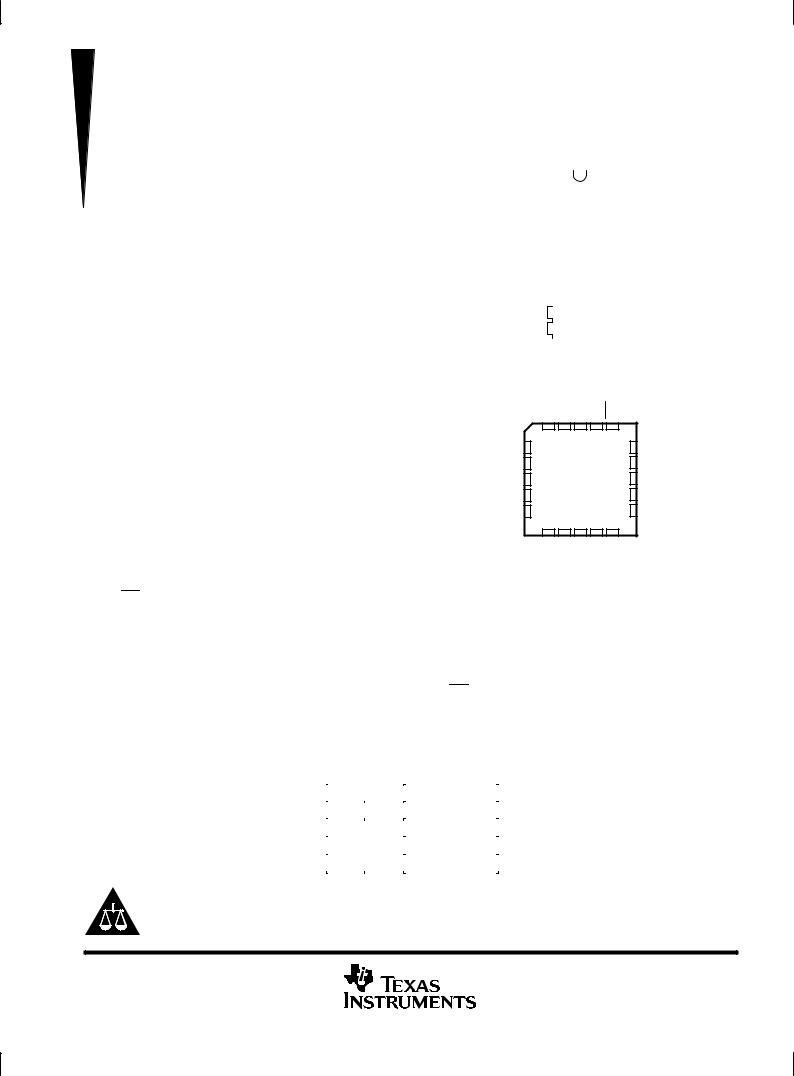

SN54ABT2245 . . . J OR W PACKAGE |

|||||||

Series Resistors, So No External Resistors |

SN74ABT2245 . . . DB, DW, N, OR PW PACKAGE |

|||||||

Are Required |

|

|

(TOP VIEW) |

|

|

|||

|

|

|

|

|

|

|

|

|

D State-of-the-Art EPIC-ΙΙB BiCMOS Design |

DIR |

|

1 |

20 |

|

|

VCC |

|

|

|

|

||||||

Significantly Reduces Power Dissipation |

|

|

|

|||||

A1 |

|

2 |

19 |

|

|

OE |

|

|

|

|

|

|

|||||

D Latch-Up Performance Exceeds 500 mA Per |

A2 |

|

3 |

18 |

|

|

B1 |

|

|

|

|

||||||

JEDEC Standard JESD-17 |

A3 |

|

4 |

17 |

|

|

B2 |

|

|

|

|

||||||

D ESD Protection Exceeds 2000 V Per |

A4 |

|

5 |

16 |

|

|

B3 |

|

|

|

|

||||||

MIL-STD-833, Method 3015; Exceeds 200 V |

A5 |

|

6 |

15 |

|

|

B4 |

|

|

|

|

||||||

Using Machine Model (C = 200 pF, R = 0) |

A6 |

|

7 |

14 |

|

|

B5 |

|

|

|

|

||||||

D Typical VOLP (Output Ground Bounce) < 1 V |

A7 |

|

8 |

13 |

|

|

B6 |

|

|

|

|

||||||

A8 |

9 |

12 |

|

|

B7 |

|||

at VCC = 5 V, TA = 25°C |

|

|

||||||

GND |

10 |

11 |

|

|

B8 |

|||

|

|

|||||||

D High-Impedance State During Power Up |

|

|

||||||

|

|

|

|

|

|

|

|

|

and Power Down |

|

|

|

|

|

|

|

|

D Package Options Include Plastic |

SN54ABT2245 . . . FK PACKAGE |

||||||||

Small-Outline (DW), Shrink Small-Outline |

|

(TOP VIEW) |

|

||||||

|

|

|

|

CC |

|

||||

(DB), and Thin Shrink Small-Outline (PW) |

|

A2 |

A1 |

DIR |

|

||||

Packages, Ceramic Chip Carriers (FK), |

|

V OE |

|

||||||

|

|

|

|

|

|

||||

Plastic (N) and Ceramic (J) DIPs, and |

|

3 |

2 |

1 |

20 19 |

|

|||

Ceramic Flat (W) Package |

|

A3 |

B1 |

||||||

|

4 |

|

|

18 |

|||||

description |

|

|

|

A4 |

5 |

|

|

17 |

B2 |

|

|

|

A5 |

6 |

|

|

16 |

B3 |

|

These octal transceivers and |

line drivers are |

A6 |

7 |

|

|

15 |

B4 |

||

A7 |

8 |

|

|

14 |

B5 |

||||

designed |

for |

asynchronous |

communication |

|

|

||||

|

9 |

10 11 12 13 |

|

||||||

between data buses. The devices transmit data |

|

A8 |

GND |

B8 |

B7 B6 |

|

|||

from the A bus to the B bus or from the B bus to |

|

|

|||||||

|

|

|

|

|

|

||||

the A bus, depending on the logic level at the |

|

|

|

|

|

|

|||

direction-control (DIR) input. The output-enable |

|

|

|

|

|

|

|||

(OE) input can be used to disable the device so |

|

|

|

|

|

|

|||

the buses are effectively isolated. |

|

|

|

|

|

|

|||

The B-port outputs, which are designed to sink up to 12 mA, include equivalent 25-Ω series resistors to reduce |

|||||||||

overshoot and undershoot. |

|

|

|

|

|

|

|

||

When VCC is between 0 and 2.1 V, the device is in the high-impedance state during power up or power down.

However, to ensure the high-impedance state above 2.1 V, OE should be tied to VCC through a pullup resistor; the minimum value of the resistor is determined by the current-sinking/current-sourcing capability of the driver.

The SN54ABT2245 is characterized for operation over the full military temperature range of ±55°C to 125°C. The SN74ABT2245 is characterized for operation from ±40°C to 85°C.

FUNCTION TABLE

|

INPUTS |

OPERATION |

||

|

|

|

||

|

|

|

||

OE |

DIR |

|||

|

||||

|

|

|

|

|

|

L |

L |

B data to A bus |

|

|

L |

H |

A data to B bus |

|

|

H |

X |

Isolation |

|

|

|

|

|

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC-ΙΙB is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1997, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

SN54ABT2245, SN74ABT2245

OCTAL TRANSCEIVERS AND LINE/MOS DRIVERS

WITH 3-STATE OUTPUTS

SCBS234D ± SEPTEMBER 1992 ± REVISED MAY 1997

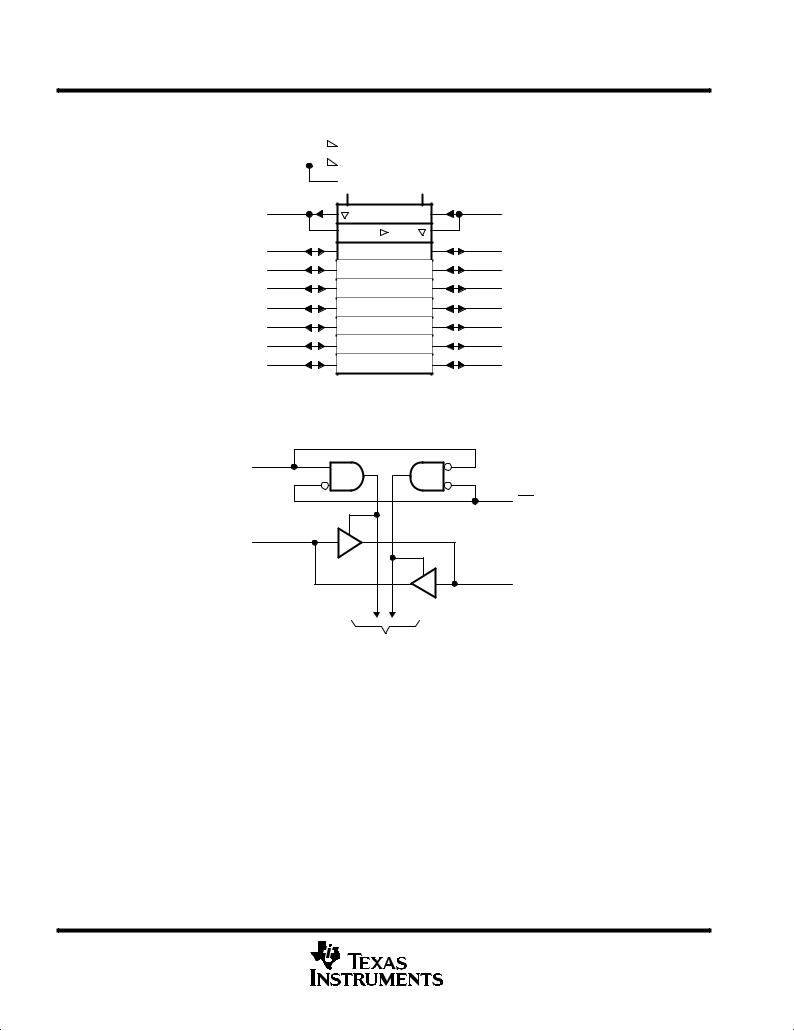

logic symbol²

|

|

|

19 |

|

|

|

G3 |

|||

OE |

||||||||||

|

|

|

|

|||||||

1 |

|

|

|

|||||||

DIR |

|

|

|

3 EN1 [BA] |

||||||

|

|

|

|

|||||||

|

|

|

|

|

|

|

3 EN2 [AB] |

|||

|

|

|

|

|

|

|

|

|

|

|

A1 |

2 |

18 |

1 |

B1 |

|

|

|

2 |

A2 |

3 |

17 |

|

B2 |

|

A3 |

4 |

16 |

|

B3 |

|

A4 |

5 |

15 |

|

B4 |

|

A5 |

6 |

14 |

|

B5 |

|

A6 |

7 |

13 |

|

B6 |

|

A7 |

8 |

12 |

|

B7 |

|

A8 |

9 |

11 |

|

B8 |

² This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

logic diagram (positive logic)

1

DIR

19

OE

2

A1

18

B1

To Seven Other Channels

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

|

|

|

|

|

|

SN54ABT2245, SN74ABT2245 |

||||

|

|

|

|

|

OCTAL TRANSCEIVERS AND LINE/MOS DRIVERS |

|||||

|

|

|

|

|

|

WITH 3-STATE OUTPUTS |

||||

|

|

|

|

|

|

SCBS234D ± SEPTEMBER 1992 ± REVISED MAY 1997 |

||||

|

|

|

|

|

|

|

|

|

|

|

schematic of A-port outputs |

schematic of B-port outputs |

|||||||||

VCC |

|

|

|

VCC |

|

|

|

|||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output |

25 Ω |

|

Output |

||

|

GND |

GND |

All resistor values shown are nominal.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. ±0.5 V to 7 |

V |

Input voltage range, VI (except I/O ports) (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. ±0.5 V to 7 |

V |

Voltage range applied to any output in the high or power-off state, VO . . . . . . . . . . . . . . . . . . . |

±0.5 V to 5.5 |

V |

Current into any output in the low state, IO: SN54ABT2245 (except B port) . . . . . . . . . . . . . . . |

. . . . . . . 96 mA |

|

SN74ABT2245 (except B port) . . . . . . . . . . . . . . . |

. . . . . . 128 mA |

|

B port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 30 mA |

|

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . ±18 mA |

|

Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . ±50 mA |

|

Package thermal impedance, θJA (see Note 2): DB package . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . 115°C/W |

|

DW package . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 97°C/W |

|

N package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . 67°C/W |

|

PW package . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . 128°C/W |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±65°C to 150°C |

|

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

2.The package thermal impedance is calculated in accordance with EIA/JEDEC Std JESD51, except for through-hole packages, which use a trace length of zero.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

Loading...

Loading...