Texas Instruments SN74AHC138, SN74AHC138D, SN74AHC138DBLE, SN74AHC138DBR, SN74AHC138DGVR Datasheet

...

|

SN54AHC138, SN74AHC138 |

|

|

3-LINE TO 8-LINE DECODERS/DEMULTIPLEXERS |

|

|

SCLS258I ± DECEMBER 1995 ± REVISED JANUARY 2000 |

|

|

|

|

D EPIC (Enhanced-Performance Implanted |

SN54AHC138 . . . J OR W PACKAGE |

|

CMOS) Process |

SN74AHC138 . . . D, DB, DGV, N, OR PW PACKAGE |

|

|

(TOP VIEW) |

|

DOperating Range 2-V to 5.5-V VCC

D Designed Specifically for High-Speed |

|

|

A |

1 |

16 |

|

VCC |

Memory Decoders and Data-Transmission |

|

|

B |

2 |

15 |

|

Y0 |

Systems |

|

|

C |

3 |

14 |

|

Y1 |

D Incorporate Three Enable Inputs to Simplify |

|

G2A |

4 |

13 |

|

Y2 |

|

Cascading and/or Data Reception |

|

|

|

5 |

12 |

|

Y3 |

|

G2B |

|

|||||

D Latch-Up Performance Exceeds 250 mA Per |

|

G1 |

6 |

11 |

|

Y4 |

|

JESD 17 |

|

|

Y7 |

7 |

10 |

|

Y5 |

D ESD Protection Exceeds 2000 V Per |

GND |

8 |

9 |

|

Y6 |

||

|

|

|

|

|

|

|

|

MIL-STD-833, Method 3015; Exceeds 200 V |

|

|

|

|

|

|

|

Using Machine Model (C = 200 pF, R = 0) |

SN54AHC138 . . . FK PACKAGE |

||||||

|

|||||||

D Package Options Include Plastic |

|

|

(TOP VIEW) |

|

|||||||||

Small-Outline (D), Shrink Small-Outline |

|

|

B |

A |

NC |

CC |

Y0 |

|

|||||

|

|

|

|

|

|

|

|

|

|||||

(DB), Thin Very Small-Outline (DGV), Thin |

|

V |

|

||||||||||

|

|

|

|

|

|

|

|||||||

Shrink Small-Outline (PW), and Ceramic |

|

|

3 |

2 |

1 |

20 19 |

|

||||||

Flat (W) Packages, Ceramic Chip |

|

C |

Y1 |

||||||||||

|

4 |

|

|

|

18 |

||||||||

Carriers (FK), and Standard Plastic (N) and |

G2A |

5 |

|

|

|

17 |

Y2 |

||||||

Ceramic (J) DIPs |

|

|

|

NC |

6 |

|

|

|

16 |

NC |

|||

description |

|

|

|

|

|

G2B |

7 |

|

|

|

15 |

Y3 |

|

|

|

|

|

|

G1 |

8 |

|

|

|

14 |

Y4 |

||

The |

'AHC138 |

decoders/demultiplexers |

are |

|

9 10 11 12 13 |

|

|||||||

|

Y7 |

GND |

NC |

Y6 |

Y5 |

|

|||||||

designed for high-performance memory-decoding |

|

|

|||||||||||

|

|

|

|

|

|

|

|||||||

and data-routing applications that require very |

NC ± No internal connection |

|

|||||||||||

short |

|

propagation-delay |

times. |

In |

|

||||||||

high-performance memory systems, these |

|

|

|

|

|

|

|

||||||

decoders can be used to minimize the effects of |

|

|

|

|

|

|

|

||||||

system |

decoding. |

When |

employed |

with |

|

|

|

|

|

|

|

||

high-speed memories utilizing a fast enable |

|

|

|

|

|

|

|

||||||

circuit, the delay times of these decoders and the |

|

|

|

|

|

|

|

||||||

enable time of the memory are usually less than |

|

|

|

|

|

|

|

||||||

the typical access time of the memory. This means |

|

|

|

|

|

|

|

||||||

that the effective system delay introduced by the |

|

|

|

|

|

|

|

||||||

decoders is negligible. |

|

|

|

|

|

|

|

|

|

|

|||

The conditions at the binary-select inputs and the three enable inputs select one of eight output lines. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.

The SN54AHC138 is characterized for operation over the full military temperature range of ±55°C to 125°C. The SN74AHC138 is characterized for operation from ±40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

EPIC is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 2000, Texas Instruments Incorporated

On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

SN54AHC138, SN74AHC138

3-LINE TO 8-LINE DECODERS/DEMULTIPLEXERS

SCLS258I ± DECEMBER 1995 ± REVISED JANUARY 2000

FUNCTION TABLE

ENABLE INPUTS |

SELECT INPUTS |

|

|

|

OUTPUTS |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G1 |

|

|

|

|

C |

B |

A |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

G2A |

G2B |

||||||||||||||

X |

H |

X |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

||

X |

X |

H |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

||

L |

X |

X |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

||

H |

L |

L |

L |

L |

L |

L |

H |

H |

H |

H |

H |

H |

H |

||

H |

L |

L |

L |

L |

H |

H |

L |

H |

H |

H |

H |

H |

H |

||

H |

L |

L |

L |

H |

L |

H |

H |

L |

H |

H |

H |

H |

H |

||

H |

L |

L |

L |

H |

H |

H |

H |

H |

L |

H |

H |

H |

H |

||

H |

L |

L |

H |

L |

L |

H |

H |

H |

H |

L |

H |

H |

H |

||

H |

L |

L |

H |

L |

H |

H |

H |

H |

H |

H |

L |

H |

H |

||

H |

L |

L |

H |

H |

L |

H |

H |

H |

H |

H |

H |

L |

H |

||

H |

L |

L |

H |

H |

H |

H |

H |

H |

H |

H |

H |

H |

L |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

logic symbols (alternatives)²

1 |

|

BIN/OCT |

0 |

15 |

Y0 |

1 |

|||||||

|

A |

|

|

1 |

|

|

14 |

|

A |

|

|

||

|

|

|

|

|

|

||||||||

2 |

|

|

|

|

|

2 |

|||||||

|

B |

|

|

2 |

|

|

1 |

|

Y1 |

|

B |

|

|

|

|

|

|

|

|

|

|||||||

3 |

|

|

|

|

13 |

|

3 |

||||||

|

C |

|

|

4 |

|

|

2 |

12 |

Y2 |

|

C |

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

3 |

Y3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

6 |

|

& |

|

11 |

6 |

||||||||

|

|

|

|

||||||||||

G1 |

|

|

|

|

4 |

|

Y4 |

G1 |

|

||||

|

|

|

|

|

|||||||||

|

|

4 |

|

|

EN |

|

10 |

|

|

|

4 |

||

|

|

|

|

|

|

||||||||

G2A |

|

|

5 |

|

Y5 |

G2A |

|||||||

|

|

|

|

||||||||||

|

5 |

|

|

|

6 |

9 |

Y6 |

|

5 |

||||

G2B |

|

|

|

7 |

G2B |

||||||||

|

|

|

|

|

|

|

7 |

Y7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

² These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the D, DB, DGV, J, N, PW, and W packages.

0 |

DMUX |

0 |

15 |

Y0 |

|

|

0 |

14 |

|||

|

G |

1 |

Y1 |

||

2 |

7 |

13 |

|||

|

|

2 |

Y2 |

||

|

|

12 |

|||

|

|

|

3 |

Y3 |

|

& |

|

|

11 |

||

|

|

||||

|

|

|

|

||

|

|

|

4 |

Y4 |

|

|

|

|

10 |

||

|

|

|

5 |

Y5 |

|

|

|

|

9 |

||

|

|

|

6 |

Y6 |

|

|

|

|

7 |

||

|

|

|

7 |

Y7 |

|

|

|

|

|

||

|

|

|

|

|

|

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

SN54AHC138, SN74AHC138 3-LINE TO 8-LINE DECODERS/DEMULTIPLEXERS

SCLS258I ± DECEMBER 1995 ± REVISED JANUARY 2000

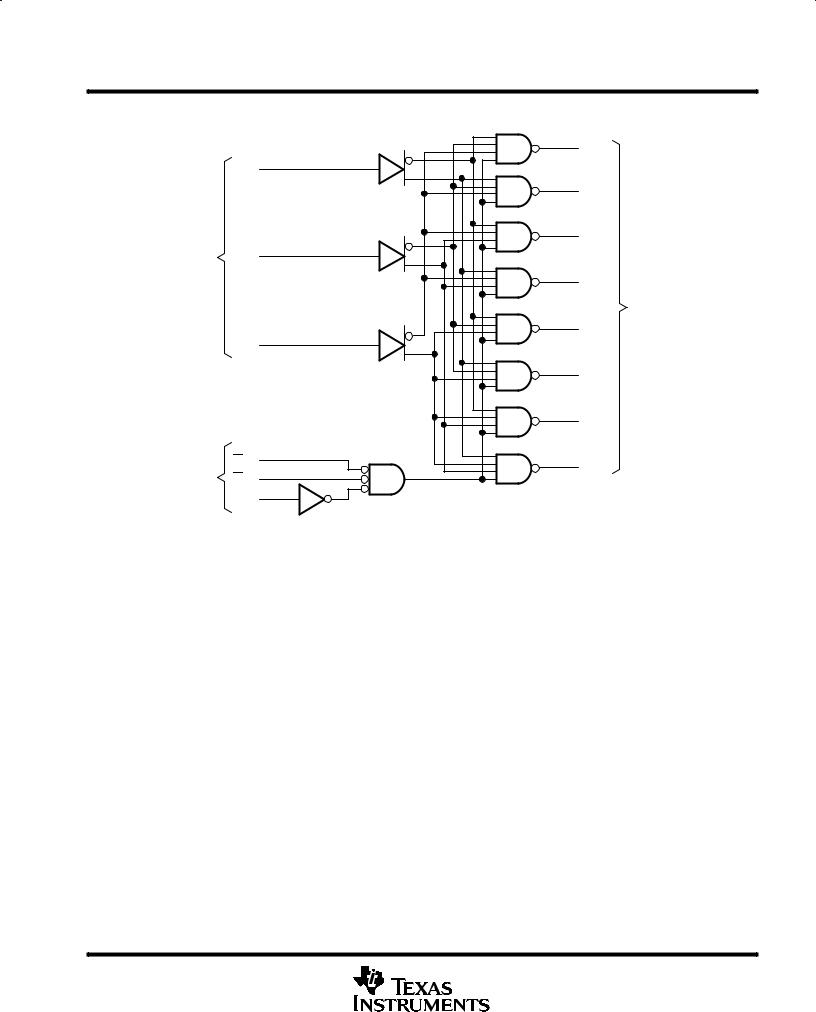

logic diagram (positive logic)

|

|

|

15 |

Y0 |

|

|

|

|

|

||

|

A |

1 |

|

|

|

|

|

|

|

||

|

|

|

14 |

Y1 |

|

|

|

|

|

||

|

|

|

13 |

Y2 |

|

Select |

|

2 |

|

||

B |

|

|

|||

Inputs |

|

|

|

||

|

|

12 |

|

||

|

|

|

Y3 |

||

|

|

|

|

||

|

|

|

|

Data |

|

|

|

|

11 |

Outputs |

|

|

|

|

Y4 |

||

|

|

3 |

|

||

|

C |

|

|

||

|

|

|

|

||

|

|

|

10 |

Y5 |

|

|

|

|

|

||

|

|

|

9 |

Y6 |

|

|

|

|

|

||

|

G2A |

4 |

7 |

|

|

Enable |

5 |

Y7 |

|||

|

|

||||

G2B |

|

|

|||

Inputs |

6 |

|

|

||

|

|

|

|||

|

G1 |

|

|

||

|

|

|

|

Pin numbers shown are for the D, DB, DGV, J, N, PW, and W packages.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . ±0.5 V to 7 |

V |

Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . ±0.5 V to 7 |

V |

Output voltage range, VO (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±0.5 V to VCC + 0.5 |

V |

Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±20 mA |

|

Output clamp current, IOK (VO < 0 or VO > VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±20 mA |

|

Continuous output current, IO (VO = 0 to VCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±25 mA |

|

Continuous current through VCC or GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±75 mA |

|

Package thermal impedance, θJA (see Note 2): D package . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . 73°C/W |

|

DB package . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . 82°C/W |

|

DGV package . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . 120°C/W |

|

N package . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . 67°C/W |

|

PW package . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . 108°C/W |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . ±65°C to 150°C |

|

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed. 2. The package thermal impedance is calculated in accordance with JESD 51.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

Loading...

Loading...