Fairchild Semiconductor MM74HC4316CW, MM74HC4316WMX, MM74HC4316SJ, MM74HC4316SJX, MM74HC4316WM Datasheet

...

February 1984

Revised February 1999

MM74HC4316

Quad Analog Switch with Level Translator

General Description

The MM74HC4316 devices are digitally controlled analog switches implemented in advanced silicon-gate CMOS technology. These switches have low “ON” resistance and low “OFF” leakages. They are bidirectional switches, thus any analog input may be used as an output and vice-versa. Three supply pins are provided on the MM74HC4316 to implement a level translator which enables this circuit to operate with 0–6V logic levels and up to ±6V analog switch levels. The MM74HC4316 also has a common enable input in addition to each switch's control which when LOW will disable all switches to their OFF state. All analog inputs

and outputs and digital inputs are protected from electrostatic damage by diodes to VCC and ground.

Features

■Typical switch enable time: 20 ns

■Wide analog input voltage range: ±6V

■Low “ON” resistance:

50 typ. (VCC−VEE = 4.5V) 30 typ. (VCC−VEE = 9V)

■Low quiescent current: 80 μA maximum (74HC)

■Matched switch characteristics

■Individual switch controls plus a common enable

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

MM74HC4316M |

M16A |

16-Lead Small Outline Integrated Package (SOIC), JEDEC MS-012, 0.150” Narrow |

|

|

|

MM74HC4316SJ |

M16D |

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

MM74HC4316MTC |

MTC16 |

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-1536, 4.4mm Wide |

|

|

|

MM74HC4316N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

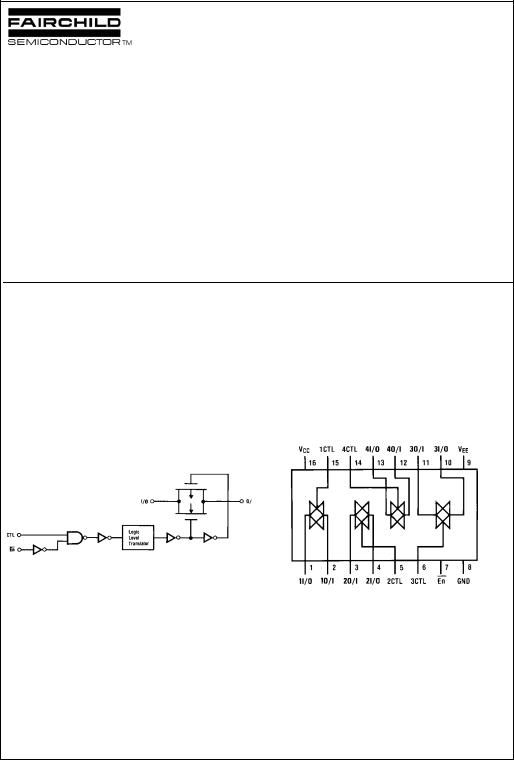

Logic Diagram |

Connection Diagram |

|

Pin Assignments for DIP, SOIC, SOP and TSSOP |

Top View

Truth Table

|

|

Inputs |

|

Switch |

|

|

|

|

|

||

En |

|

CTL |

I/O–O/I |

||

|

|

|

|

|

|

|

H |

|

X |

“OFF” |

|

|

L |

|

L |

“OFF” |

|

|

L |

|

H |

“ON” |

|

|

|

|

|

|

|

Translator Level with Switch Analog Quad MM74HC4316

© 1999 Fairchild Semiconductor Corporation |

DS005369.prf |

www.fairchildsemi.com |

MM74HC4316

Absolute Maximum Ratings(Note 1)

(Note 2) |

|

Supply Voltage (VCC) |

−0.5 to +7.5V |

Supply Voltage (VEE) |

+0.5 to −7.5V |

DC Control Input Voltage (VIN) |

−1.5 to VCC +1.5V |

DC Switch I/O Voltage (VIO) |

VEE−0.5 to VCC +0.5V |

Clamp Diode Current (IIK, IOK) |

±20 mA |

DC Output Current, per pin (IOUT) |

±25 mA |

DC VCC or GND Current, per pin (ICC) |

±50 mA |

Storage Temperature Range (TSTG) |

−65°C to +150°C |

Power Dissipation (PD) |

|

(Note 3) |

600 mW |

S.O. Package only |

500 mW |

Lead Temperature (TL) |

260°C |

(Soldering 10 seconds) |

Recommended Operating

Conditions

|

Min |

Max |

Units |

Supply Voltage (VCC) |

2 |

6 |

V |

Supply Voltage (VEE) |

0 |

−6 |

V |

DC Input or Output Voltage |

|

|

|

(VIN, VOUT) |

0 |

VCC |

V |

Operating Temperature Range (TA) |

−40 |

+85 |

°C |

Input Rise or Fall Times |

|

|

|

(tr, tf) VCC = 2.0V |

|

1000 |

ns |

VCC = 4.5V |

|

500 |

ns |

VCC = 6.0V |

|

400 |

ns |

VCC = 12.0V |

|

250 |

ns |

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating — plastic “N” package: − 12 mW/°C from 65°C to 85°C.

DC Electrical Characteristics (Note 4)

Symbol |

Parameter |

Conditions |

VEE |

VCC |

TA = 25°C |

TA = −40 to 85°C |

TA = −55 to 125°C |

Units |

|

Typ |

|

Guaranteed Limits |

|||||||

|

|

|

|

|

|

|

|

|

|

VIH |

Minimum HIGH Level |

|

|

2.0V |

|

1.5 |

1.5 |

1.5 |

V |

|

Input Voltage |

|

|

4.5V |

|

3.15 |

3.15 |

3.15 |

V |

|

|

|

|

6.0V |

|

4.2 |

4.2 |

4.2 |

V |

|

|

|

|

|

|

|

|

|

|

VIL |

Maximum LOW Level |

|

|

2.0V |

|

0.5 |

0.5 |

0.5 |

V |

|

Input Voltage |

|

|

4.5V |

|

1.35 |

1.35 |

1.35 |

V |

|

|

|

|

6.0V |

|

1.8 |

1.8 |

1.8 |

V |

|

|

|

|

|

|

|

|

|

|

RON |

Minimum “ON” Resistance |

VCTL = VIH, IS = 2.0 mA |

GND |

4.5V |

100 |

170 |

200 |

220 |

Ω |

|

(Note 5) |

VIS = VCC to VEE |

−4.5V |

4.5V |

40 |

85 |

105 |

110 |

Ω |

|

|

(Figure 1) |

−6.0V |

6.0V |

30 |

70 |

85 |

90 |

Ω |

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

2.0V |

100 |

180 |

215 |

240 |

Ω |

|

|

VCTL = VIH, IS = 2.0 mA |

GND |

4.5V |

40 |

80 |

100 |

120 |

Ω |

|

|

VIS = VCC or VEE |

−4.5V |

4.5V |

50 |

60 |

75 |

80 |

Ω |

|

|

(Figure 1) |

−6.0V |

6.0V |

20 |

40 |

60 |

70 |

Ω |

|

|

|

|

|

|

|

|

|

|

RON |

Maximum “ON” Resistance |

VCTL = VIH |

GND |

4.5V |

10 |

15 |

20 |

20 |

Ω |

|

Matching |

VIS = VCC to VEE |

−4.5V |

4.5V |

5 |

10 |

15 |

15 |

Ω |

|

|

|

−6.0V |

6.0V |

5 |

10 |

15 |

15 |

Ω |

|

|

|

|

|

|

|

|

|

|

IIN |

Maximum Control |

VIN = VCC or GND |

GND |

6.0V |

|

±0.1 |

±1.0 |

±1.0 |

μA |

|

Input Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIZ |

Maximum Switch “OFF” |

VOS = VCC or VEE |

GND |

6.0V |

|

±60 |

±600 |

±600 |

nA |

|

Leakage Current |

VIS = VEE or VCC |

−6.0V |

6.0V |

|

±100 |

±1000 |

±1000 |

nA |

|

|

VCTL = VIL (Figure 2) |

|

|

|

|

|

|

|

IIZ |

Maximum Switch “ON” |

VIS = VCC to VEE |

GND |

6.0V |

|

±40 |

±150 |

±150 |

nA |

|

Leakage Current |

VCTL = VIH, VOS = OPEN |

−6.0V |

6.0V |

|

±60 |

±300 |

±300 |

nA |

|

|

(Figure 3) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC |

Maximum Quiescent |

VIN = VCC or GND |

GND |

6.0V |

|

2.0 |

20 |

40 |

μA |

|

Supply Current |

IOUT = 0 μA |

−6.0V |

6.0V |

|

8.0 |

80 |

160 |

μA |

Note 4: For a power supply of 5V ±10% the worst case on resistances (RON) occurs for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case VIH and VIL occur at VCC=5.5V and 4.5V respectively. (The VIH value at 5.5V is 3.85V.) The worst case leakage current occurs for CMOS at the higher voltage and so the 5.5V values should be used.

Note 5: At supply voltages (VCC–VEE) approaching 2V the analog switch on resistance becomes extremely non-linear. Therefore it is recommended that these devices be used to transmit digital only when using these supply voltages.

www.fairchildsemi.com |

2 |

tPLH |

Delay Switch |

|

GND |

4.5V |

5 |

10 |

13 |

15 |

ns |

MM74HC4316 |

AC Electrical Characteristics |

|

|

|

|

|

|

|

|

||

VCC = 2.0V−6.0V, VEE = 0V−6V, CL = 50 pF (unless otherwise specified) |

|

|

|

|

|

|

||||

Symbol |

Parameter |

Conditions |

VEE |

VCC |

TA = +25°C |

TA = −40°C to +85°C |

TA = −55°C to +125°C |

Units |

|

|

Typ |

|

Guaranteed Limits |

|

|||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

tPHL, |

Maximum Propagation |

|

GND |

2.0V |

25 |

50 |

63 |

75 |

ns |

|

|

In to Out |

|

−4.5V |

4.5V |

4 |

8 |

12 |

14 |

ns |

|

|

|

|

−6.0V |

6.0V |

3 |

7 |

11 |

13 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

tPZL, |

Maximum Switch |

RL = 1 kΩ |

GND |

2.0V |

30 |

165 |

206 |

250 |

ns |

|

tPZH |

Turn “ON” Delay |

|

GND |

4.5V |

20 |

35 |

43 |

53 |

ns |

|

|

(Control) |

|

−4.5V |

4.5V |

15 |

32 |

39 |

48 |

ns |

|

|

|

|

−6.0V |

6.0V |

14 |

30 |

37 |

45 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

tPHZ, |

Maximum Switch |

RL = 1 kΩ |

GND |

2.0V |

45 |

250 |

312 |

375 |

ns |

|

tPLZ |

Turn “OFF” Delay |

|

GND |

4.5V |

25 |

50 |

63 |

75 |

ns |

|

|

(Control) |

|

−4.5V |

4.5V |

20 |

44 |

55 |

66 |

ns |

|

|

|

|

−6.0V |

6.0V |

20 |

44 |

55 |

66 |

|

|

|

|

|

|

|

|

|

|

|

|

|

tPZL, |

Maximum Switch |

|

GND |

2.0V |

35 |

205 |

256 |

308 |

ns |

|

tPZH |

Turn “ON” Delay |

|

GND |

4.5V |

20 |

41 |

52 |

62 |

ns |

|

|

(Enable) |

|

−4.5V |

4.5V |

19 |

38 |

48 |

57 |

ns |

|

|

|

|

−6.0V |

6.0V |

18 |

36 |

45 |

54 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

tPLZ, |

Maximum Switch |

|

GND |

2.0V |

58 |

265 |

330 |

400 |

ns |

|

tPHZ |

Turn “OFF” Delay |

|

GND |

4.5V |

28 |

53 |

67 |

79 |

ns |

|

|

(Enable) |

|

−4.5V |

4.5V |

23 |

47 |

59 |

70 |

ns |

|

|

|

|

−6.0V |

6.0V |

21 |

47 |

59 |

70 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

fMAX |

Minimum Frequency |

RL = 600Ω, VIS = 2VPP |

0V |

4.5 |

40 |

|

|

|

MHz |

|

|

Response (Figure 7) |

at (VCC−VEE/2) |

−4.5V |

4.5V |

100 |

|

|

|

MHz |

|

|

20 log (VOS/VIS)= −3 dB |

(Note 6) (Note 7) |

|

|

|

|

|

|

|

|

|

Control to Switch |

RL = 600Ω, F = 1 MHz |

0V |

4.5V |

100 |

|

|

|

mV |

|

|

Feedthrough Noise |

CL = 50 pF |

−4.5V |

4.5V |

250 |

|

|

|

mV |

|

|

(Figure 8) |

(Note 7) (Note 8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Crosstalk Between |

RL = 600Ω, F = 1 MHz |

|

|

−52 |

|

|

|

|

|

|

any Two Switches |

|

0V |

4.5V |

|

|

|

dB |

|

|

|

(Figure 9) |

|

−4.5V |

4.5V |

−50 |

|

|

|

dB |

|

|

|

|

|

|

|

|

|

|

|

|

|

Switch OFF Signal |

RL = 600Ω, F = 1 MHz |

|

|

|

|

|

|

|

|

|

Feedthrough Isolation |

VCTL = VIL, |

0V |

4.5V |

−42 |

|

|

|

dB |

|

|

(Figure 10) |

(Note 7) (Note 8) |

−4.5V |

4.5V |

−44 |

|

|

|

dB |

|

|

|

|

|

|

|

|

|

|

|

|

THD |

Sinewave Harmonic |

RL = 10 KΩ, CL = 50 pF, |

|

|

|

|

|

|

|

|

|

Distortion |

F = 1 KHz |

|

|

|

|

|

|

|

|

|

(Figure 11) |

VIS = 4VPP |

0V |

4.5V |

0.013 |

|

|

|

% |

|

|

|

VIS = 8VPP |

−4.5V |

4.5V |

0.008 |

|

|

|

% |

|

CIN |

Maximum Control |

|

|

|

5 |

|

|

|

pF |

|

|

Input Capacitance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CIN |

Maximum Switch |

|

|

|

35 |

|

|

|

pF |

|

|

Input Capacitance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CIN |

Maximum Feedthrough |

VCTL = GND |

|

|

0.5 |

|

|

|

pF |

|

|

Capacitance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CPD |

Power Dissipation |

|

|

|

15 |

|

|

|

pF |

|

|

Capacitance |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Note 6: |

Adjust 0 dBm for F = 1 KHz |

(Null RL/Ron Attenuation). |

|

|

|

|

|

|

|

|

Note 7: VIS is centered at VCC–VEE/2. |

|

|

|

|

|

|

|

|

||

Note 8: Adjust for 0 dBm. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

www.fairchildsemi.com |

Loading...

Loading...