Fairchild Semiconductor MM74C374WM, MM74C374WMX, MM74C374CW, MM74C374N Datasheet

October 1987

Revised January 1999

MM74C373 • MM74C374

3-STATE Octal D-Type Latch •

3-STATE Octal D-Type Flip-Flop

General Description

The MM74C373 and MM74C374 are integrated, complementary MOS (CMOS), 8-bit storage elements with 3- STATE outputs. These outputs have been specially designed to drive high capacitive loads, such as one might find when driving a bus, and to have a fan out of 1 when driving standard TTL. When a high logic level is applied to the OUTPUT DISABLE input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements.

The MM74C373 is an 8-bit latch. When LATCH ENABLE is high, the Q outputs will follow the D inputs. When LATCH ENABLE goes low, data at the D inputs, which meets the set-up and hold time requirements, will be retained at the outputs until LATCH ENABLE returns high again.

The MM74C374 is an 8-bit, D-type, positive-edge triggered flip-flop. Data at the D inputs, meeting the set-up and hold time requirements, is transferred to the Q outputs on posi- tive-going transitions of the CLOCK input.

Both the MM74C373 and the MM74C374 are being assembled in 20-pin dual-in-line packages with 0.300” pin centers.

Features

■Wide supply voltage range: 3V to 15V

■High noise immunity: 0.45 VCC (typ.)

■Low power consumption

■TTL compatibility:

Fan out of 1driving standard TTL

■Bus driving capability

■3-STATE outputs

■Eight storage elements in one package

■Single CLOCK/LATCH ENABLE and OUTPUT DISABLE control inputs

■20-pin dual-in-line package with 0.300” centers takes half the board space of a 24-pin package

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

MM74C373M |

M20B |

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide |

|

|

|

MM74C373N |

N20A |

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

MM74C374M |

M20B |

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide |

|

|

|

MM74C374N |

N20A |

20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Flop-Flip Type-D Octal STATE-3 • Latch Type-D Octal STATE-3 MM74C374 • MM74C373

© 1999 Fairchild Semiconductor Corporation |

DS005906.prf |

www.fairchildsemi.com |

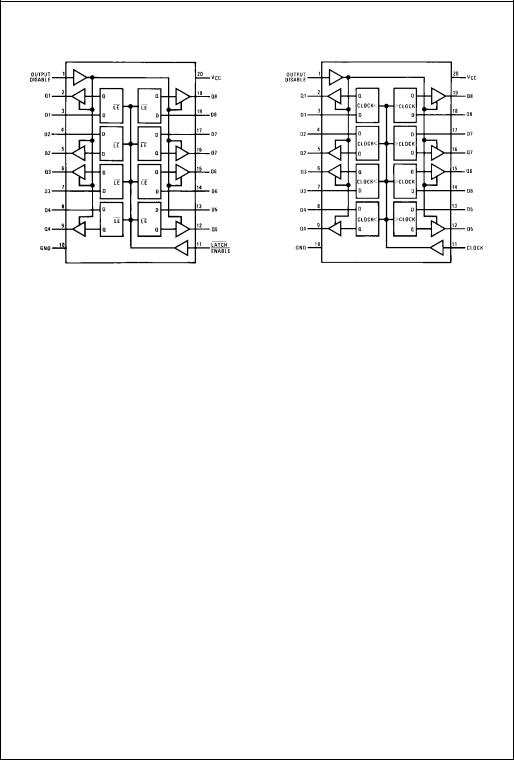

MM74C373 • MM74C374

Connection Diagrams

Pin Assignments for DIP and SOIC

MM74C373 |

MM74C374 |

Top View |

Top View |

Truth Tables

MM74C373

|

|

|

|

|

|

|

|

Output |

|

|

LATCH |

|

D |

Q |

|

Disable |

|

|

|

|

|

||

ENABLE |

|

|

|

||||

|

|

|

|

|

|

|

|

L |

|

|

H |

|

H |

H |

|

L |

|

|

H |

|

L |

L |

|

L |

|

|

L |

|

X |

Q |

|

H |

|

|

X |

|

X |

Hi-Z |

|

|

|

|

|

|

|

|

|

L = LOW logic level H = HIGH logic level X = Irrelevant

= LOW-to-HIGH logic level transition Q = Preexisting output level

Hi-Z = High impedance output state

MM74C374

Output |

Clock |

D |

Q |

Disable |

|

|

|

|

|

|

|

L |

|

H |

H |

L |

|

L |

L |

L |

L |

X |

Q |

L |

H |

X |

Q |

H |

X |

X |

Hi-Z |

|

|

|

|

www.fairchildsemi.com |

2 |

Block Diagrams

MM74C373 (1 of 8 Latches)

MM74C374 (1 of 8 Flip-Flops)

MM74C374 • MM74C373

3 |

www.fairchildsemi.com |

MM74C373 • MM74C374

Absolute Maximum Ratings(Note 1)

Voltage at Any Pin |

−0.3V to VCC + 0.3V |

Operating Temperature Range (TA) |

−40°C to +85°C |

MM74C373 |

|

Storage Temperature Range (TS) |

−65°C to +150°C |

Power Dissipation |

|

Dual-In-Line |

700 mW |

Small Outline |

500 mW |

Operating VCC Range |

3V to 15V |

Absolute Maximum VCC |

18V |

Lead Temperature (TL) |

260°C |

(Soldering, 10 seconds) |

Note 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed. Except for “Operating Temperature Range” they are not meant to imply that the devices should be operated at these limits. The table of “Electrical Characteristics” provides conditions for actual device operation.

DC Electrical Characteristics

Min/Max limits apply across temperature range unless otherwise noted

Symbol |

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

CMOS TO CMOS |

|

|

|

|

|

|

|

|

|

|

|

|

|

VIN(1) |

Logical “1” Input Voltage |

VCC = 5V |

3.5 |

|

|

V |

|

|

VCC = 10V |

8.0 |

|

|

V |

VIN(0) |

Logical “0” Input Voltage |

VCC = 5V |

|

|

1.5 |

V |

|

|

VCC = 10V |

|

|

2.0 |

V |

VOUT(1) |

Logical “1” Output Voltage |

VCC = 5V, IO = −10 μA |

4.5 |

|

|

V |

|

|

VCC = 10V, IO = −10 μA |

9.0 |

|

|

V |

VOUT(0) |

Logical “0” Output Voltage |

VCC = 5V, IO = 10 μA |

|

|

0.5 |

V |

|

|

VCC = 10V, IO = 10 μA |

|

|

1.0 |

V |

IIN(1) |

Logical “1” Input Current |

VCC = 15V, VIN = 15V |

|

0.005 |

1.0 |

μA |

IIN(0) |

Logical “0” Input Current |

VCC = 15V, VIN = 0V |

−1.0 |

−0.005 |

|

μA |

IOZ |

3-STATE Leakage Current |

VCC = 15V, VO = 15V |

|

0.005 |

1.0 |

μA |

|

|

VCC = 15V, VO = 0V |

−1.0 |

−0.005 |

|

μA |

ICC |

Supply Current |

VCC = 15V |

|

0.05 |

300 |

μA |

CMOS/LPTTL |

INTERFACE |

|

|

|

|

|

|

|

|

|

|

|

|

VIN(1) |

Logical “1” Input Voltage |

VCC = 4.75V |

VCC − 1.5 |

|

|

V |

VIN(0) |

Logical “0” Input Voltage |

VCC = 4.75V |

|

|

0.8 |

V |

VOUT(1) |

Logical “1” Output Voltage |

VCC = 4.75V, IO = −360 μA |

VCC − 0.4 |

|

|

V |

|

|

VCC = 4.75V, IO = −1.6 mA |

2.4 |

|

|

V |

VOUT(0) |

Logical “0” Output Voltage |

VCC = 4.75V, IO = 1.6 mA |

|

|

0.4 |

V |

OUTPUT DRIVE (Short Circuit Current) |

|

|

|

|

|

|

|

|

|

|

|

|

|

ISOURCE |

Output Source Current |

VCC = 5V, VOUT = 0V |

−12 |

−24 |

|

mA |

|

|

TA = 25°C (Note 2) |

|

|

|

|

ISOURCE |

Output Source Current |

VCC = 10V, VOUT = 0V |

−24 |

−48 |

|

mA |

|

|

TA = 25°C (Note 2) |

|

|

|

|

ISINK |

Output Sink Current |

VCC = 5V, VOUT = VCC |

6 |

12 |

|

mA |

|

(N-Channel) |

TA = 25°C (Note 2) |

|

|

|

|

ISINK |

Output Sink Current |

VCC = 10V, VOUT = VCC |

24 |

48 |

|

mA |

|

(N-Channel) |

TA = 25°C (Note 2) |

|

|

|

|

Note 2: These are peak output current capabilities. Continuous output current is rated at 12 mA max.

www.fairchildsemi.com |

4 |

Loading...

Loading...