Fairchild Semiconductor MM74HC161MX, MM74HC161MTC, MM74HC161N, MM74HC161MTCX, MM74HC161M Datasheet

...

September 1983

Revised February 1999

MM74HC161 • MM74HC163

Synchronous Binary Counter with Asynchronous Clear

• Synchronous Binary Counter with Synchronous Clear

General Description

The MM74HC161 and MM74HC163 synchronous presettable counters utilize advanced silicon-gate CMOS technology and internal look-ahead carry logic for use in high speed counting applications. They offer the high noise immunity and low power consumption inherent to CMOS with speeds similar to low power Schottky TTL. The HC161 and the HC163 are 4 bit binary counters. All flip-flops are clocked simultaneously on the LOW-to-HIGH transition (positive edge) of the CLOCK input waveform.

These counters may be preset using the LOAD input. Presetting of all four flip-flops is synchronous to the rising edge of CLOCK. When LOAD is held LOW counting is disabled and the data on the A, B, C, and D inputs is loaded into the counter on the rising edge of CLOCK. If the load input is taken HIGH before the positive edge of CLOCK the count operation will be unaffected.

All of these counters may be cleared by utilizing the CLEAR input. The clear function on the MM74HC163 counter is synchronous to the clock. That is, the counters are cleared on the positive edge of CLOCK while the clear input is held LOW.

The MM74HC161 counter is cleared asynchronously. When the CLEAR is taken LOW the counter is cleared immediately regardless of the CLOCK.

Two active HIGH enable inputs (ENP and ENT) and a RIPPLE CARRY (RC) output are provided to enable easy cascading of counters. Both ENABLE inputs must be HIGH to count. The ENT input also enables the RC output. When enabled, the RC outputs a positive pulse when the counter overflows. This pulse is approximately equal in duration to the HIGH level portion of the QA output. The RC output is fed to successive cascaded stages to facilitate easy implementation of N-bit counters.

All inputs are protected from damage due to static discharge by diodes to VCC and ground.

Features

■Typical operating frequency: 40 MHz

■Typical propagation delay; clock to Q: 18 ns

■Low quiescent current: 80 μA maximum (74HC Series)

■Low input current: 1 μA maximum

■Wide power supply range: 2–6V

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

MM74HC161M |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow |

|

|

|

MM74HC161SJ |

M16D |

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

MM74HC161MTC |

MTC16 |

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |

|

|

|

MM74HC161N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

MM74HC163M |

M16A |

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow |

|

|

|

MM74HC163SJ |

M16D |

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

MM74HC163MTC |

MTC16 |

16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |

|

|

|

MM74HC163N |

N16E |

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

with Counter |

MM74HC161 |

Synchronous |

MM74HC163 • |

Clear |

Synchronous |

|

Binary Synchronous • Clear Asynchronous with Counter Binary |

© 1999 Fairchild Semiconductor Corporation |

DS005008.prf |

www.fairchildsemi.com |

MM74HC161 • MM74HC163

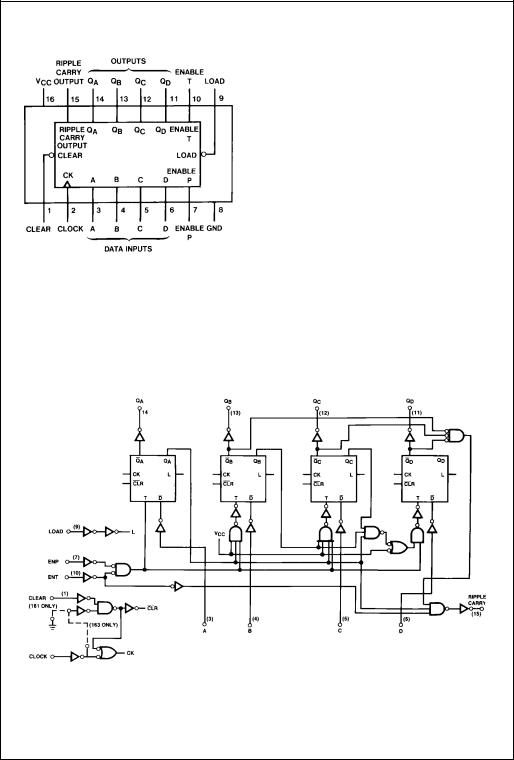

Connection Diagram |

Truth Tables |

|

|

|

|

|||

Pin Assignments for DIP, SOIC, SOP and TSSOP |

|

|

|

|

MM74HC161 |

|

||

|

|

|

|

|

|

|

|

|

|

CLK |

CLR |

ENP |

|

ENT |

Load |

|

Function |

|

|

|

|

|

|

|

|

|

|

X |

L |

X |

|

X |

X |

|

Clear |

|

X |

H |

H |

|

L |

H |

|

Count & RC disabled |

|

X |

H |

L |

|

H |

H |

|

Count disabled |

|

X |

H |

L |

|

L |

H |

|

Count & RC disabled |

|

− |

H |

X |

|

X |

L |

|

Load |

|

− |

H |

H |

|

H |

H |

|

Increment Counter |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MM74HC163 |

|

||

|

|

|

|

|

|

|

||

|

CLK |

CLR |

ENP |

|

ENT |

Load |

|

Function |

|

|

|

|

|

|

|

|

|

|

− |

L |

X |

|

X |

X |

|

Clear |

|

X |

H |

H |

|

L |

H |

|

Count & RC disabled |

|

X |

H |

L |

|

H |

H |

|

Count disabled |

|

X |

H |

L |

|

L |

H |

|

Count & RC disabled |

|

− |

H |

X |

|

X |

L |

|

Load |

|

− |

H |

H |

|

H |

H |

|

Increment Counter |

|

|

|

|

|

|

|

|

|

H = HIGH Level

L = LOW Level

X = Don’t Care

− = LOW-to-HIGH Transition

Logic Diagram

www.fairchildsemi.com |

2 |

Absolute Maximum Ratings(Note 1)

(Note 2) |

|

Supply Voltage (VCC) |

−0.5 to +7.0V |

DC Input Voltage (VIN) |

−1.5 to VCC+1.5V |

DC Output Voltage (VOUT) |

−0.5 to VCC+0.5V |

Clamp Diode Current (IIK, IOK) |

±20 mA |

DC Output Current, per pin (IOUT) |

±25 mA |

DC VCC or GND Current, per pin (ICC) |

±50 mA |

Storage Temperature Range (TSTG) |

−65°C to +150°C |

Power Dissipation (PD) |

|

(Note 3) |

600 mW |

S.O. Package only |

500 mW |

Lead Temperature |

|

(TL) (Soldering 10 seconds) |

260°C |

DC Electrical Characteristics (Note 4)

Recommended Operating

Conditions

|

Min |

Max |

Units |

Supply Voltage (VCC) |

2 |

6 |

V |

DC Input or Output Voltage |

0 |

VCC |

V |

(VIN, VOUT) |

−40 |

+85 |

°C |

Operating Temperature Range (TA) |

|||

Input Rise or Fall Times |

|

|

|

(tr, tf) VCC = 2.0V |

|

1000 |

ns |

VCC = 4.5V |

|

500 |

ns |

VCC = 6.0V |

|

400 |

ns |

Note 1: Absolute Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating — plastic “N” package: − 12 mW/°C from 65°C to 85°C.

Symbol |

Parameter |

Conditions |

VCC |

|

TA=25°C |

TA=−40 to 85°C |

TA=−55 to 125°C |

Units |

|

Typ |

Guaranteed Limits |

||||||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

VIH |

Minimum HIGH Level |

|

2.0V |

|

1.5 |

1.5 |

1.5 |

V |

|

|

Input Voltage |

|

4.5V |

|

3.15 |

3.15 |

3.15 |

V |

|

|

|

|

6.0V |

|

4.2 |

4.2 |

4.2 |

V |

|

|

|

|

|

|

|

|

|

|

|

VIL |

Maximum LOW Level |

|

2.0V |

|

0.5 |

0.5 |

0.5 |

V |

|

|

Input Voltage |

|

4.5V |

|

1.35 |

1.35 |

1.35 |

V |

|

|

|

|

6.0V |

|

1.8 |

1.8 |

1.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

VOH |

Minimum HIGH Level |

VIN = VIH or VIL |

|

|

|

|

|

|

|

|

Output Voltage |

|IOUT| ≤ 20 μA |

2.0V |

2.0 |

1.9 |

1.9 |

1.9 |

V |

|

|

|

|

4.5V |

4.5 |

4.4 |

4.4 |

4.4 |

V |

|

|

|

|

6.0V |

6.0 |

5.9 |

5.9 |

5.9 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

VIN = VIH or VIL |

|

|

|

|

|

|

|

|

|

|IOUT| ≤ 4.0 mA |

4.5V |

4.2 |

3.98 |

3.84 |

3.7 |

V |

|

|

|

|IOUT| ≤ 5.2 mA |

6.0V |

5.7 |

5.48 |

5.34 |

5.2 |

V |

|

VOL |

Maximum LOW Level |

VIN = VIH or VIL |

|

|

|

|

|

|

|

|

Output Voltage |

|IOUT| ≤ 20 μA |

2.0V |

0 |

0.1 |

0.1 |

0.1 |

V |

|

|

|

|

4.5V |

0 |

0.1 |

0.1 |

0.1 |

V |

|

|

|

|

6.0V |

0 |

0.1 |

0.1 |

0.1 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

VIN = VIH or VIL |

|

|

|

|

|

|

|

|

|

|IOUT| ≤ 4.0 mA |

4.5V |

0.2 |

0.26 |

0.33 |

0.4 |

V |

|

|

|

|IOUT| ≤ 5.2 mA |

6.0V |

0.2 |

0.26 |

0.33 |

0.4 |

V |

|

IIN |

Maximum Input |

VIN = VCC or GND |

6.0V |

|

±0.1 |

±1.0 |

±1.0 |

μA |

|

|

Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC |

Maximum Quiescent |

VIN = VCC or GND |

6.0V |

|

8.0 |

80 |

160 |

μA |

|

|

Supply Current |

IOUT = 0 μA |

|

|

|

|

|

|

|

Note 4: For a power supply of 5V ±10% the worst case output voltages (VOH, and VOL) occur for HC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case VIH and VIL occur at VCC=5.5V and 4.5V respectively. (The VIH value at 5.5V is 3.85V.) The worst case leakage current (IIN, ICC, and IOZ) occur for CMOS at the higher voltage and so the 6.0V values should be used.

MM74HC163 • MM74HC161

3 |

www.fairchildsemi.com |

Loading...

Loading...