Texas Instruments CY74FCT841CTSOCT, CY74FCT841CTSOC, CY74FCT841CTQCT, CY74FCT841CTQC, CY74FCT841BTPC Datasheet

...

Data sheet acquired from Cypress Semiconductor Corporation.

Data sheet modified to remove devices not offered.

CY54/74FCT841T

SCCS035 - September 1994 - Revised March 2000

10-Bit Latch

Features |

• High-speed parallel latches |

•Function, pinout, and drive compatible with FCT, F, and AM29841 logic

•FCT-C speed at 5.5 ns max. (Com’l)

FCT-B speed at 6.5 ns max. (Com’l)

• Reduced V (typically = 3.3V) versions of equivalent

OH

FCT functions

•Edge-rate control circuitry for significantly improved noise characteristics

•Power-off disable feature

•Matched rise and fall times

•ESD > 2000V

•Fully compatible with TTL input and output logic levels

• Sink current |

64 mA (Com’l), |

|

32 mA (Mil) |

Source current |

32 mA (Com’l), |

|

12 mA (Mil) |

• Buffered common latch enable input

Functional Description

The FCT841T bus interface latch is designed to eliminate the extra packages required to buffer existing latches and provide extra data width for wider address/data paths or buses carrying parity. The FCT841T is a buffered 10-bit wide version of the FCT373 function.

The FCT841T high-performance interface is designed for high-capacitance load drive capability while providing low-capacitance bus loading at both inputs and outputs. Outputs are designed for low-capacitance bus loading in the high impedance state and are designed with a power-off disable feature to allow for live insertion of boards.

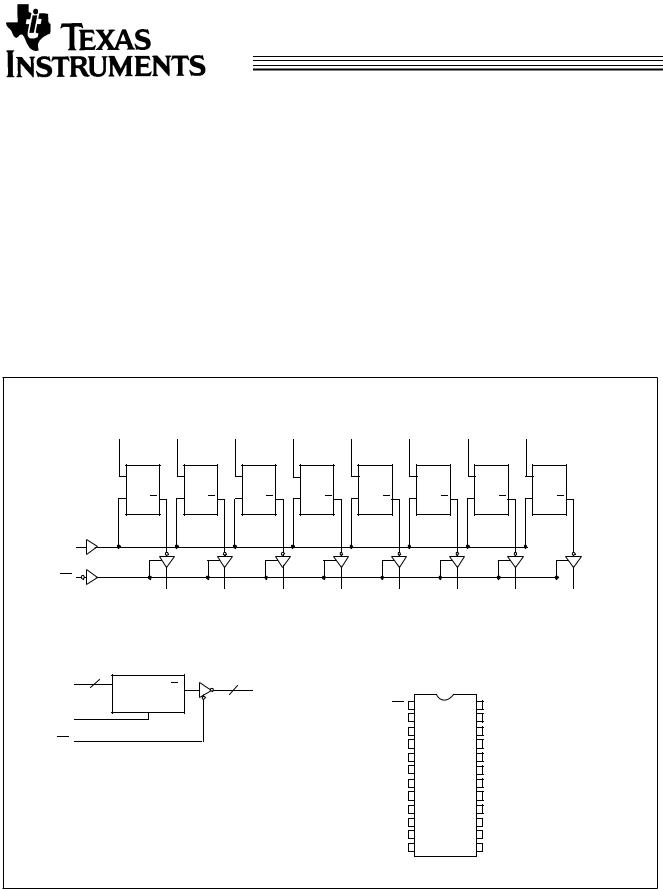

Functional Block Diagram |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

D0 |

|

D1 |

|

D2 |

|

D3 |

|

D4 |

D5 |

|

DN- 1 |

|

DN |

|

|

|

|

D |

|

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

D Q |

|||||||

|

|

LE |

Q |

LE |

Q |

LE |

Q |

LE |

Q |

LE |

Q |

LE |

Q |

LE |

Q |

LE |

Q |

LE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y0 |

|

Y1 |

|

Y2 |

|

Y3 |

Y4 |

|

Y5 |

|

YN- 1 |

|

YN |

Logic Block Diagram |

|

|

|

|

|

|

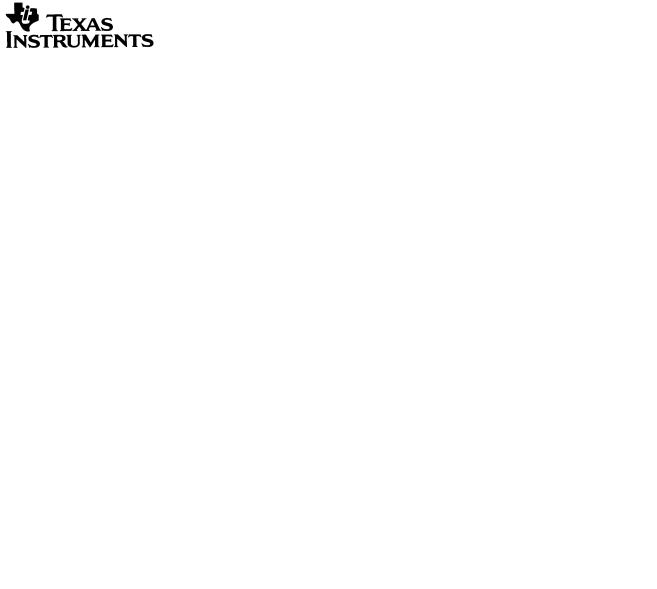

Pin Configurations |

|

|

||||||||

|

10 |

|

|

|

|

|

|

|

|

|

DIP/QSOP/SOIC |

|

|

||||

D |

D |

|

Q |

|

10 |

|

|

|

|

|

Top View |

|

|

|

|

||

|

|

|

Y |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LE |

|

|

|

|

|

|

|

OE |

1 |

24 |

|

VCC |

|

|

LE |

|

|

|

|

|

|

|

|

|

|

D0 |

2 |

23 |

|

Y0 |

|

|

OE |

|

|

|

|

|

|

|

|

|

|

D1 |

3 |

22 |

|

Y1 |

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

4 |

21 |

|

Y2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

D3 |

5 |

20 |

|

Y3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

D4 |

6 |

19 |

|

Y4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

D5 |

7 |

18 |

|

Y5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

D6 |

8 |

17 |

|

Y6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

D7 |

9 |

16 |

|

Y7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

D8 |

10 |

15 |

|

Y8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

D9 |

11 |

14 |

|

Y9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

12 |

13 |

|

LE |

|

|

Copyright © 2000, Texas Instruments Incorporated

|

|

|

|

|

|

|

CY54/74FCT841T |

||

|

|

|

|

|

|

|

|

|

|

Pin Description |

|||||||||

|

|

|

|

|

|

|

|||

|

Name |

I/O |

|

|

|

Description |

|||

|

|

|

|

||||||

|

D |

I |

The latch data inputs. |

||||||

|

|

|

|

||||||

|

LE |

I |

The latch enable input. The latches are transparent when LE is HIGH. Input data is latched on the |

||||||

|

|

|

|

HIGH-to-LOW transition. |

|||||

|

|

|

|

||||||

|

Y |

O |

The three-state latch outputs. |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

The output enable control. When the |

|

is LOW, the outputs are enabled. When |

|

is HIGH, the outputs |

|

|

OE |

OE |

OE |

||||||

|

|

|

|

Y1 are in the high impedance (off) state. |

|||||

Function Table[1]

|

|

|

Inputs |

|

Internal Outputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

LE |

D |

O |

Y |

Function |

OE |

|||||||

|

|

|

|

|

|

|

|

|

H |

X |

X |

X |

Z |

High Z |

|

|

H |

H |

L |

L |

Z |

|

|

|

H |

H |

H |

H |

Z |

|

|

|

|

|

|

|

|

|

|

|

H |

L |

X |

NC |

Z |

Latched (High Z) |

|

|

|

|

|

|

|

|

|

|

L |

H |

L |

L |

L |

Transparent |

|

|

L |

H |

H |

H |

H |

|

|

|

|

|

|

|

|

|

|

|

L |

L |

X |

NC |

NC |

Latched |

|

|

|

|

|

|

|

|

|

Maximum Ratings[2, 3]

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature ................................. |

–65°C to +150°C |

Ambient Temperature with |

–65°C to +135°C |

Power Applied ............................................. |

|

Supply Voltage to Ground Potential ............... |

–0.5V to +7.0V |

DC Input Voltage............................................ |

–0.5V to +7.0V |

DC Output Voltage ......................................... |

–0.5V to +7.0V |

Notes: |

|

DC Output Current (Maximum Sink Current/Pin) ...... |

120 mA |

Power Dissipation .......................................................... |

0.5W |

Static Discharge Voltage............................................ |

>2001V |

(per MIL-STD-883, Method 3015)

Operating Range

|

|

Ambient |

|

Range |

Range |

Temperature |

VCC |

Commercial |

All |

–40°C to +85°C |

5V ± 5% |

|

|

|

|

Military[4] |

All |

–55°C to +125°C |

5V ± 10% |

1.H = HIGH Voltage Level, L = LOW Voltage Level, X = Don’t Care, NC = No Change, Z = High Impedance.

2.Unless otherwise noted, these limits are over the operating free-air temperature range.

3.Unused inputs must always be connected to an appropriate logic voltage level, preferably either VCC or ground.

4.TA is the “instant on” case temperature.

2

CY54/74FCT841T

Electrical Characteristics Over the Operating Range

Parameter |

Description |

|

Test Conditions |

|

Min. |

Typ.[5] |

Max. |

Unit |

||

VOH |

Output HIGH Voltage |

VCC= Min., IOH = −32 mA |

Com’l |

2.0 |

|

|

V |

|||

|

|

|

VCC= Min., IOH = −15 mA |

Com’l |

2.4 |

3.3 |

|

V |

||

|

|

|

VCC= Min., IOH = −12 mA |

Mil |

2.4 |

3.3 |

|

V |

||

VOL |

Output LOW Voltage |

VCC= Min., IOL = 64 mA |

Com’l |

|

0.3 |

0.55 |

V |

|||

|

|

|

VCC= Min., IOL = 32 mA |

Mil |

|

0.3 |

0.55 |

V |

||

VIH |

Input HIGH Voltage |

|

|

|

|

2.0 |

|

|

V |

|

VIL |

Input LOW Voltage |

|

|

|

|

|

|

0.8 |

V |

|

VH |

Hysteresis[6] |

All inputs |

|

|

|

0.2 |

|

V |

||

VIK |

Input Clamp Diode Voltage |

VCC= Min., IIN= −18 mA |

|

|

−0.7 |

−1.2 |

V |

|||

II |

Input HIGH Current |

VCC= Max., VIN= VCC |

|

|

|

5 |

µA |

|||

IIH |

Input HIGH Current |

VCC= Max., VIN= 2.7V |

|

|

|

±1 |

µA |

|||

IIL |

Input LOW Current |

VCC= Max., VIN= 0.5V |

|

|

|

±1 |

µA |

|||

IOZH |

Off State HIGH-Level Output |

VCC = Max., VOUT = 2.7V |

|

|

|

10 |

µA |

|||

|

|

Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

IOZL |

Off State LOW-Level |

VCC = Max., VOUT = 0.5V |

|

|

|

−10 |

µA |

|||

|

|

Output Current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

OS |

Output Short Circuit Current[7] |

V |

= Max., V |

= 0.0V |

|

−60 |

−120 |

−225 |

mA |

|

|

CC |

OUT |

|

|

|

|

|

|

|

IOFF |

Power-Off Disable |

VCC = 0V, VOUT = 4.5V |

|

|

|

±1 |

µA |

|||

Capacitance[6]

Parameter |

Description |

Typ.[5] |

Max. |

Unit |

CIN |

Input Capacitance |

5 |

10 |

pF |

COUT |

Output Capacitance |

9 |

12 |

pF |

Notes: |

|

|

|

|

5.Typical values are at VCC=5.0V, TA=+25˚C ambient.

6.This parameter is specified but not tested.

7.Not more than one output should be shorted at a time. Duration of short should not exceed one second. The use of high-speed test apparatus and/or sample and hold techniques are preferable in order to minimize internal chip heating and more accurately reflect operational values. Otherwise prolonged shorting of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parametric tests. In any sequence of parameter tests, IOS tests should be performed last.

3

Loading...

Loading...