Texas Instruments CD4541BPWR, CD4541BM96, CD4541BM, CD4541BF3A, CD4541BF Datasheet

...

[ /Title (CD45 41B)

/Subject (CMO S Programmable Timer High Voltage Types (20V Rating)) /Autho r () /Keywords (Harris Semicon- ductor, CD400 0, metal gate, CMOS , pdip, cerdip, mil, military, mil

|

CD4541B |

|

Data sheet acquired from Harris Semiconductor |

CMOS Programmable Timer |

|

High Voltage Types (20V Rating) |

||

SCHS085 |

Features

•Low Symmetrical Output Resistance, Typically 100Ω at VDD = 15V

•Built-In Low-Power RC Oscillator

•Oscillator Frequency Range . . . . . . . . . . DC to 100kHz

•External Clock (Applied to Pin 3) can be Used Instead of Oscillator

•Operates as 2N Frequency Divider or as a SingleTransition Timer

•Q/Q Select Provides Output Logic Level Flexibility

•AUTO or MASTER RESET Disables Oscillator During Reset to Reduce Power Dissipation

•Operates With Very Slow Clock Rise and Fall Times

•Capable of Driving Six Low Power TTL Loads, Three Low-Power Schottky Loads, or Six HTL Loads Over the Rated Temperature Range

•Symmetrical Output Characteristics

•100% Tested for Quiescent Current at 20V

•5V, 10V, and 15V Parametric Ratings

•Meets All Requirements of JEDEC Standard No. 13B, “Standard Specifications for Description of ‘B’ Series CMOS Devices”

Ordering Information

|

TEMP. |

|

PKG. |

PART NUMBER |

RANGE (oC) |

PACKAGE |

NO. |

CD4541BF |

-55 to 125 |

14 Ld CERDIP |

F14.3 |

|

|

|

|

CD4541BE |

-55 to 125 |

14 Ld PDIP |

E14.3 |

|

|

|

|

CD4541BH |

-55 to 125 |

Chip |

- |

|

|

|

|

CD4541BM |

-55 to 125 |

14 Ld SOIC |

M14.15 |

|

|

|

|

Description

CD4541B programmable timer consists of a 16-stage binary counter, an oscillator that is controlled by external R-C components (2 resistors and a capacitor), an automatic power-on reset circuit, and output control logic. The counter increments on positive-edge clock transitions and can also be reset via the MASTER RESET input.

The output from this timer is the Q or Q output from the 8th, 10th, 13th, or 16th counter stage. The desired stage is chosen using time-select inputs A and B (see Frequency Select Table). The output is available in either of two modes selectable via the MODE input, pin 10 (see Truth Table). When this MODE input is a logic “1”, the output will be a continuous square wave having a frequency equal to the oscillator frequency divided by 2N. With the MODE input set to logic “0” and after a MASTER RESET is initiated, the output (assuming Q output has been selected) changes from a low to a high state after 2N-1 counts and remains in that state until another MASTER RESET pulse is applied or the MODE input is set to a logic “1”.

Timing is initialized by setting the AUTO RESET input (pin 5) to logic “0” and turning power on. If pin 5 is set to logic “1”, the AUTO RESET circuit is disabled and counting will not start until after a positive MASTER RESET pulse is applied and returns to a low level. The AUTO RESET consumes an appreciable amount of power and should not be used if low-power operation is desired. For reliable automatic power-on reset, VDD should be greater than 5V.

The RC oscillator, shown in Figure 2, oscillates with a frequency determined by the RC network and is calculated using:

f = |

1 |

Where f is between 1kHz |

2.3-----------R-----TC--------C----TC------ |

and 100kHz |

|

|

|

and RS ≥ 10kΩ and ≈ 2RTC |

Pinout

CD4541B (CERDIP, PDIP, SOIC)

TOP VIEW

RTC |

1 |

|

14 |

VDD |

||

CTC |

|

|

|

B |

||

2 |

|

13 |

||||

RS |

|

|

|

A |

||

3 |

|

12 |

||||

NC |

|

|

|

NC |

||

4 |

|

11 |

||||

AUTO RESET |

|

|

|

MODE |

||

5 |

|

10 |

||||

MASTER RESET |

|

|

|

|

|

|

6 |

|

9 |

Q/Q |

SELECT |

||

VSS |

|

|

|

OUTPUT |

||

7 |

|

8 |

||||

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 1378.1 |

|

|

||

Copyright © Harris Corporation 1998 |

1 |

|

|

|

|

CD4541B

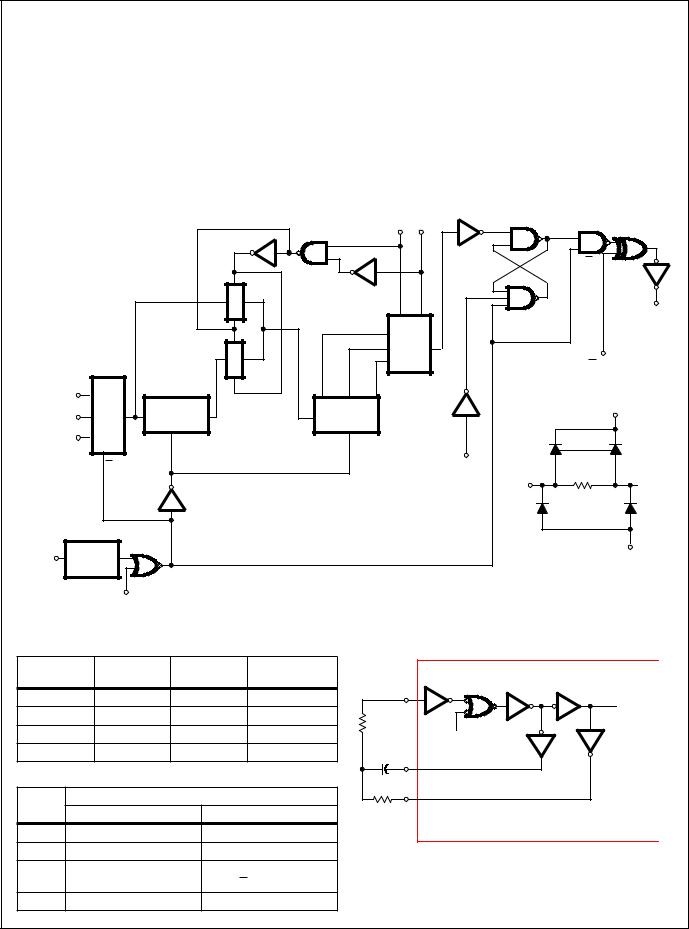

Functional Diagram

|

A |

12 |

|

|

|

||

13 |

|

|

|

||||

|

B |

|

|

|

|||

1 |

|

|

|

||||

RTC |

|

|

|

||||

2 |

|

|

|

||||

CTC |

|

|

|

||||

3 |

|

8 |

|

||||

RS |

|

Q |

|||||

5 |

|

|

|||||

AR |

|

|

|

||||

6 |

|

|

|

||||

MR |

|

|

|

||||

10 |

|

VDD = PIN 14 |

|||||

MODE |

9 |

|

VSS = PIN 7 |

||||

|

|

|

|

||||

Q/Q |

|||||||

|

|

|

|

||||

SELECT |

|

|

|

|

|||

|

|

|

|

||||

Functional Block Diagram

12 13

AUTO RESET†

|

|

|

|

|

† A |

† B |

|

|

|

|

|

|

|

|

R |

|

|

N |

|

|

|

|

|

|

|

P |

|

|

|

|

8 |

|

|

|

|

|

|

Q |

|

|

|

|

|

|

1 OF 3 |

|

|

|

|

N |

|

|

MUX |

9 |

|

|

|

P |

|

|

216 |

|

† Q/Q SELECT |

|

|

|

|

OR |

|

|

|

|

3 |

|

|

|

|

|

|

† RS |

|

210 |

213 |

28 |

|

|

|

2 |

8-STAGE |

|

8-STAGE |

|

VDD |

||

† CTC |

|

|

|||||

OSC |

COUNTER |

|

COUNTER |

|

|

||

† RTC |

1 |

|

|

|

|

|

|

|

R |

|

|

R |

|

|

|

|

|

|

|

|

|

|

10 |

|

R |

|

|

|

|

|

† MODE |

5 |

PWR ON |

|

VSS |

|

|

||

|

RESET |

|

|

|

|

|

|

|

|

VDD = 14 |

† All inputs are protected by CMOS Protection Network. |

|

6 |

VSS = 7 NC = 4, 11 |

|

|

|

MANUAL RESET†

FIGURE 1.

|

FREQUENCY SELECTION TABLE |

|

|

|

|

||

|

|

|

NO. OF |

COUNT 2N |

|

|

|

A |

B |

STAGES N |

|

|

|||

0 |

0 |

|

13 |

|

8192 |

|

3 |

|

|

|

TO CLOCK |

||||

0 |

1 |

|

10 |

|

1024 |

|

CKT |

|

|

RS |

|

||||

1 |

0 |

|

8 |

|

256 |

|

|

|

|

|

INTERNAL |

||||

1 |

1 |

|

16 |

|

65536 |

CTC |

RESET |

|

|

2 |

|||||

|

|

|

|

|

|

||

|

TRUTH TABLE |

|

|

|

|

||

|

|

STATE |

|

|

|

1 |

|

|

|

|

|

|

|

||

PIN |

0 |

|

|

1 |

|

RTC |

|

5 |

Auto Reset On |

|

Auto Reset Disable |

|

|

||

6 |

Master Reset Off |

|

Master Reset On |

|

FIGURE 2. RC OSCILLATOR CIRCUIT |

||

9 |

Output Initially Low After |

Output Initially High After |

|

||||

|

|

||||||

|

Reset (Q) |

|

Reset (Q) |

|

|

|

|

10 |

Single Transition Mode |

|

Recycle Mode |

|

|

|

|

2

CD4541B

Absolute Maximum Ratings

DC Supply - Voltage Range, VDD

Voltages Referenced to VSS Terminal . . . . . . . . . . -0.5V to +20V Input Voltage Range, All Inputs . . . . . . . . . . . . . -0.5V to VDD +0.5V DC Input Current, Any One Input . . . . . . . . . . . . . . . . . . . . . ±10mA Device Dissipation Per Output Transistor

For TA = Full Package Temperature Range

(All Package Types) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100mW

Operating Conditions

Temperature Range TA . . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range

For TA = Full Package Temperature Range . . . . .3V (Min), 18V (Typ)

Thermal Information

Thermal Resistance (Typical, Note 1) |

θJA (oC/W) θJC (oC/W) |

|

PDIP Package . . . . . . . . . . . . . . . . . . . |

90 |

N/A |

CERDIP Package . . . . . . . . . . . . . . . . |

90 |

36 |

SOIC Package . . . . . . . . . . . . . . . . . . . |

120 |

N/A |

Maximum Junction Temperature (Plastic Package) . |

. . . . . . . 150oC |

|

Maximum Storage Temperature Range (TSTG) . . . |

-65oC to 150oC |

|

Maximum Lead Temperature (Soldering 10s) |

|

|

At Distance 1/16in ± 1/32in (1.59mm ±0.79mm) |

265oC |

|

from case for 10s Maximum . . . . . . . . . |

. . . . . . . . |

|

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. θJA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications

|

CONDITIONS |

|

|

LIMITS AT INDICATED TEMPERATURES (oC) |

|

|

||||||

|

VO |

VIN |

|

VDD |

|

|

|

|

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

PARAMETER |

(V) |

(V) |

|

(V) |

-55 |

-40 |

85 |

125 |

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

|

|

|

|

|

|

|

Quiescent Device |

- |

0, 5 |

|

5 |

5 |

5 |

150 |

150 |

- |

0.04 |

5 |

µA |

Current, |

|

|

|

|

|

|

|

|

|

|

|

|

- |

0, 10 |

|

10 |

10 |

10 |

300 |

300 |

- |

0.04 |

10 |

µA |

|

(Note 2) IDD (Max) |

|

|||||||||||

|

- |

0, 15 |

|

15 |

20 |

20 |

600 |

600 |

- |

0.04 |

20 |

µA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

0, 20 |

|

20 |

100 |

100 |

3000 |

3000 |

- |

0.08 |

100 |

µA |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Low (Sink) |

0.4 |

0, 5 |

|

5 |

1.9 |

1.85 |

1.26 |

1.08 |

1.55 |

3.1 |

- |

µA |

Current lOL (Min) |

|

|

|

|

|

|

|

|

|

|

|

|

0.5 |

0, 10 |

|

10 |

5 |

4.8 |

3.3 |

2.8 |

4 |

8 |

- |

µA |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.5 |

0, 15 |

|

15 |

12.6 |

12 |

8.4 |

7.2 |

10 |

20 |

- |

µA |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output High (Source) |

4.6 |

0, 5 |

|

5 |

-1.9 |

-1.85 |

-1.26 |

-1.08 |

-1.55 |

-3.1 |

- |

mA |

Current, IOH (Min) |

|

|

|

|

|

|

|

|

|

|

|

|

2.5 |

0, 5 |

|

5 |

-6.2 |

-6 |

-4.1 |

-3 |

-5 |

-10 |

- |

mA |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9.5 |

0, 10 |

|

10 |

-5 |

-4.8 |

-3.3 |

-2.8 |

-4 |

-8 |

- |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13.5 |

0, 15 |

|

15 |

-12.6 |

-12 |

-8.4 |

-7.2 |

-10 |

-20 |

- |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage: |

- |

0, 5 |

|

5 |

- |

|

0.05 |

|

- |

0 |

0.05 |

mA |

Low-Level, VOL (Max) |

|

|

|

|

|

|

|

|

|

|

|

|

- |

0, 10 |

|

10 |

- |

|

0.05 |

|

- |

0 |

0.05 |

mA |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

0, 15 |

|

15 |

- |

|

0.05 |

|

- |

0 |

0.05 |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage: |

- |

0, 5 |

|

5 |

- |

|

4.95 |

|

4.95 |

5 |

- |

mA |

High-Level, VOH (Min) |

|

|

|

|

|

|

|

|

|

|

|

|

- |

0, 10 |

|

10 |

- |

|

9.95 |

|

9.95 |

10 |

- |

mA |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

0, 15 |

|

15 |

- |

|

14.95 |

|

14.95 |

15 |

- |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Low Voltage, |

0.5, 4.5 |

- |

|

5 |

- |

|

1.5 |

|

- |

- |

1.5 |

V |

VIL (Max) |

|

|

|

|

|

|

|

|

|

|

|

|

1, 9 |

- |

|

10 |

- |

|

3 |

|

- |

- |

3 |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.5, 13.5 |

- |

|

15 |

- |

|

4 |

|

- |

- |

4 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

3

Loading...

Loading...