Analog Devices AD677KR, AD677KN, AD677KD, AD677JR, AD677JN Datasheet

...

a |

16-Bit 100 kSPS |

|

Sampling ADC |

||

|

|

|

|

|

AD677 |

|

|

|

FEATURES Autocalibrating

On-Chip Sample-Hold Function Serial Output

16 Bits No Missing Codes

61 LSB INL

–99 dB THD 92 dB S/(N+D)

1 MHz Full Power Bandwidth

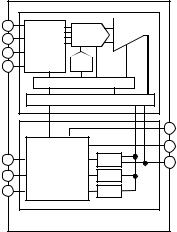

FUNCTIONAL BLOCK DIAGRAM

VIN |

10 |

|

|

A CHIP |

|

|

16-BIT |

COMP |

|||

AGND SENSE |

9 |

INPUT |

DAC |

||

|

|||||

|

|

|

|

||

VR E F |

11 |

BUFFERS |

|

||

|

|

|

CAL |

|

|

AGND |

8 |

|

DAC |

|

|

|

|

|

LOGIC TIMING |

|

|

|

|

LEVEL TRANSLATORS |

|||

CAL |

16 |

MICROCODED |

SAR |

|

|

|

|

CLK |

2 |

CONTROLLER |

ALU |

SAMPLE |

1 |

|

RAM |

D CHIP

AD677

15 BUSY

14 SCLK

3 SDATA

PRODUCT DESCRIPTION

The AD677 is a multipurpose 16-bit serial output analog-to- digital converter which utilizes a switched-capacitor/charge redistribution architecture to achieve a 100 kSPS conversion rate (10 μs total conversion time). Overall performance is optimized by digitally correcting internal nonlinearities through on-chip autocalibration.

The AD677 circuitry is segmented onto two monolithic chips— a digital control chip fabricated on Analog Devices DSP CMOS process and an analog ADC chip fabricated on our BiMOS II process. Both chips are contained in a single package.

The AD677 is specified for ac (or “dynamic”) parameters such as S/(N+D) Ratio, THD and IMD which are important in signal processing applications. In addition, dc parameters are specified which are important in measurement applications.

The AD677 operates from +5 V and ±12 V supplies and typically consumes 450 mW using a 10 V reference (360 mW with 5 V reference) during conversion. The digital supply (VDD) is separated from the analog supplies (VCC, VEE) for reduced digital crosstalk. An analog ground sense is provided to remotely sense the ground potential of the signal source. This can be useful if the signal has to be carried some distance to the A/D converter. Separate analog and digital grounds are also provided.

The AD677 is available in a 16-pin narrow plastic DIP, 16-pin narrow side-brazed ceramic package, or 28-lead SOIC. A parallel output version, the AD676, is available in a 28-pin ceramic or plastic DIP. All models operate over a commercial temperature range of 0°C to +70°C or an industrial range of –40°C to +85°C.

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

PRODUCT HIGHLIGHTS

1.Autocalibration provides excellent dc performance while eliminating the need for user adjustments or additional external circuitry.

2.±5 V to ±10 V input range (±VREF).

3.Available in 16-pin 0.3" skinny DIP or 28-lead SOIC.

4.Easy serial interface to standard ADI DSPs.

5.TTL compatible inputs/outputs.

6.Excellent ac performance: –99 dB THD, 92 dB S/(N+D) peak spurious –101 dB.

7.Industry leading dc performance: 1.0 LSB INL, ±1 LSB full scale and offset.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD677–SPECIFICATIONS

AC SPECIFICATIONS (TMIN to TMAX, VCC = +12 V 6 5%, VEE = –12 V 6 5%, VDD = +5 V 6 10%)1

|

|

AD677J/A |

|

|

AD677K/B |

|

|

Parameter |

Min |

Typ |

Max |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

Total Harmonic Distortion (THD)2 |

|

|

|

|

|

|

|

@ 83 kSPS, TMIN to TMAX |

|

–97 |

–92 |

|

–99 |

–95 |

dB |

@ 100 kSPS, +25°C |

|

–97 |

–92 |

|

–99 |

–95 |

dB |

@ 100 kSPS, TMIN to TMAX |

|

–93 |

|

|

–95 |

|

dB |

Signal-to-Noise and Distortion Ratio (S/(N+D))2, 3 |

|

|

|

|

|

|

|

@ 83 kSPS, TMIN to TMAX |

89 |

91 |

|

90 |

92 |

|

dB |

@ 100 kSPS, +25°C |

89 |

91 |

|

90 |

92 |

|

dB |

@ 100 kSPS, TMIN to TMAX |

|

89 |

|

|

90 |

|

dB |

Peak Spurious or Peak Harmonic Component |

|

–101 |

|

|

–101 |

|

dB |

Intermodulation Distortion (IMD)4 |

|

|

|

|

|

|

|

2nd Order Products |

|

–102 |

|

|

–102 |

|

dB |

3rd Order Products |

|

–98 |

|

|

–98 |

|

dB |

Full Power Bandwidth |

|

1 |

|

|

1 |

|

MHz |

Noise |

|

160 |

|

|

160 |

|

μV rms |

DIGITAL SPECIFICATIONS (for all grades TMIN to TMAX, VCC = +12 V 6 5%, VEE = –12 V 6 5%, VDD = +5 V 6 10%)

Parameter |

|

Test Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

LOGIC INPUTS |

|

|

|

|

|

|

VIH |

High Level Input Voltage |

|

2.0 |

|

VDD + 0.3 |

V |

VIL |

Low Level Input Voltage |

|

–0.3 |

|

0.8 |

V |

IIH |

High Level Input Current |

VIH = VDD |

–10 |

|

+10 |

μA |

IIL |

Low Level Input Current |

VIL = 0 V |

–10 |

|

+10 |

μA |

CIN |

Input Capacitance |

|

|

10 |

|

pF |

LOGIC OUTPUTS |

|

|

|

|

|

|

VOH |

High Level Output Voltage |

IOH = 0.1 mA |

VDD – 1 V |

|

|

V |

|

|

IOH = 0.5 mA |

2.4 |

|

|

V |

VOL |

Low Level Output Voltage |

IOL = 1.6 mA |

|

|

0.4 |

V |

NOTES

1VREF = 10.0 V, Conversion Rate = 100 kSPS, flN = 1.0 kHz, VIN = –0.05 dB, Bandwidth = 50 kHz unless otherwise indicated. All measurements referred to a 0 dB (20 V p-p) input signal. Values are post-calibration.

2For other input amplitudes, refer to Figure 12.

3For dynamic performance with different reference values see Figure 11.

4fa = 1008 Hz, fb = 1055 Hz. See Definition of Specifications section and Figure 16.

Specifications subject to change without notice.

–2– |

REV. A |

DC SPECIFICATIONS (TMIN to TMAX, VCC = +12 V 6 5%, VEE = –12 V 6 5%, VDD = +5 V 6 1O%)1 |

|

AD677 |

|||||

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

AD677J/A |

|

|

AD677K/B |

|

|

Parameter |

Min |

Typ |

Max |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

TEMPERATURE RANGE |

|

|

|

|

|

|

°C |

J, K Grades |

0 |

|

+70 |

0 |

|

+70 |

|

A, B Grades |

–40 |

|

+85 |

–40 |

|

+85 |

°C |

ACCURACY |

|

|

|

|

|

|

|

Resolution |

16 |

|

|

16 |

|

|

Bits |

Integral Nonlinearity (INL) |

|

±1 |

|

|

±1 |

±1.5 |

|

@ 83 kSPS, TMIN to TMAX |

|

|

|

LSB |

|||

@ 100 kSPS, +25°C |

|

±1 |

|

|

+1 |

±1.5 |

LSB |

@ 100 kSPS, TMIN to TMAX |

|

±2 |

|

|

±2 |

|

LSB |

Differential Nonlinearity (DNL)–No Missing Codes |

|

16 |

±4 |

16 |

±1 |

±3 |

Bits |

Bipolar Zero Error2 |

|

±2 |

|

LSB |

|||

Positive, Negative FS Errors2 |

|

±2 |

±4 |

|

±1 |

±3 |

|

@ 83 kSPS |

|

|

LSB |

||||

@ 100 kSPS, +25°C |

|

±2 |

±4 |

|

±1 |

±3 |

LSB |

@ 100 kSPS |

|

±4 |

|

|

±4 |

|

LSB |

TEMPERATURE DRIFT3 |

|

±0.5 |

|

|

±0.5 |

|

|

Bipolar Zero |

|

|

|

|

LSB |

||

Postive Full Scale |

|

±0.5 |

|

|

±0.5 |

|

LSB |

Negative Full Scale |

|

±0.5 |

|

|

±0.5 |

|

LSB |

VOLTAGE REFERENCE INPUT RANGE4 (VREF) |

5 |

|

10 |

5 |

|

10 |

V |

ANALOG INPUT5 |

|

|

±VREF |

|

|

±VREF |

|

Input Range (VIN) |

|

|

|

|

V |

||

Input Impedance |

|

* |

|

|

* |

|

μs |

Input Settling Time |

|

2 |

|

|

2 |

|

|

Input Capacitance During Sample |

|

|

50* |

|

|

50* |

pF |

Aperture Delay |

|

6 |

|

|

6 |

|

ns |

Aperture Jitter |

|

100 |

|

|

100 |

|

ps |

|

|

|

|

|

|

|

|

POWER SUPPLIES |

|

|

|

|

|

|

|

Power Supply Rejection6 |

|

|

|

|

|

|

|

VCC = +12 V ± 5% |

|

±0.5 |

|

|

±0.5 |

|

LSB |

VEE = –12 V ± 5% |

|

±0.5 |

|

|

±0.5 |

|

LSB |

VDD = +5 V ± 10% |

|

±0.5 |

|

|

±0.5 |

|

LSB |

Operating Current |

|

|

|

|

|

|

|

VREF = +5 V |

|

|

|

|

|

|

|

ICC |

|

14.5 |

18 |

|

14.5 |

18 |

mA |

IEE |

|

14.5 |

18 |

|

14.5 |

18 |

–mA |

IDD |

|

3 |

5 |

|

3 |

5 |

mA |

Power Consumption |

|

360 |

480 |

|

360 |

480 |

mW |

VREF = +10 V |

|

|

|

|

|

|

|

ICC |

|

18 |

24 |

|

18 |

24 |

mA |

IEE |

|

18 |

24 |

|

18 |

24 |

–mA |

IDD |

|

3 |

5 |

|

3 |

5 |

mA |

Power Consumption |

|

450 |

630 |

|

450 |

630 |

mW |

|

|

|

|

|

|

|

|

NOTES

1VREF = 10.0 V, Conversion Rate = 100 kSPS unless otherwise noted. Values are post-calibration.

2Values shown apply to any temperature from TMIN to TMAX after calibration at that temperature at nominal supplies.

3Values shown are based upon calibration at +25°C with no additional calibration at temperature. Values shown are the typical variation from the value at +25 °C. 4See “APPLICATIONS” section for recommended voltage reference circuit, and Figure 11 for dynamic performance with other reference voltage values.

5See “APPLICATIONS” section for recommended input buffer circuit.

6Typical deviation of bipolar zero, –full scale or +full scale from min to max rating. *For explanation of input characteristics, see “ANALOG INPUT” section.

Specifications subject to change without notice.

REV. A |

–3– |

AD677

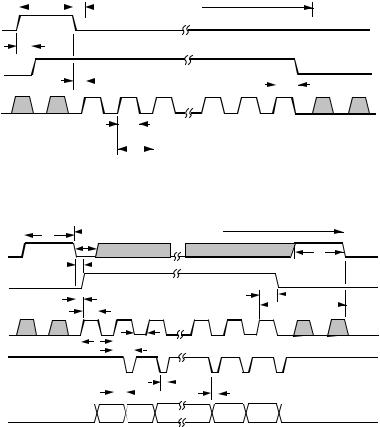

TIMING SPECIFICATIONS (TMIN to TMAX, VCC = +12 V 6 5%, VEE = –12 V 6 5%, VDD = +5 V 6 10%)1

Parameter |

Symbol |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

Conversion Period2, 3 |

tC |

10 |

|

1000 |

μs |

CLK Period4 |

tCLK |

480 |

|

|

ns |

Calibration Time |

tCT |

|

|

85532 |

tCLK |

Sampling Time |

tS |

2 |

|

|

μs |

Last CLK to SAMPLE Delay5 |

tLCS |

2.1 |

|

|

μs |

SAMPLE Low |

tSL |

100 |

|

|

ns |

SAMPLE to Busy Delay |

tSS |

|

30 |

75 |

ns |

1st CLK Delay |

tFCD |

50 |

|

|

ns |

CLK Low6 |

tCL |

50 |

|

|

ns |

CLK High6 |

tCH |

50 |

|

|

ns |

CLK to BUSY Delay |

tCB |

|

180 |

300 |

ns |

CLK to SDATA Valid |

tCD |

50 |

100 |

175 |

ns |

CLK to SCLK High |

tCSH |

100 |

180 |

300 |

ns |

SCLK Low |

tSCL |

50 |

80 |

|

ns |

SDATA to SCLK High |

tDSH |

50 |

80 |

|

ns |

CAL High Time |

tCALH |

50 |

|

|

ns |

CAL to BUSY Delay |

tCALB |

|

15 |

50 |

ns |

NOTES

1See the “CONVERSION CONTROL” and “AUTOCALIBRATION” sections for detailed explanations of the above timing.

2Depends upon external clock frequency; includes acquisition time and conversion time. The maximum conversion period is specified to account for the droop of the

internal sample/hold function. Operation at slower rates may degrade performance.

3tC = tFCD + 16 × tCLK + tLCS.

4580 ns is recommended for optimal accuracy over temperature (not necessary during calibration cycle).

5If SAMPLE goes high before the 17th CLK pulse, the device will start sampling approximately 100 ns after the rising edge of the 17th CLK pulse. 6tCH + tCL = tCLK and must be greater than 480 ns.

CAL |

|

|

|

|

tCALH |

|

|

|

|

|

|

tCT |

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(INPUT) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BUSY |

|

|

|

|

|

tCALB |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(OUTPUT) |

|

|

|

|

|

tFCD |

|

|

|

|

|

|

|

|

|

|

|

CLK* |

|

|

|

|

|

|

|

|

|

|

2 |

3 |

|

tCB |

|||

|

|

|

|

|

|

|

|||||||||||

1 |

|

||||||||||||||||

|

|

||||||||||||||||

(INPUT) |

|

|

|||||||||||||||

tCH 85530 85531 85532

tCL

tCL

tCLK

*SHADED PORTIONS OF INPUT SIGNALS ARE OPTIONAL. FOR BEST PERFORMANCE, WE RECOMMEND THAT THESE SIGNALS BE HELD LOW EXCEPT WHEN EXPLICITY SHOWN HIGH.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 1. Calibration Timing |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tC |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

SAMPLE* |

|

S |

|

tSL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tS |

||||||||

(INPUT) |

|

tSB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

BUSY |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(OUTPUT) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCB |

|

|

|

|

|

CLK* |

|

tFCD |

|

|

|

|

|

|

|

|

|

|

|

|

|

tCH |

|

|

|

|

|

|

|

|

|

|

|

|

tLCS |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

1 |

|

|

|

2 tCL |

3 |

|

15 |

16 |

|

17 |

|

|

|

|

||||||||||||||||

(INPUT) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

tCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

tCSH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(OUTPUT) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDATA |

|

|

|

|

|

|

|

|

|

|

tCD |

|

|

tSCL |

|

|

|

tDSH |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

OLD BIT 16 |

|

|

|

|

|

|

|

|

|

|

MSB |

|

BIT |

BIT |

|

BIT |

BIT |

|

|

BIT |

|||||||||||||||||

(OUTPUT) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

13 |

|

14 |

|

15 |

16 |

||||||||||

*SHADED PORTIONS OF INPUT SIGNALS ARE OPTIONAL. FOR BEST PERFORMANCE, WE RECOMMEND THAT THESE SIGNALS BE HELD LOW EXCEPT WHEN EXPLICITY SHOWN HIGH.

Figure 2. General Conversion Timing

–4– |

REV. A |

|

|

|

|

|

|

AD677 |

|

|

|

|

|

|

|

|

|

|

|

|

ORDERING GUIDE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Temperature |

|

|

|

Package |

|

|

Model |

Range |

S/(N+D) |

Max INL |

Package Description |

Option* |

|

|

|

|

|

|

|

|

|

|

AD677JN |

0°C to +70°C |

89 dB |

Typ Only |

Plastic 16-Pin DIP |

N-16 |

|

|

AD677KN |

0°C to +70°C |

90 dB |

±1.5 LSB |

Plastic 16-Pin DIP |

N-16 |

|

AD677JD |

0°C to +70°C |

89 dB |

Typ Only |

Ceramic 16-Pin DIP |

D-16 |

||

AD677KD |

0°C to +70°C |

90 dB |

±1.5 LSB |

Ceramic 16-Pin DIP |

D-16 |

||

AD677JR |

0°C to +70°C |

89 dB |

Typ Only |

Plastic 28-Lead SOIC |

R-28 |

||

AD677KR |

0°C to +70°C |

90 dB |

±1.5 LSB |

Plastic 28-Lead SOIC |

R-28 |

||

AD677AD |

–40°C to +85°C |

89 dB |

Typ Only |

Ceramic 16-Pin DIP |

D-16 |

||

|

AD677BD |

–40°C to +85°C |

90 dB |

±1.5 LSB |

Ceramic 16-Pin DIP |

D-16 |

|

*D = Ceramic DIP; N = Plastic DIP; R = Small Outline IC (SOIC).

ABSOLUTE MAXIMUM RATINGS*

VCC to VEE . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . –0.3 V to +26.4 V |

VDD to DGND . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . –0.3 V to +7 V |

Vcc to AGND . . . . . . . . . . . . . . . . . |

. . . . . . . . . . –0.3 V to +18 V |

VEE to AGND . . . . . . . . . . . . . . . . |

. . . . . . . . . . –18 V to +0.3 V |

AGND to DGND . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . +0.3 V |

Digiul Inputs to DGND . . . . . . . . . |

. . . . . . . . . . . . . 0 to +5.5 V |

Analog Inputs, VREF to AGND |

(VCC +0.3 V) to (VEE –0.3 V) |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . |

|

Soldering . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . +300°C, 10 sec |

Storage Temperature . . . . . . . . . . . . |

. . . . . . . . .–65°C to +150°C |

*Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD677 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. A |

–5– |

Loading...

Loading...