Fairchild Semiconductor 74F1071SCX, 74F1071SC, 74F1071MTCX, 74F1071MTC, 74F1071MSAX Datasheet

...

October 1994

Revised August 1999

74F1071

18-Bit Undershoot/Overshoot Clamp and ESD Protection Device

General Description

The 74F1071 is an 18-bit undershoot/overshoot clamp which is designed to limit bus voltages and also to protect more sensitive devices from electrical overstress due to electrostatic discharge (ESD). The inputs of the device aggressively clamp voltage excursions nominally at 0.5V below and 7V above ground.

Features

■18-bit array structure in 20-pin package

■FASTâ Bipolar voltage clamping action

■Dual center pin grounds for min inductance

■Robust design for ESD protection

■Low input capacitance

■Optimum voltage clamping for 5V CMOS/TTL applications

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

74F1071SC |

M20B |

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

|

|

|

74F1071MSA |

MSA20 |

20-Lead Shrink Small Outline Package (SSOP), EIAJ TYPE II, 5.3mm Wide |

|

|

|

74F1071MTC |

MTC20 |

20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |

|

|

|

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

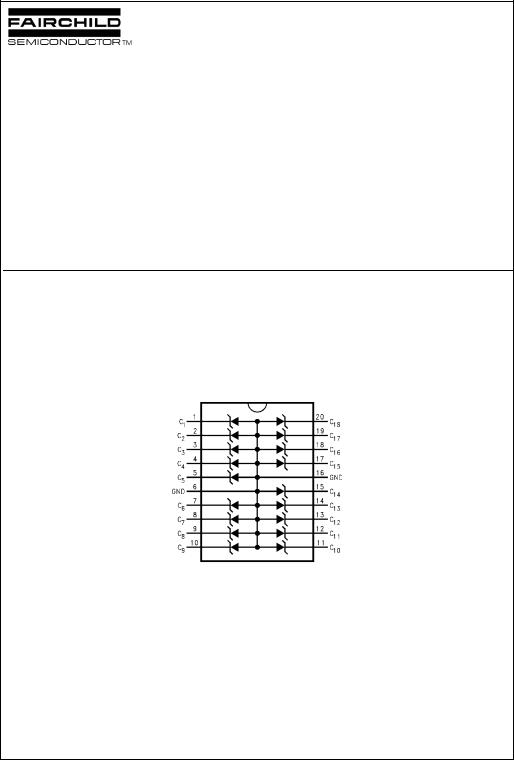

Connection Diagram

Note: Simplified Component Representation

FASTâ is a registered trademark of Fairchild Semiconductor Corporation.

Clamp Undershoot/Overshoot Bit-18 74F1071

© 1999 Fairchild Semiconductor Corporation |

DS011685 |

www.fairchildsemi.com |

74F1071

Absolute Maximum Ratings(Note 1)

Storage Temperature |

−65°C to +150°C |

Ambient Temperature under Bias |

−65°C to +125°C |

Junction Temperature under Bias |

−65°C to +150°C |

Input Voltage (Note 2) |

−0.5V to +6V |

Input Current (Note 2) |

−200 mA to +50 mA |

ESD (Note 3) |

|

Human Body Model |

|

(MIL-STD-883D method 3015.7) |

±10 kV |

IEC 801-2 |

±6 kV |

Machine Model (EIAJIC-121-1981) |

±2 kV |

DC Latchup Source Current |

|

(JEDEC Method 17) |

±500 mA |

Package Power Dissipation @+70°C |

|

SOIC Package |

800 mW |

Recommended Operating

Conditions

Free Air Ambient Temperature |

0°C to +70°C |

Reverse Bias Voltage |

0V to 5.25 VDC |

Thermal Resistance (θJA in Free Air) |

|

SOIC Package |

100°C/W |

SSOP Package |

110°C/W |

Note 1: Absolute maximum ratings are DC values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Voltage ratings may be exceeded if current ratings and junction temperature and power consumption ratings are not exceeded.

Note 3: ESD Rating for Direct contact discharge using ESD Simulation Tester. Higher rating may be realized in the actual application.

DC Electrical Characteristics

Symbol |

Parameter |

|

TA = +25°C |

|

TA = 0°C to +70°C |

Units |

Conditions |

||

Min |

Typ |

Max |

Min |

Max |

|||||

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

1.5 |

10 |

|

50 |

μA |

VIN = 5.25V; Untested Input @ GND |

|

|

|

|

3 |

20 |

|

100 |

VIN = 5.5V; Untested Input @ GND |

||

|

|

|

|

|

|||||

VZ |

Reverse Voltage |

6.6 |

6.9 |

7.2 |

5.9 |

7.7 |

V |

IZ = 1 mA; Untested Inputs @ GND |

|

|

|

|

7.1 |

7.5 |

|

8.0 |

IZ = 50 mA; Untested Inputs @ GND |

||

|

|

|

|

|

|||||

VF |

Forward Voltage |

−0.3 |

−0.6 |

−0.9 |

−0.3 |

−0.9 |

V |

IF = −18 mA; Untested Inputs @ 5V |

|

|

|

−0.5 |

−1.1 |

−1.5 |

−0.5 |

−1.5 |

IF = −200 mA; Untested Inputs @ 5V |

||

|

|

|

|||||||

ICT |

Adjacent Input Crosstalk |

|

|

3 |

|

|

% |

|

|

CIN |

Input Capacitance |

|

25 |

|

|

|

pF |

VBIAS = 0 VDC |

|

|

(small signal @ 1 MHz) |

|

13 |

|

|

|

VBIAS = 5 VDC |

||

|

|

|

|

|

|

||||

www.fairchildsemi.com |

2 |

Loading...

Loading...