Fairchild Semiconductor 74ACTQ273SJX, 74ACTQ273SCX, 74ACTQ273SC, 74ACTQ273PC, 74ACTQ273MTCX Datasheet

...

August 1989

Revised November 1999

74ACTQ273

Quiet Series Octal D-Type Flip-Flop

General Description

The ACTQ273 has eight edge-triggered D-type flip-flops with individual D inputs and Q outputs. The common buffered Clock (CP) and Master Reset (MR) input load and reset (clear) all flip-flops simultaneously.

The register is fully edge-triggered. The state of each D- type input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop’s Q output.

All outputs will be forced LOW independently of Clock or Data inputs by a LOW voltage level on the MR input. The device is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.

The ACTQ utilizes Fairchild Quiet Series technology to guarantee quiet output switching and improved dynamic threshold performance. FACT Quiet Series features

GTO output control and undershoot corrector in addition to a split ground bus for superior performance.

Features

■ICC reduced by 50%

■Guaranteed simultaneous switching noise level and dynamic threshold performance

■Guaranteed pin-to-pin skew AC performance

■Improved latch-up immunity

■Buffered common clock and asynchronous master reset

■Outputs source/sink 24 mA

■4 kV minimum ESD immunity

Ordering Code:

Order Number |

Package Number |

Package Description |

|

|

|

74ACTQ273SC |

M20B |

20-Lead Small Outline Integrated Circuit, JEDEC MS-013, 0.300” Wide Body |

|

|

|

74ACTQ273SJ |

M20D |

20-Lead Small Outline Package, EIAJ TYPE II, 5.3mm Wide |

|

|

|

74ACTQ273MTC |

MTC20 |

20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide |

|

|

|

74ACTQ273PC |

N20A |

20-Lead Plastic Dual-In-Line Package, JEDEC MS-001, 0.300” Wide |

|

|

|

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

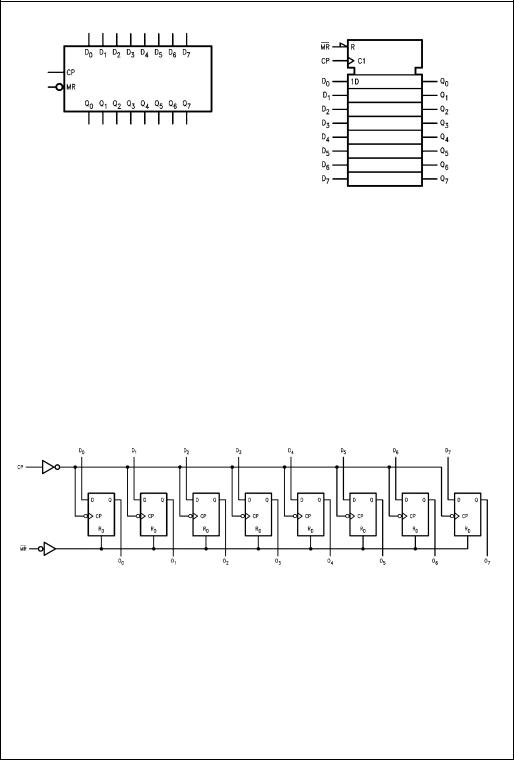

Connection Diagram |

Pin Descriptions |

||||

|

|

|

|

||

|

|

Pin Names |

Description |

||

|

|

|

|

|

|

|

|

|

D0–D7 |

Data Inputs |

|

|

|

|

|

Master Reset |

|

|

|

|

MR |

|

|

|

|

|

CP |

Clock Pulse Input |

|

|

|

|

Q0–Q7 |

Data Outputs |

|

FACT , FACT Quiet Series , and GTO are trademarks of Fairchild Semiconductor Corporation.

Flop-Flip Type-D Octal Series Quiet 74ACTQ273

© 1999 Fairchild Semiconductor Corporation |

DS010585 |

www.fairchildsemi.com |

74ACTQ273

Logic Symbols

IEEE/IEC

Mode Select-Function Table

Operating Mode |

|

|

Inputs |

|

Outputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

CP |

Dn |

Qn |

Reset (Clear) |

|

L |

X |

X |

L |

|

|

|

|

|

|

Load “1” |

|

H |

|

H |

H |

|

|

|

|

|

|

Load “0” |

|

H |

|

L |

L |

|

|

|

|

|

|

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

= LOW-to-HIGH Transition

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com |

2 |

Absolute Maximum Ratings(Note 1)

Supply Voltage (VCC) |

|

|

− 0.5V to + 7.0V |

||

DC Input Diode Current (IIK) |

|

||||

VI = |

− 0.5V |

|

|

|

− 20 mA |

VI = |

VCC + 0.5V |

|

|

|

+ 20 mA |

DC Input Voltage (VI) |

|

|

− 0.5V to VCC + 0.5V |

||

DC Output Diode Current (IOK) |

|

||||

VO = |

− 0.5V |

|

|

|

− 20 mA |

VO = |

VCC + 0.5V |

|

|

+ 20 mA |

|

DC Output Voltage (VO) |

|

− 0.5V to VCC + 0.5V |

|||

DC Output Source |

|

|

|

|

|

or Sink Current (IO) |

|

|

± 50 mA |

||

DC VCC or Ground Current |

|

||||

per Output Pin (I |

CC |

or I |

) |

± 50 mA |

|

|

|

|

GND |

|

|

Storage Temperature (TSTG) |

− 65° C to + 150° C |

||||

DC Latch-up Source or |

|

|

|||

Sink Current |

|

|

|

± 300 mA |

|

Junction Temperature (TJ) |

|

||||

PDIP |

|

|

|

140° C |

|

Recommended Operating

Conditions

Supply Voltage (V |

) |

4.5V to 5.5V |

|

CC |

|

Input Voltage (V ) |

|

0V to V |

I |

|

CC |

Output Voltage (VO) |

0V to VCC |

|

Operating Temperature (TA) |

− 40° C to + 85° C |

|

Minimum Input Edge Rate ∆ V/∆ t |

|

|

VIN from 0.8V to 2.0V |

|

|

VCC @ 4.5V, 5.5V |

125 mV/ns |

|

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT circuits outside databook specifications.

DC Electrical Characteristics

Symbol |

Parameter |

VCC |

TA |

= + 25° C |

TA = − 40° C to + 85° C |

Units |

|

Conditions |

|||

|

|

(V) |

Typ |

|

Guaranteed Limits |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

VIH |

Minimum HIGH Level |

4.5 |

1.5 |

|

2.0 |

2.0 |

V |

VOUT = |

0.1V |

||

|

Input Voltage |

5.5 |

1.5 |

|

2.0 |

2.0 |

or VCC − |

0.1V |

|||

|

|

|

|||||||||

VIL |

Maximum LOW Level |

4.5 |

1.5 |

|

0.8 |

0.8 |

V |

VOUT = |

0.1V |

||

|

Input Voltage |

5.5 |

1.5 |

|

0.8 |

0.8 |

or VCC − |

0.1V |

|||

|

|

|

|||||||||

VOH |

Minimum HIGH Level |

4.5 |

4.49 |

|

4.4 |

4.4 |

V |

IOUT = |

− |

50 µ A |

|

|

Output Voltage |

5.5 |

5.49 |

|

5.4 |

5.4 |

|||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

VIN = |

VIL or VIH |

||

|

|

4.5 |

|

|

3.86 |

3.76 |

V |

IOH = |

− |

24 mA |

|

|

|

5.5 |

|

|

4.86 |

4.76 |

|

IOH = |

− 24 mA (Note 2) |

||

VOL |

Maximum LOW Level |

4.5 |

0.001 |

|

0.1 |

0.1 |

V |

IOUT = |

50 µ A |

||

|

Output Voltage |

5.5 |

0.001 |

|

0.1 |

0.1 |

|||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

VIN = |

VIL or VIH |

||

|

|

4.5 |

|

|

0.36 |

0.44 |

V |

IOL = |

24 mA |

||

|

|

5.5 |

|

|

0.36 |

0.44 |

|

IOL = |

24 mA (Note 2) |

||

IIN |

Maximum Input Leakage Current |

5.5 |

|

|

± 0.1 |

± 1.0 |

µ A |

VI = |

VCC, GND |

||

ICCT |

Maximum ICC/Input |

5.5 |

0.6 |

|

|

1.5 |

mA |

VI = |

VCC − 2.1V |

||

IOLD |

Minimum Dynamic |

5.5 |

|

|

|

75 |

mA |

VOLD = |

1.65V Max |

||

IOHD |

Output Current (Note 3) |

5.5 |

|

|

|

− 75 |

mA |

VOHD = |

|

3.85V Min |

|

ICC |

Maximum Quiescent Supply Current |

5.5 |

|

|

4.0 |

40.0 |

µ A |

VIN = |

VCC or GND |

||

VOLP |

Quiet Output |

5.0 |

1.1 |

|

1.5 |

|

V |

Figure 1Figure 2 |

|||

|

Maximum Dynamic VOL |

|

|

(Note 4) |

|

||||||

|

|

|

|

|

|

|

|

||||

VOLV |

Quiet Output |

5.0 |

− 0.6 |

|

− 1.2 |

|

V |

Figure 1Figure 2 |

|||

|

Minimum Dynamic VOL |

|

|

(Note 4) |

|

||||||

|

|

|

|

|

|

|

|

||||

VIHD |

Minimum HIGH Level Dynamic Input Voltage |

5.0 |

1.9 |

|

2.2 |

|

V |

(Note 5) |

|||

VILD |

Maximum LOW Level Dynamic Input Voltage |

5.0 |

1.2 |

|

0.8 |

|

V |

(Note 5) |

|

||

Note 2: All outputs loaded; thresholds on input associated with output under test.

Note 3: Maximum test duration 2.0 ms, one output loaded at a time.

Note 4: Max number of outputs defined as (n). n − 1 Data inputs are driven 0V to 3V; one output @ GND.

Note 5: Max number of Data Inputs (n) switching. (n − 1) Inputs switching 0V to 3V (ACTQ). Input-under-test switching: 3V to threshold (VILD), 0V to threshold (VIHD) f = 1 MHz.

74ACTQ273

3 |

www.fairchildsemi.com |

Loading...

Loading...