MOTOROLA MC10H102P, MC10H102FNR2, MC10H102M, MC10H102MEL, MC10H102ML1 Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

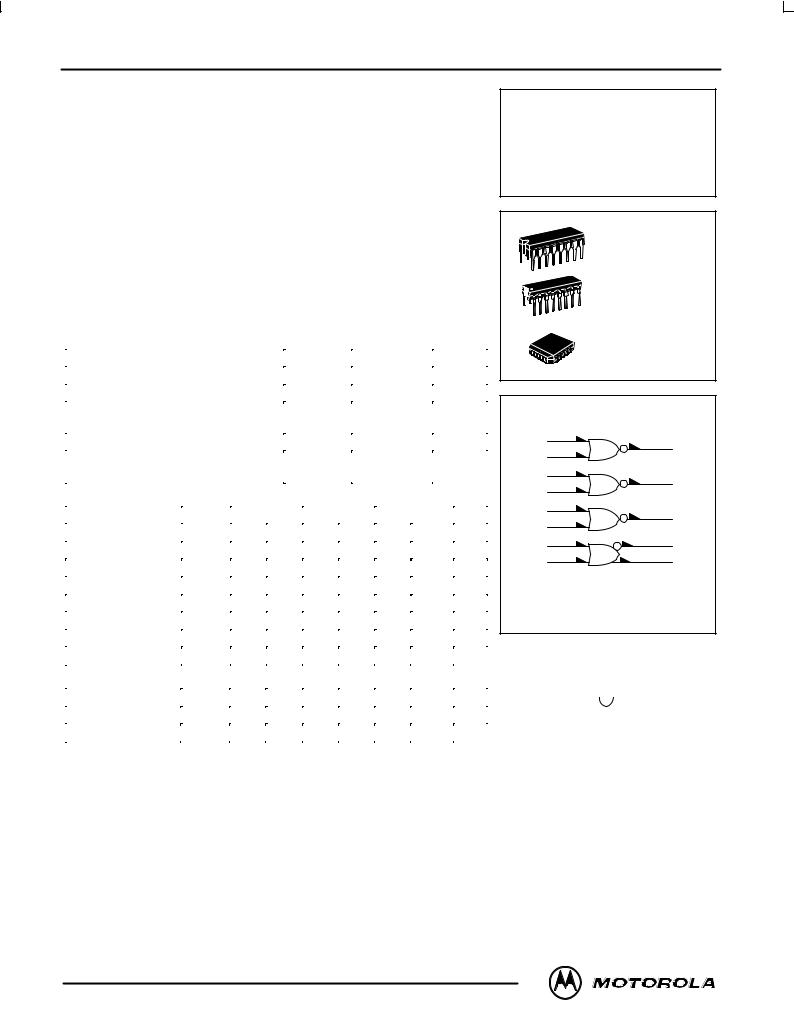

Quad 2-Input NOR Gate

The MC10H102 is a quad 2±input NOR gate. The MC10H102 provides one gate with OR/NOR outputs. This MECL 10H part is a functional/pinout duplication of the standard MECL 10K family part, with 100% improvement in propagation delay, and no increases in power± supply current.

•Propagation Delay, 1.0 ns Typical

•Power Dissipation 25 mW/Gate (same as MECL 10K)

•Improved Noise Margin 150 mV (Over Operating Voltage and Temperature Range)

•Voltage Compensated

•MECL 10K±Compatible

MAXIMUM RATINGS

Characteristic |

Symbol |

Rating |

Unit |

|

|

|

|

Power Supply (VCC = 0) |

VEE |

±8.0 to 0 |

Vdc |

Input Voltage (VCC = 0) |

VI |

0 to VEE |

Vdc |

Output Current Ð Continuous |

Iout |

50 |

mA |

Ð Surge |

|

100 |

|

|

|

|

|

Operating Temperature Range |

TA |

0 to +75 |

°C |

Storage Temperature Range Ð Plastic |

Tstg |

±55 to +150 |

°C |

Ð Ceramic |

|

±55 to +165 |

°C |

|

|

|

|

ELECTRICAL CHARACTERISTICS (VEE = ±5.2 V ±5%) (See Note)

|

|

0° |

25° |

|

75° |

|

|||

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Min |

Max |

Min |

Max |

Min |

|

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

Power Supply Current |

IE |

Ð |

29 |

Ð |

26 |

Ð |

|

29 |

mA |

Input Current High |

IinH |

Ð |

425 |

Ð |

265 |

Ð |

|

265 |

μA |

Input Current Low |

IinL |

0.5 |

Ð |

0.5 |

Ð |

0.3 |

|

Ð |

μA |

High Output Voltage |

VOH |

±1.02 |

±0.84 |

±0.98 |

±0.81 |

±0.92 |

|

±0.735 |

Vdc |

Low Output Voltage |

VOL |

±1.95 |

±1.63 |

±1.95 |

±1.63 |

±1.95 |

|

±1.60 |

Vdc |

High Input Voltage |

VIH |

±1.17 |

±0.84 |

±1.13 |

±0.81 |

±1.07 |

|

±0.735 |

Vdc |

Low Input Voltage |

VIL |

±1.95 |

±1.48 |

±1.95 |

±1.48 |

±1.95 |

|

±1.45 |

Vdc |

AC PARAMETERS

Propagation Delay |

tpd |

0.4 |

1.25 |

0.4 |

1.25 |

0.4 |

1.4 |

ns |

Rise Time |

tr |

0.5 |

1.5 |

0.5 |

1.6 |

0.55 |

1.7 |

ns |

Fall Time |

tf |

0.5 |

1.5 |

0.5 |

1.6 |

0.55 |

1.7 |

ns |

NOTE:

Each MECL 10H series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 Iinear fpm is maintained. Outputs are terminated through a 50±ohm resistor to ±2.0 volts.

MC10H102

L SUFFIX

CERAMIC PACKAGE

CASE 620±10

P SUFFIX

PLASTIC PACKAGE

CASE 648±08

FN SUFFIX

PLCC

CASE 775±02

LOGIC DIAGRAM

4

2

5 |

|

|

6 |

3 |

|

7 |

||

|

||

10 |

14 |

|

11 |

||

|

||

12 |

15 |

|

13 |

9 |

|

|

VCC1 = PIN 1 |

|

|

VCC2 = PIN 16 |

|

|

VEE = PIN 8 |

DIP

PIN ASSIGNMENT

VCC1 |

|

1 |

|

16 |

|

|

VCC2 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

AOUT |

|

2 |

|

15 |

|

|

DOUT |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

BOUT |

|

3 |

|

14 |

|

|

COUT |

|

|

|

|

|

|||||

AIN |

|

4 |

|

13 |

|

|

DIN |

|

|

|

|

|

|||||

AIN |

|

5 |

|

12 |

|

|

DIN |

|

|

|

|

|

|||||

BIN |

|

6 |

|

11 |

|

|

CIN |

|

|

|

|

|

|||||

BIN |

|

7 |

|

10 |

|

|

CIN |

|

|

|

|

|

|||||

VEE |

|

8 |

|

9 |

|

|

DOUT |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Pin assignment is for Dual±in±Line Package.

For PLCC pin assignment, see the Pin Conversion

Tables on page 6±11 of the Motorola MECL Data

Book (DL122/D).

3/93

Motorola, Inc. 1996 |

2±66 |

REV 5 |

Loading...

Loading...