Analog Devices AD571SD, AD571KD, AD571JD Datasheet

a

10-Bit A/D Converter

AD571*

FEATURES

Complete A/D Converter with Reference and Clock Fast Successive Approximation Conversion: 40 ms max

No Missing Codes Over Temperature 08C to +708C: AD571K

–558C to +1258C: AD571S

Digital Multiplexing: Three-State Outputs 18-Pin Ceramic DIP

Low Cost Monolithic Construction

PRODUCT DESCRIPTION

The AD571 is an 10-bit successive approximation A/D converter consisting of a DAC, voltage reference, clock, comparator, successive approximation register and output buffers—all fabricated on a single chip. No external components are required to perform a full accuracy 10-bit conversion in 40 μs.

Operating on supplies of +5 V to +15 V and –15 V, the AD571 will accepts analog inputs of 0 V to +10 V unipolar of

±5 V bipolar, externally selectable. When the BLANK and CONVERT input is driven low, the three-state outputs will be open and a conversion will commence. Upon completion of the conversion, the DATA READY line goes low and the data appears at the output. Pulling the BLANK and CONVERT input high blanks the outputs and readies the device for the next conversion. The AD571 executes a true 10-bit conversion with no missing codes in 40 μs maximum.

The AD571 is available in two version for the 0°C to +70°C temperature range, the AD571J and K. The AD571S guarantees 10-bit accuracy and no missing codes from –55°C to +125°C.

*Covered by Patent Nos. 3,940,760; 4,213,806; 4,136,349.

|

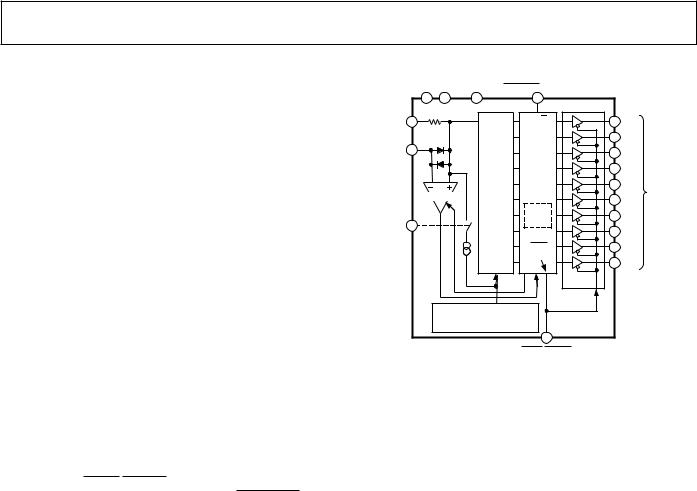

FUNCTIONAL BLOCK DIAGRAM |

|

||||||

|

V+ |

|

DIGITAL |

BLANK & |

|

|

||

|

V– |

COMMON CONVERT CONTROL |

|

|

||||

|

10 |

12 |

|

16 |

11 |

|

|

|

ANALOG |

5k |

|

|

B & C |

|

|

MSB |

|

13 |

|

|

|

|

9 |

|||

IN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

ANALOG 14 |

|

|

|

|

|

7 |

|

|

COMMON |

|

|

|

|

|

|

|

|

|

|

|

|

|

10-BIT |

|

6 |

|

|

|

|

|

|

SAR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10-BIT |

|

|

5 |

|

|

|

|

|

CURRENT |

|

|

BIT |

|

|

|

|

|

|

|

|

||

|

COMPARATOR |

OUTPUT |

|

|

4 |

OUTPUTS |

||

|

|

|

|

DAC |

|

|

|

|

BIPOLAR |

|

|

|

|

INT. |

|

3 |

|

|

|

|

|

CLOCK |

|

|

||

OFFSET 15 |

|

|

|

|

|

2 |

|

|

CONTROL |

|

|

|

|

|

|

|

|

|

|

|

|

|

DATA |

|

1 |

|

|

|

|

|

|

READY |

|

|

|

|

|

|

|

|

|

|

18 |

LSB |

|

|

|

|

|

|

3 STATE |

|

|

|

|

|

|

|

|

BUFFERS |

|

|

|

|

|

|

|

|

AUTO BLANK |

|

|

|

|

|

|

|

|

CONTROL |

|

|

|

|

TEMPERATURE COMPENSATED |

|

|

|

|||

|

|

BURIED ZENER REFERENCE |

AD571 |

|

|

|||

|

|

|

AND DAC CONTROL |

|

|

|

||

17

DATA READY

PRODUCT HIGHLIGHTS

1.The AD571 is a complete 10-bit A/D converter. No external

components are required to perform a conversion. Full-scale calibration accuracy of ±0.3% is achieved without external trims.

2.The AD571 is a single chip device employing the most advanced IC processing techniques. Thus, the user has at his disposal a truly precision component with the reliability and low cost inherent in monolithic construction,

3.The AD571 accepts either unipolar (0 V to +10 V) or bipolar (–5 V to +5 V) analog inputs by grounding or opening a single pin.

4.The device offers true 10-bit accuracy and exhibits no missing codes over its entire operating temperature range.

5.Operation is guaranteed with –15 V and +5 V or +15 V supplies. The device will also operate with a –12 V supply.

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

|

|

(TA = +258C, V+ = +5 V, V– = –12 V or –15 V, all voltages measured with respect to |

|||||||||

AD571–SPECIFICATIONS digital common, |

unless otherwise noted) |

|

|

|

|

||||||

|

|

AD571J |

|

|

|

AD571K |

|

|

AD571S |

|

|

Model |

Min |

Typ |

Max |

|

Min |

Typ |

Max |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

|

|

|

|

|

|

RESOLUTION |

|

|

10 |

|

|

|

10 |

|

|

10 |

Bits |

|

|

|

|

|

|

|

|

|

|

|

|

RELATIVE ACCURACY, TA |

|

|

61 |

|

|

|

61/2 |

|

|

61 |

LSB |

TMIN to TMAX |

|

|

61 |

|

|

|

61/2 |

|

|

61 |

LSB |

FULL-SCALE CALIBRATION |

|

±2 |

|

|

|

±2 |

|

|

±2 |

|

LSB |

|

|

|

|

|

|

|

|

|

|

|

|

UNIPOLAR OFFSET |

|

|

61 |

|

|

|

61/2 |

|

|

61 |

LSB |

|

|

|

|

|

|

|

|

|

|

|

|

BIPOLAR OFFSET |

|

|

61 |

|

|

|

61/2 |

|

|

61 |

LSB |

|

|

|

|

|

|

|

|

|

|

|

|

DIFFERENTIAL NONLINEAIRTY, TA |

10 |

|

|

|

10 |

|

|

10 |

|

|

Bits |

TMIN to TMAX |

9 |

|

|

|

10 |

|

|

10 |

|

|

Bits |

TEMPERATURE RANGE |

0 |

|

+70 |

|

0 |

|

+70 |

–55 |

|

+125 |

°C |

|

|

|

|

|

|

|

|

|

|

|

|

TEMPERATURE COEFFICIENTS |

|

|

|

|

|

|

|

|

|

|

|

Unipolar Offset |

|

|

62 |

|

|

|

61 |

|

|

62 |

LSB |

Bipolar Offset |

|

|

62 |

|

|

|

61 |

|

|

62 |

LSB |

Full-Scale Calibration2 |

|

|

64 |

|

|

|

62 |

|

|

65 |

LSB |

POWER SUPPLY REJECTION |

|

|

|

|

|

|

|

|

|

|

|

CMOS Positive Supply |

|

|

|

|

|

|

|

|

|

|

|

+13.5 V ≤ V + ≤ +16.5 V |

– |

– |

– |

|

|

|

61 |

– |

– |

– |

LSB |

TTL Positive Supply |

|

|

|

|

|

|

|

|

|

|

|

+4.5 V ≤ V + ≤ +5.5 V |

|

|

62 |

|

|

|

61 |

|

|

62 |

LSB |

Negative Supply |

|

|

|

|

|

|

|

|

|

|

|

–16.0 V ≤ V – ≤ –13.5 V |

|

|

62 |

|

|

|

61 |

|

|

62 |

LSB |

|

|

|

|

|

|

|

|

|

|

|

|

ANALOG INPUT IMPEDANCE |

3.0 |

5.0 |

7.0 |

|

3.0 |

5.0 |

7.0 |

3.0 |

5.0 |

7.0 |

kΩ |

|

|

|

|

|

|

|

|

|

|

|

|

ANALOG INPUT RANGES |

|

|

|

|

|

|

|

|

|

|

|

Unipolar |

0 |

|

+10 |

|

0 |

|

+10 |

0 |

|

+10 |

V |

Bipolar |

–5 |

|

+5 |

|

–5 |

|

+5 |

–5 |

|

+5 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUT CODING |

|

|

|

|

|

|

|

|

|

|

|

Unipolar |

Positive True Binary |

|

|

Positive True Binary |

|

Positive True Binary |

|

|

|||

Bipolar |

Positive True Offset Binary |

|

Positive True Offset Binary |

Positive True Offset Binary |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

Output Sink Current |

|

|

|

|

|

|

|

|

|

|

|

(VOUT = 0.4 V max, TMIN to TMAX) |

3.2 |

|

|

|

3.2 |

|

|

3.2 |

|

|

mA |

Output Source Current1 |

|

|

|

|

|

|

|

|

|

|

|

(VOUT = 2.4 V max, TMIN to TMAX) |

0.5 |

|

|

|

0.5 |

|

|

0.5 |

|

|

mA |

Output Leakage |

|

|

640 |

|

|

|

640 |

|

|

640 |

μA |

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC INPUT |

|

|

|

|

|

|

|

|

|

|

μA |

Input Current |

|

|

6100 |

|

|

|

6100 |

|

|

6100 |

|

Logic “1” |

2.0 |

|

|

|

2.0 |

|

|

2.0 |

|

|

V |

Logic “0” |

|

|

0.8 |

|

|

|

0.8 |

|

|

0.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

CONVERSION TIME, TMIN to TMAX |

15 |

25 |

40 |

|

15 |

25 |

40 |

15 |

25 |

40 |

μs |

|

|

|

|

|

|

|

|

|

|

|

|

POWER SUPPLY |

|

|

|

|

|

|

|

|

|

|

|

V+ |

+4.5 |

+5.0 |

+7.0 |

|

+4.5 |

+5.0 |

+16.5 |

+4.5 |

+5.0 |

+7.0 |

V |

V– |

–12.0 |

–15 |

–16.5 |

|

–12.0 |

–15 |

–16.5 |

–12.0 |

–15 |

–16.5 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

OPERATING CURRENT |

|

|

|

|

|

|

|

|

|

|

|

V+ |

|

7 |

10 |

|

|

7 |

10 |

|

7 |

10 |

mA |

V– |

|

9 |

15 |

|

|

9 |

15 |

|

9 |

15 |

mA |

|

|

|

|

|

|

|

|

|

|

|

|

PACKAGE OPTION2 |

|

|

|

|

|

|

|

|

|

|

|

Ceramic DIP (D-18) |

|

AD571JD |

|

|

|

AD571KD |

|

AD571SD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES

1The data output lines have active pull-ups to source 0.5 mA. The DATA READY line is open collector with a nominal 6 kΩ internal pull-up resistor.

2For details on grade and package offerings for SD-grade in accordance with MIL-STD-883, refer to Analog Devices’ Military Products databook or current /883B data sheet.

Specifications subject to change without notice.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

–2– |

REV. A |

|

|

|

|

|

|

|

|

|

|

|

|

|

AD571 |

||

ABSOLUTE MAXIMUM RATINGS |

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

V+ to Digital Common |

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

AD571J . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to +7 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

AD571K . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to +16.5 V |

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

V– to Digital Common |

. . . . . . . . . . . . . . . . . . . 0 V to –16.0 V |

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

Analog Common to Digital Common . . . . . . . . . . . . . . . ±1 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Volts |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Analog Input to Analog Common . . . . . . . . . . . . . . . . . ±15 V |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

||

Control Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0 V to V+ |

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Digital Outputs (Blank Mode) . . . . . . . . . . . . . . . . . . 0 V to V+ |

TH |

4 |

|

|

|

|

|

|

|

|

|

|

|

||

V |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 800 mW |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

CIRCUIT DESCRIPTION |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

The AD571 is a complete 10-bit A/D converter which requires |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

no external components to provide the complete successive- |

|

|

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

|

approximation analog-to-digital conversion function. A block |

|

|

|

|

|

|

|

V+ – Volts |

|

|

|

|

|

||

diagram of the AD571 is shown on front page of this data sheet. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Upon receipt of the CONVERT command, the internal 10-bit |

|

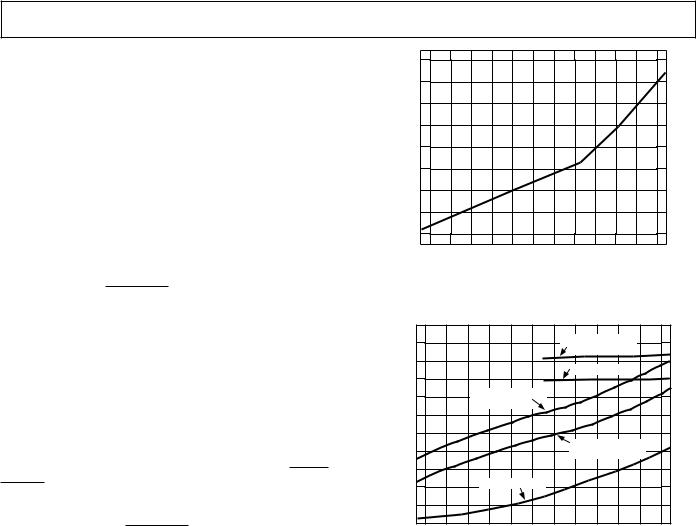

Figure 1. Logic Threshold (AD571K Only) |

|

||||||||||||

current output DAC is sequenced by the I2L successive- |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

approximation register (SAR) from its most-significant bit |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

(MSB) to least-significant bit (LSB) to provide an output cur- |

|

11 |

|

|

|

|

|

|

I–, CONVERT MODE |

|

|||||

rent which accurately balances the input signal current through |

|

|

|

|

|

|

|

|

AIN = 0 to +10V |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||||

the 5 kΩ input resistor. The comparator determines whether the |

|

10 |

|

|

|

|

|

|

|

I–, BLANK MODE |

|

||||

|

|

|

|

|

|

|

|

|

|

||||||

addition of each successively-weighted bit current causes the |

– mA |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

DAC current sum to be greater or less than the input current; if |

8 |

|

|

I+, CONVERT MODE |

|

|

|

|

|

|

|||||

the sum is less the bit is left on, if more, the bit is turned off. Af- |

CURRENT |

|

|

|

|

|

VIN = 0V |

|

|

|

|

|

|

||

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

ter testing all the bits, the SAR contains a 10-bit binary code |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

which accurately represents the input signal to within ±1/2 LSB |

|

6 |

|

|

|

|

|

|

|

I+, CONVERT MODE |

|

||||

SUPPLY |

|

|

|

|

|

|

|

|

|

||||||

(0.05%). |

|

5 |

|

|

|

|

|

|

|

|

VIN = +10V |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

Upon completion of the sequence, the SAR sends out a DATA |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I+, BLANK MODE |

|

|

|

|

|

|

||||

READY signal (active low), which also brings the three-state |

|

3 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

buffers out of their “open” state, making the bit output lines be- |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

come active high or low, depending on the code in the SAR. |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

When the BLANK and CONVERT line is brought high, the |

|

4.5 5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

16 |

||

output buffers again go “open”, and the SAR is prepared for |

|

|

|

|

|

|

|

V+/V– – Volts |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

another conversion cycle. Details of the timing are given in the |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Control and Timing section. |

Figure 2. Supply Currents vs. Supply Levels and |

||||||||||||||

The temperature compensated buried Zener reference provides the primary voltage reference to the DAC and guarantees excellent stability with both time and temperature. The bipolar offset input controls a switch which allows the positive bipolar offset current (exactly equal to the value of the MSB less 1/2 LSB) to be injected into the summing (+) node of the comparator to offset the DAC output. Thus the nominal 0 V to +10 V unipolar input range becomes a –5 V to +5 V range. The 5 kΩ thinfilm input resistor is trimmed so that with a full-scale input signal, an input current will be generated which exactly matches the DAC output with all bits on. (The input resistor is trimmed slightly low to facilitate user trimming, as discussed on the next page.)

POWER SUPPLY SELECTION

The AD571 is designed for optimum performance using a +5 V and –15 V supply, for which the AD571J and AD571S are specified. AD571K will also operate with up to a +15 V supply, which allows direct interface to CMOS logic. The input logic threshold is a function of V+ as shown in Figure 1. The supply current drawn by the device is a function of both V+ and the operating mode (BLANK or CONVERT). These supply currents variations are shown in Figure 2. The supply currents change only moderately over temperature as shown in Figure 6.

Operating Modes

CONNECTING THE AD571 FOR STANDARD OPERATION

The AD571 contains all the active components required to perform a complete A/D conversion. For most situations, all that is necessary is connection of the power supply (+5 V and –15 V), the analog input, and the conversion start pulse. However, there are some features and special connections which should be considered for optimum performance. The functional pinout is shown in Figure 3.

REV. A |

–3– |

Loading...

Loading...