Analog Devices AD538SD, AD538BD, AD538AD, AD539SE-883B, AD539SD-883B Datasheet

...

a |

Real-Time Analog |

|

Computational Unit (ACU) |

||

|

|

|

|

|

AD538 |

|

|

|

FEATURES

VZ m

VOUT = VY Transfer Function

VX

Wide Dynamic Range (Denominator) –1000:1

Simultaneous Multiplication and Division

Resistor-Programmable Powers and Roots

No External Trims Required

Low Input Offsets <100 mV

Low Error 60.25% of Reading (100:1 Range)

+2 V and +10 V On-Chip References

Monolithic Construction

APPLICATIONS

Oneor Two-Quadrant Mult/Div Log Ratio Computation Squaring/Square Rooting

Trigonometric Function Approximations Linearization Via Curve Fitting Precision AGC

Power Functions

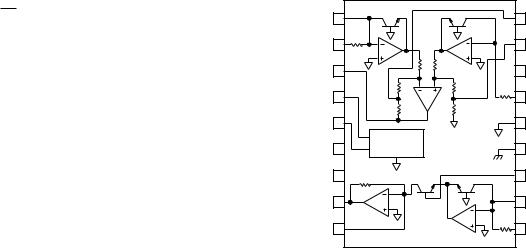

FUNCTIONAL BLOCK DIAGRAM

IZ |

1 |

|

|

|

18 |

A |

VZ |

|

25kV |

LOG |

|

|

|

2 |

|

RATIO |

|

17 |

D |

|

B |

3 |

|

|

|

16 |

IX |

+10V |

4 |

|

|

|

15 |

VX |

|

|

|

100V |

100V |

25kV |

|

|

|

|

|

SIGNAL |

||

+2V |

5 |

|

|

|

14 |

|

|

|

|

GND |

|||

|

|

|

INTERNAL |

|

|

|

+VS |

6 |

|

VOLTAGE |

AD538 |

13 |

PWR |

|

REFERENCE |

GND |

||||

–V |

7 |

OUTPUT |

|

12 |

C |

|

S |

|

|

|

|

||

|

|

25kV |

|

|

|

|

VO |

8 |

|

ANTILOG |

|

11 |

IY |

|

|

|

|

|

|

|

I |

9 |

|

|

LOG |

10 |

VY |

|

|

|

|

|

25kV |

|

PRODUCT DESCRIPTION

The AD538 is a monolithic real-time computational circuit that provides precision analog multiplication, division and exponentiation. The combination of low input and output offset voltages and excellent linearity results in accurate computation over an unusually wide input dynamic range. Laser wafer trimming makes multiplication and division with errors as low as 0.25% of reading possible, while typical output offsets of 100 V or less add to the overall off-the-shelf performance level. Real-time analog signal processing is further enhanced by the device’s 400 kHz bandwidth.

The AD538’s overall transfer function is VO = VY (VZ /VX)m. Programming a particular function is via pin strapping. No external components are required for one-quadrant (positive input) multiplication and division. Two-quadrant (bipolar numerator) division is possible with the use of external level shifting and scaling resistors. The desired scale factor for both multiplication and division can be set using the on-chip +2 V or +10 V references, or controlled externally to provide simultaneous multiplication and division. Exponentiation with an m value from 0.2 to 5 can be implemented with the addition of one or two external resistors.

REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Direct log ratio computation is possible by using only the log ratio and output sections of the chip. Access to the multiple summing junctions adds further to the AD538’s flexibility.

Finally, a wide power supply range of ±4.5 V to ±18 V allows operation from standard ±5 V, ±12 V and ±15 V supplies.

The AD538 is available in two accuracy grades (A and B) over the industrial (–25°C to +85°C) temperature range and one grade (S) over the military (–55°C to +125°C) temperature range. The device is packaged in an 18-lead TO-118 hermetic side-brazed ceramic DIP. A-grade chips are also available.

PRODUCT HIGHLIGHTS

1.Real-time analog multiplication, division and exponentiation.

2.High accuracy analog division with a wide input dynamic range.

3.On-chip +2 V or +10 V scaling reference voltages.

4.Both voltage and current (summing) input modes.

5.Monolithic construction with lower cost and higher reliability than hybrid and modular circuits.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 1999 |

AD538–SPECIFICATIONS (VS = 615 V, TA = +258C unless otherwise noted)

|

|

|

|

AD538AD |

|

|

|

|

AD538BD |

|

|

|

AD538SD |

|

|

|

||||||

Parameters |

Conditions |

Min |

Typ |

|

Max |

Min |

Typ |

|

Max |

Min Typ |

|

Max |

Units |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MULTIPLIER DIVIDER |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PERFORMANCE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Nominal Transfer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Function |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VZ |

m |

|

|

|

|

VZ |

m |

|

|

|

VZ |

m |

|

|

|

|||

|

10 V ≥ VX, VY, VZ ≥ 0 |

VO |

= VY |

|

|

|

|

VO |

= Vy |

|

|

|

|

VO |

= VY |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

VX |

|

|

|

|

|

VX |

|

|

|

|

VX |

|

|

|

|

|||

|

|

|

|

|

|

|

IZ m |

|

|

|

|

|

IZ m |

|

|

|

|

IZ m |

|

|||

|

400 µA ≥ IX, IY, IZ ≥ 0 |

VO |

= 25 kΩ × IY |

|

|

VO |

= 25 kΩ × IY |

|

|

VO |

= 25 kΩ × IY |

|

|

|

||||||||

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

IX |

|

|

|

|

|

IX |

|

|

|

|

IX |

|

|||

Total Error Terms |

100 mV ≤ VX ≤ 10 V |

|

|

±0.5 |

|

61 |

|

|

± 0.25 |

60.5 |

|

± 0.5 |

|

61 |

% of Reading + |

|||||||

100:1 Input Range1 |

100 mV ≤ VY ≤ 10 V |

|

|

±200 |

|

6500 |

|

|

± 100 |

|

6250 |

|

± 200 |

|

6500 |

µV |

||||||

|

100 mV ≤ VZ ≤ 10 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VZ ≤ 10 VX, m = 1.0 |

|

|

±1 |

|

62 |

|

|

± 0.5 |

|

61 |

|

± 1.25 |

|

62.5 |

|

||||||

|

TA = TMIN to TMAX |

|

|

|

|

|

|

|

|

% of Reading + |

||||||||||||

|

|

|

|

±450 |

|

6750 |

|

|

± 350 |

|

6500 |

|

± 750 |

|

61000 |

µV |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Wide Dynamic Range2 |

10 mV ≤ VX ≤ 10 V |

|

|

±1 |

|

62 |

|

|

± 0.5 |

|

61 |

|

± 1 |

|

62 |

% of Reading + |

||||||

|

1 mV ≤ VY ≤ 10 V |

|

|

±200 |

|

6500 |

|

|

± 100 |

|

6250 |

|

± 200 |

|

6500 |

µV + |

||||||

|

0 mV ≤ VZ ≤ 10 V |

|

|

±100 |

|

6250 |

|

|

± 750 |

|

6150 |

|

± 200 |

|

6250 |

µV × (VY + VZ)/VX |

||||||

|

VZ ≤ 10 VX, m = 1.0 |

|

|

±1 |

|

63 |

|

|

± 1 |

|

62 |

|

± 2 |

|

64 |

|

||||||

|

TA = TMIN to TMAX |

|

|

|

|

|

|

|

|

% of Reading + |

||||||||||||

|

|

|

|

±450 |

|

6750 |

|

|

± 350 |

|

6500 |

|

± 750 |

|

61000 |

µV + |

||||||

|

|

|

|

±450 |

|

6750 |

|

|

± 350 |

|

6500 |

|

± 750 |

|

61000 |

µV × (VY + VZ)/VX |

||||||

Exponent (m) Range |

TA = TMIN to TMAX |

0.2 |

|

|

|

|

5 |

|

0.2 |

|

|

|

|

5 |

0.2 |

|

|

|

5 |

|

|

|

OUTPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CHARACTERISTICS |

|

|

|

±200 |

|

|

|

|

|

± 100 |

|

|

|

|

± 200 |

|

|

|

µV |

|||

Offset Voltage |

VY = 0, VC = –600 mV |

|

|

|

6500 |

|

|

|

6250 |

|

|

6500 |

||||||||||

|

TA = TMIN to TMAX |

|

|

±450 |

|

6750 |

|

|

± 350 |

|

6500 |

|

± 750 |

|

61000 |

µV |

||||||

Output Voltage Swing |

RL = 2 kΩ |

–11 |

|

|

|

+11 |

–11 |

|

|

|

+11 |

–11 |

|

+11 |

V |

|||||||

Output Current |

|

5 |

|

10 |

|

|

|

5 |

|

10 |

|

|

|

5 |

10 |

|

|

|

mA |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FREQUENCY RESPONSE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V/µs |

Slew Rate |

100 mV ≤ 10 VY, VZ, |

|

|

1.4 |

|

|

|

|

|

1.4 |

|

|

|

|

1.4 |

|

|

|

||||

Small Signal Bandwidth |

|

|

400 |

|

|

|

|

|

400 |

|

|

|

|

400 |

|

|

|

kHz |

||||

|

VX ≤ 10 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOLTAGE REFERENCE |

|

|

|

±25 |

|

|

|

|

|

± 15 |

|

|

|

|

± 25 |

|

|

|

|

|||

Accuracy |

VREF = 10 V or 2 V |

|

|

|

650 |

|

|

|

625 |

|

|

650 |

mV |

|||||||||

Additional Error |

TA = TMIN or TMAX |

|

|

±20 |

|

630 |

|

|

± 20 |

|

630 |

|

± 30 |

|

650 |

mV |

||||||

Output Current |

VREF = 10 V to 2 V |

1 |

|

2.5 |

|

|

|

1 |

|

2.5 |

|

|

|

1 |

2.5 |

|

|

|

mA |

|||

Power Supply Rejection |

±4.5 V ≤ VS ≤ ± 18 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

µV/V |

+2 V = VREF |

|

|

300 |

|

600 |

|

|

300 |

|

600 |

|

300 |

|

600 |

||||||||

+10 V = VREF |

±13 V ≤ VS ≤ ±18 V |

|

|

200 |

|

500 |

|

|

200 |

|

500 |

|

200 |

|

500 |

µV/V |

||||||

POWER SUPPLY |

RL = 2 kΩ |

|

|

±15 |

|

|

|

|

|

± 15 |

|

|

|

|

± 15 |

|

|

|

|

|||

Rated |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|||||||

Operating Range3 |

±4.5 V < VS < ±18 V |

64.5 |

|

|

|

618 |

64.5 |

|

|

|

618 |

64.5 |

|

|

618 |

V |

||||||

PSRR |

|

|

0.5 |

|

0.1 |

|

|

0.05 |

|

0.1 |

|

0.5 |

|

0.1 |

%/V |

|||||||

|

VX = VY = VZ = 1 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quiescent Current |

VOUT = 1 V |

|

|

4.5 |

|

7 |

|

|

|

4.5 |

|

7 |

|

4.5 |

|

7 |

|

mA |

||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TEMPERATURE RANGE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

°C |

Rated |

|

–25 |

|

|

|

+85 |

–25 |

|

|

|

+85 |

–55 |

|

+125 |

||||||||

Storage |

|

–65 |

|

|

|

+150 |

–65 |

|

|

|

+150 |

–65 |

|

+150 |

°C |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PACKAGE OPTIONS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ceramic (D-18) |

|

|

|

AD538AD |

|

|

|

|

AD538BD |

|

|

|

AD538SD |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD538SD/883B |

|

||||

Chips |

|

|

|

AD538ACHIPS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES

1Over the 100 mV to 10 V operating range total error is the sum of a percent of reading term and an output offset. With this input dynamic range the input offset contribution to total error is negligible compared to the percent of reading error. Thus, it is specified indirectly as a part of the percent of reading error.

2The most accurate representation of total error with low level inputs is the summation of a percent of reading term, an output offset and an input offset multiplied by the incremental gain (VY + VZ) VX.

3When using supplies below ± 13 V, the 10 V reference pin must be connected to the 2 V pin in order for the AD538 to operate correctly.

Specifications subject to change without notice.

Specifications shown in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

–2– |

REV. C |

AD538

RE-EXAMINATION OF MULTIPLIER/DIVIDER ACCURACY

Traditionally, the “accuracy” (actually the errors) of analog multipliers and dividers have been specified in terms of percent of full scale. Thus specified, a 1% multiplier error with a 10 V full-scale output would mean a worst case error of +100 mV at “any” level within its designated output range. While this type of error specification is easy to test evaluate, and interpret, it can leave the user guessing as to how useful the multiplier actually is at low output levels, those approaching the specified error limit (in this case) 100 mV.

The AD538’s error sources do not follow the percent of fullscale approach to specification, thus it more optimally fits the needs of the very wide dynamic range applications for which it is best suited. Rather than as a percent of full scale, the AD538’s error as a multiplier or divider for a 100:1 (100 mV to 10 V) input range is specified as the sum of two error components: a percent of reading (ideal output) term plus a fixed output offset. Following this format the AD538AD, operating as a multiplier

or divider with inputs down to 100 mV, has a maximum error of

± 1% of reading ± 500 µV. Some sample total error calculations for both grades over the 100:1 input range are illustrated in the chart below. This error specification format is a familiar one to designers and users of digital voltmeters where error is specified as a percent of reading ± a certain number of digits on the meter readout.

For operation as a multiplier or divider over a wider dynamic range (>100:1), the AD538 has a more detailed error specification that is the sum of three components: a percent of reading term, an output offset term and an input offset term for the VY/VX log ratio section. A sample application of this specification, taken from Table I, for the AD538AD with VY = 1 V, VZ = 100 mV and VX = 10 mV would yield a maximum error of

± 2.0% of reading ± 500 µV ± (1 V + 100 mV)/10 mV × 250 µV or ± 2.0% of reading ±500 µV ± 27.5 mV. This example illustrates that with very low level inputs the AD538’s incremental gain (VY + VZ)/VX has increased to make the input offset contribution to error substantial.

Table I. Sample Error Calculation Chart (Worst Case)

|

VY |

VZ |

VX |

Ideal |

Total Offset |

% of Reading |

Total Error |

Total Error Summation |

||||

|

Input |

Input |

Input |

Output |

Error Term |

Error Term |

Summation |

as a % of the Ideal |

||||

|

(in V) |

(in V) |

(in V) |

(in V) |

(in mV) |

(in mV) |

(in mV) |

Output |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

100:1 |

10 |

10 |

10 |

10 |

0.5 |

(AD) |

100 (AD) |

100.5 |

(AD) |

1.0 |

(AD) |

|

INPUT |

|

|

|

|

0.25 |

(BD) |

50 |

(BD) |

50.25 |

(BD) |

0.5 |

(BD) |

RANGE |

|

|

|

|

|

|

|

|

|

|

|

|

Total Error = |

10 |

0.1 |

0.1 |

10 |

0.5 |

(AD) |

100 (AD) |

100.5 |

(AD) |

1.0 |

(AD) |

|

± % rdg |

|

|

|

|

0.25 |

(BD) |

50 |

(BD) |

50.25 |

(BD) |

0.5 |

(BD) |

± Output VOS |

1 |

1 |

1 |

1 |

0.5 |

(AD) |

10 |

(AD) |

10.5 |

(AD) |

1.05 |

(AD) |

|

||||||||||||

|

|

|

|

|

0.25 |

(BD) |

5 |

(BD) |

5.25 |

(BD) |

0.5 |

(BD) |

|

0.1 |

0.1 |

0.1 |

0.1 |

0.5 |

(AD) |

1 |

(AD) |

1.5 |

(AD) |

1.5 |

(AD) |

|

|

|

|

|

0.25 |

(BD) |

0.5 |

(BD) |

0.75 |

(BD) |

0.75 |

(BD) |

|

|

|

|

|

|

|

|

|

|

|

|

|

WIDE |

1 |

0.10 |

0.01 |

10 |

28 |

(AD) |

200 (AD) |

228 |

(AD) |

2.28 |

(AD) |

|

DYNAMIC |

|

|

|

|

16.75 |

(BD) |

100 (BD) |

116.75 (BD) |

1.17 |

(BD) |

||

RANGE |

|

|

|

|

|

|

|

|

|

|

|

|

Total Error = |

10 |

0.05 |

2 |

0.25 |

1.76 |

(AD) |

5 |

(AD) |

6.76 |

(AD) |

2.7 |

(AD) |

± % rdg |

|

|

|

|

1 |

(BD) |

2.5 |

(BD) |

3.5 |

(BD) |

1.4 |

(BD) |

± Output VOS |

|

|

|

|

|

|

|

|

|

|

|

|

± Input VOS × |

5 |

0.01 |

0.01 |

5 |

125.75 (AD) |

100 (AD) |

225.75 (AD) |

4.52 |

(AD) |

|||

(VY + VZ)/VX |

|

|

|

|

75.4 |

(BD) |

50 |

(BD) |

125.4 |

(BD) |

2.51 |

(BD) |

|

10 |

0.01 |

0.1 |

1 |

25.53 |

(AD) |

20 |

(AD) |

45.53 |

(AD) |

4.55 |

(AD) |

|

|

|

|

|

15.27 |

(BD) |

10 |

(BD) |

25.27 |

(BD) |

2.53 |

(BD) |

|

|

|

|

|

|

|

|

|

|

|

|

|

REV. C |

–3– |

AD538

ABSOLUTE MAXIMUM RATINGS

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 18 V Internal Power Dissipation . . . . . . . . . . . . . . . . . . . . 250 mW Output Short Circuit-to-Ground . . . . . . . . . . . . . . . Indefinite

Input Voltages VX, VY, VZ . . . . . . . . . . . . . (+VS – 1 V), –1 V Input Currents IX, IY, IZ, IO . . . . . . . . . . . . . . . . . . . . . . 1 mA Operating Temperature Range . . . . . . . . . . . –25°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C Lead Temperature, Storage . . . . . . . . . . . . . . 60 sec, +300°C Thermal Resistance

θJC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35°C/W θJA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120°C/W

ORDERING GUIDE

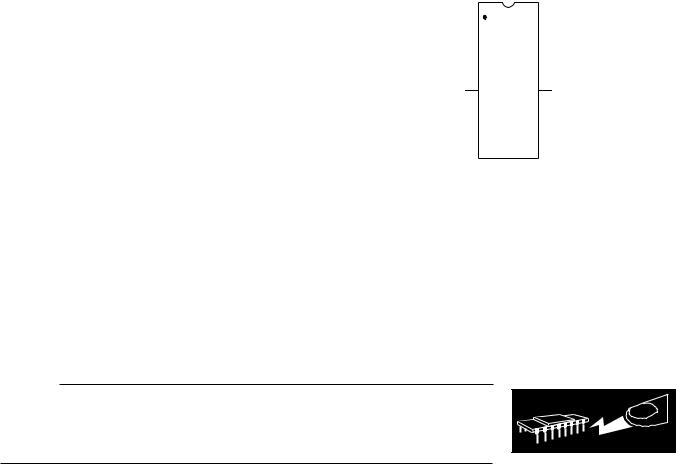

PIN CONFIGURATION

IZ |

|

1 |

|

18 |

|

A |

|

|

|

|

|

|

|

VZ |

|

2 |

|

17 |

|

D |

B |

|

|

|

|

IX |

|

|

3 |

|

16 |

|

||

|

|

|

|

|

|

|

+10V |

|

4 |

AD538 |

15 |

|

VX |

|

|

|

|

|

|

|

+2V |

|

5 |

TOP VIEW |

14 |

|

SIGNAL GND |

+VS |

|

6 |

(Not to Scale) |

13 |

|

PWR GND |

|

|

|

||||

–V |

|

|

|

|

C |

|

|

7 |

|

12 |

|

||

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

VO |

|

8 |

|

11 |

|

IY |

I |

|

|

|

|

VY |

|

|

9 |

|

10 |

|

||

|

Temperature |

Package |

Package |

Model |

Range |

Description |

Option |

|

|

|

|

AD538AD |

–25°C to +85°C |

Side-Brazed Ceramic DIP |

D-18 |

AD538BD |

–25°C to +85°C |

Side-Brazed Ceramic DIP |

D-18 |

AD538ACHIPS |

–25°C to +85°C |

Chips |

|

AD538SD |

–55°C to +125°C |

Side-Brazed Ceramic DIP |

D-18 |

AD538SD/883B |

–55°C to +125°C |

Side-Brazed Ceramic DIP |

D-18 |

|

|

|

|

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD538 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING! |

ESD SENSITIVE DEVICE |

–4– |

REV. C |

Loading...

Loading...