ANALOG DEVICES AD539 Service Manual

FEATURES

2-quadrant multiplication/division

2 independent signal channels Signal bandwidth of 60 MHz (IOUT)

Linear control channel bandwidth of 5 MHz Low distortion (to 0.01%)

Fully calibrated, monolithic circuit

APPLICATIONS

Precise high bandwidth AGC and VCA systems Voltage-controlled filters

Video signal processing High speed analog division Automatic signal-leveling Square-law gain/loss control

Wideband Dual-Channel

Linear Multiplier/Divider

AD539

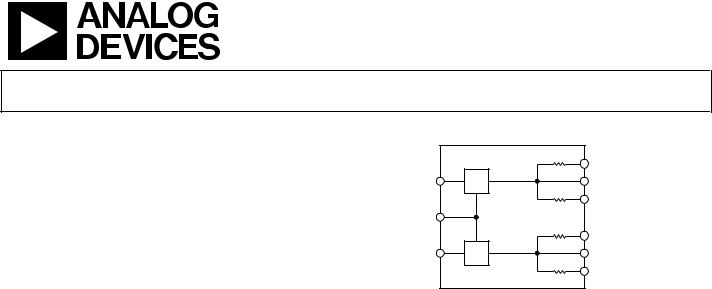

FUNCTIONAL BLOCK DIAGRAM

|

AD539 |

6kΩ |

|

× |

W1 |

VY1 |

CHAN1 OUTPUT |

|

|

6kΩ |

|

|

|

Z1 |

VX |

|

6kΩ |

|

|

|

|

× |

Z2 |

VY2 |

CHAN2 OUTPUT |

|

|

6kΩ |

|

|

|

W2 |

|

|

09679001- |

Figure 1.

GENERAL DESCRIPTION

The AD539 is a low distortion analog multiplier having two identical signal channels (Y1 and Y2), with a common X input providing linear control of gain. Excellent ac characteristics up to video frequencies and a −3 dB bandwidth of over 60 MHz are provided. Although intended primarily for applications where speed is important, the circuit exhibits good static accuracy in computational applications. Scaling is accurately determined by a band-gap voltage reference and all critical parameters are laser-trimmed during manufacture.

The full bandwidth can be realized over most of the gain range using the AD539 with simple resistive loads of up to 100 Ω. Output voltage is restricted to a few hundred millivolts under these conditions.

The two channels provide flexibility. In single-channel applications, they can be used in parallel to double the output current, in series to achieve a square-law gain function with a control range of over 100 dB, or differentially to reduce distortion. Alternatively,

they can be used independently, as in audio stereo applications, with low crosstalk between channels. Voltage-controlled filters and oscillators using the state-variable approach are easily designed, taking advantage of the dual channels and common control. The AD539 can also be configured as a divider with signal bandwidths up to 15 MHz.

Power consumption is only 135 mW using the recommended ±5 V supplies. The AD539 is available in three versions: the J and K grades are specified for 0 to 70°C operation and S grade is guaranteed over the extended range of −55°C to +125°C. The J and K grades are available in either a hermetic ceramic SBDIP (D-16) or a low cost PDIP (N-16), whereas the S grade is available in ceramic SBDIP (D-16) or LCC (E-20-1). The S grade is available in MIL-STD-883 and Standard Military Drawing (DESC) Number 5962-8980901EA versions.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibilityisassumedbyAnalogDevicesforitsuse,norforanyinfringementsofpatentsorother rightsofthirdpartiesthatmayresultfromitsuse.Specificationssubjecttochangewithoutnotice.No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©1983–2011 Analog Devices, Inc. All rights reserved.

AD539

TABLE OF CONTENTS |

|

|

Features .............................................................................................. |

|

1 |

Applications....................................................................................... |

|

1 |

Functional Block Diagram .............................................................. |

|

1 |

General Description ......................................................................... |

|

1 |

Revision History ............................................................................... |

|

2 |

Specifications..................................................................................... |

|

3 |

Pin Configurations and Function Descriptions ........................... |

|

5 |

Typical Performance Characteristics ............................................. |

|

7 |

Theory of Operation ...................................................................... |

|

10 |

Circuit Description..................................................................... |

|

10 |

General Recommendations....................................................... |

|

10 |

REVISION HISTORY |

|

|

4/11—Rev. A to Rev. B |

|

|

Updated Format.................................................................. |

Universal |

|

Changed Pin Configuration to Functional Block Diagram |

........ 1 |

|

Changes to General Description Section ...................................... |

|

1 |

Added Pin Configurations and Function Descriptions |

|

|

Section................................................................................................ |

|

5 |

Added Table 2; Renumbered Sequentially .................................... |

|

5 |

Added Table 3.................................................................................... |

|

6 |

Added Typical Performance Characteristics Section .................. |

|

7 |

Added Figure 6 and Figure 9; Renumbered Sequentially ........... |

7 |

|

Changes to Figure 18...................................................................... |

|

10 |

Transfer Function....................................................................... |

11 |

Dual Signal Channels................................................................. |

11 |

Common Control Channel....................................................... |

11 |

Flexible Scaling ........................................................................... |

11 |

Applications Information .............................................................. |

12 |

Basic Multiplier Connections ................................................... |

12 |

A 50 MHz Voltage-Controlled Amplifier ............................... |

15 |

Basic Divider Connections ....................................................... |

16 |

Outline Dimensions ....................................................................... |

17 |

Ordering Guide .......................................................................... |

18 |

Moved Dual Signal Channels Section, Common Control |

|

Channel Section, and Flexible Scaling Section........................... |

11 |

Changes to Figure 20...................................................................... |

12 |

Changes to Table 4, Figure 21, and Table 5 ................................. |

13 |

Changes to Figure 22 and Figure 23............................................. |

14 |

Changes to Figure 24...................................................................... |

15 |

Changes to Figure 25...................................................................... |

16 |

Updated Outline Dimensions....................................................... |

17 |

Changes to Ordering Guide .......................................................... |

18 |

12/91—Rev. 0 to Rev. A |

|

Rev. B | Page 2 of 20

AD539

SPECIFICATIONS

TA = 25°C, VS = ±5 V, unless otherwise specified. VY = VY1 − VY2, VX = VX1 – VX2. All minimum and maximum specifications are guaranteed.

Table 1.

|

|

|

AD539J |

|

|

AD539K |

|

|

AD539S |

|

|

Parameter |

Test Conditions/Comments |

Min |

Typ |

Max |

Min |

Typ |

Max |

Min |

Typ |

Max |

Unit |

SIGNAL CHANNEL DYNAMICS |

|

|

|

|

|

|

|

|

|

|

|

Minimal Configuration |

See Figure 22 |

|

|

|

|

|

|

|

|

|

|

Bandwidth, −3 dB |

RL = 50 Ω, CC = 0.01 μF |

30 |

60 |

|

30 |

60 |

|

30 |

60 |

|

MHz |

Maximum Output |

0.1 V < VX < 3 V, VY ac = 1 V rms |

|

−10 |

|

|

−10 |

|

|

−10 |

|

dBm |

Feedthrough |

VX = 0 V, VY ac = 1.5 V rms |

|

|

|

|

|

|

|

|

|

|

f < 1 MHz |

|

|

−75 |

|

|

−75 |

|

|

−75 |

|

dBm |

f = 20 MHz |

|

|

−55 |

|

|

−55 |

|

|

−55 |

|

dBm |

Differential Phase Linearity |

|

|

|

|

|

|

|

|

|

|

|

−1 V < VY dc < +1 V |

f = 3.58 MHz, VX = 3 V, |

|

±0.2 |

|

|

±0.2 |

|

|

±0.2 |

|

Degrees |

|

VY ac = 100 mV |

|

|

|

|

|

|

|

|

|

|

−2 V < VY dc < +2 V |

f = 3.58 MHz, VX = 3 V, |

|

±0.5 |

|

|

±0.5 |

|

|

±0.5 |

|

Degrees |

|

VY ac = 100 mV |

|

|

|

|

|

|

|

|

|

|

Group Delay |

VX = 3 V, VY ac = 1 V rms, |

|

4 |

|

|

4 |

|

|

4 |

|

ns |

|

f = 1 MHz |

|

|

|

|

|

|

|

|

|

|

Standard 2-Channel Multiplier |

See Figure 20 |

|

|

|

|

|

|

|

|

|

|

Maximum Output |

VX = 3 V, VY ac = 1.5 V rms |

|

4.5 |

|

|

4.5 |

|

|

4.5 |

|

V |

Feedthrough, f < 100 kHz |

VX = 0 V, VY ac = 1.5 V rms |

|

1 |

|

|

1 |

|

|

1 |

|

mV rms |

Crosstalk (Channel 1 to |

VY1 = 1 V rms, VY2 = 0 V, |

|

−40 |

|

|

−40 |

|

|

−40 |

|

dB |

Channel 2) |

VX = 3 V, f < 100 kHz |

|

|

|

|

|

|

|

|

|

|

RTO Noise, 10 Hz to 1 MHz |

VX = 1.5 V, VY = 0 V |

|

200 |

|

|

200 |

|

|

200 |

|

nV/√Hz |

THD + Noise |

|

|

|

|

|

|

|

|

|

|

|

VX = 1 V |

f = 10 kHz, VY ac = 1 V rms |

|

0.02 |

|

|

0.02 |

|

|

0.02 |

|

% |

VY = 3 V |

f = 10 kHz, VY ac = 1 V rms |

|

0.04 |

|

|

0.04 |

|

|

0.04 |

|

% |

Wideband 2-Channel Multiplier |

See Figure 20 |

|

|

|

|

|

|

|

|

|

|

Bandwidth, −3 dB (LH0032) |

0.1 V < VX < 3 V, |

|

25 |

|

|

25 |

|

|

25 |

|

MHz |

|

VY ac = 1 V rms |

|

|

|

|

|

|

|

|

|

|

Maximum Output VX = 3 V |

VY ac = 1.5 V rms, f = 3 MHz |

|

4.5 |

|

|

4.5 |

|

|

4.5 |

|

V rms |

Feedthrough VX = 0 V |

VY ac = 1.0 V rms, f = 3 MHz |

|

14 |

|

|

14 |

|

|

14 |

|

mV rms |

Wideband Single-Channel VCA |

See Figure 24 |

|

|

|

|

|

|

|

|

|

|

Bandwidth, −3 dB |

0.1 V < VX < 3 V, |

|

50 |

|

|

50 |

|

|

50 |

|

MHz |

|

VY ac = 1 V rms |

|

|

|

|

|

|

|

|

|

|

Maximum Output |

75 Ω load |

|

±1 |

|

|

±1 |

|

|

±1 |

|

V |

Feedthrough |

VX = −0.01 V, f = 5 MHz |

|

−54 |

|

|

−54 |

|

|

−54 |

|

dB |

|

|

|

|

|

|

|

|

|

|

|

|

CONTROL CHANNEL DYNAMICS |

|

|

|

|

|

|

|

|

|

|

|

Bandwidth, −3 dB |

CC = 3000 pF, VX dc = 1.5 V, |

|

5 |

|

|

5 |

|

|

5 |

|

MHz |

|

VX ac = 100 mV rms |

|

|

|

|

|

|

|

|

|

|

SIGNAL INPUTS, VY1 AND VY2 |

|

|

|

|

|

|

|

|

|

|

|

Nominal Full-Scale Input |

|

|

±2 |

|

|

±2 |

|

|

±2 |

|

V |

Operational Range, Degraded |

−VS ≤ 7 V |

±4.21 |

|

|

±4.21 |

|

|

±4.21 |

|

|

V |

Performance |

|

|

|

|

|

|

|

|

|

|

|

Input Resistance |

|

|

400 |

|

|

400 |

|

|

400 |

|

kΩ |

Bias Current |

|

|

10 |

301 |

|

10 |

201 |

|

10 |

301 |

μA |

Offset Voltage |

VX = 3 V, VY = 0 V |

|

5 |

201 |

|

5 |

101 |

|

5 |

201 |

mV |

TMIN to TMAX |

|

|

10 |

|

|

5 |

|

|

15 |

35 |

mV |

Power Supply Sensitivity |

VX = 3 V, VY = 0 V |

|

2 |

|

|

2 |

|

|

2 |

|

mV/V |

|

|

|

|

|

|

|

|

|

|

|

|

Rev. B | Page 3 of 20

AD539

|

|

|

AD539J |

|

|

AD539K |

|

|

AD539S |

|

|

Parameter |

Test Conditions/Comments |

Min |

Typ |

Max |

Min |

Typ |

Max |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

CONTROL INPUT, VX |

|

|

|

|

|

|

|

|

|

|

|

Nominal Full-Scale Input |

|

|

3.0 |

|

|

3.0 |

|

|

3.0 |

|

V |

Operational Range, Degraded |

|

+3.2 |

|

|

+3.2 |

|

|

+3.2 |

|

|

V |

Performance |

|

|

|

|

|

|

|

|

|

|

|

Input Resistance2 |

|

|

500 |

|

|

500 |

|

|

500 |

|

Ω |

Offset Voltage |

|

|

1 |

41 |

|

1 |

21 |

|

1 |

41 |

mV |

TMIN to TMAX |

|

|

3 |

|

|

2 |

|

|

2 |

51 |

mV |

Power Supply Sensitivity |

|

|

30 |

|

|

30 |

|

|

30 |

|

μV/V |

|

|

|

|

|

|

|

|

|

|

|

|

Gain |

See Figure 20 |

|

|

|

|

|

|

|

|

|

|

Absolute Gain Error |

VX = 0.1 V to 3.0 V, VY = ±2 V |

|

0.2 |

0.41 |

|

0.1 |

0.21 |

|

0.2 |

0.41 |

dB |

TMIN to TMAX |

VX = 0.1 V to 3.0 V, VY = ±2 V |

|

0.3 |

|

|

0.15 |

|

|

0.25 |

0.51 |

dB |

CURRENT OUTPUT2 |

|

|

|

|

|

|

|

|

|

|

|

Full-Scale Output Current |

VX = 3 V, VY = ±2 V |

|

±1 |

|

|

±1 |

|

|

±1 |

|

mA |

Peak Output Current |

VX = 3.3 V, VY = ±5 V, |

±2 |

±2.8 |

|

±2 |

±2.8 |

|

±2 |

±2.8 |

|

mA |

|

VS = ±7.5 V |

|

|

|

|

|

|

|

|

|

|

Output Offset Current |

VX = 0 V, VY = 0 V |

|

0.2 |

1.51 |

|

0.2 |

1.51 |

|

0.2 |

1.51 |

μA |

Output Offset Voltage3 |

See Figure 20, VX = 0 V, |

|

3 |

101 |

|

3 |

101 |

|

3 |

101 |

mV |

|

VY = 0 V |

|

|

|

|

|

|

|

|

|

|

Output Resistance |

|

|

1.2 |

|

|

1.2 |

|

|

1.2 |

|

kΩ |

Scaling Resistors |

|

|

|

|

|

|

|

|

|

|

|

Channel 1 |

Z1, W1 to CH1 |

|

6 |

|

|

6 |

|

|

6 |

|

kΩ |

Channel 2 |

Z2, W2 to CH2 |

|

6 |

|

|

6 |

|

|

6 |

|

kΩ |

|

|

|

|

|

|

|

|

|

|

|

|

VOLTAGE OUTPUTS, VW1 AND VW23 |

See Figure 20 |

|

|

|

|

|

|

|

|

|

|

Multiplier Transfer Function |

|

|

|

|

|

|

|

|

|

|

|

Either Channel |

|

VW = −VX × VY/VU |

VW = −VX × VY/VU |

VW = −VX × VY/VU |

|

||||||

Multiplier Scaling Voltage, VU |

|

0.981 |

1.0 |

1.021 |

0.991 |

1.0 |

1.011 |

0.981 |

1.0 |

1.021 |

V |

Accuracy |

|

|

0.5 |

21 |

|

0.5 |

11 |

|

0.5 |

2 |

% |

TMIN to TMAX |

|

|

1 |

|

|

0.5 |

|

|

1.0 |

31 |

% |

Power Supply Sensitivity |

|

|

0.04 |

|

|

0.04 |

|

|

0.04 |

|

%/V |

Total Multiplication Error4 |

VX ≤ 3 V, −2 V < VY < +2 V |

|

1 |

2.5 |

|

0.6 |

1.5 |

|

1 |

2.5 |

% FSR |

TMIN to TMAX |

|

|

2 |

|

|

1 |

|

|

2 |

41 |

% |

Control Feedthrough |

VX = 0 V to 3 V, VY = 0 V |

|

25 |

601 |

|

15 |

301 |

|

15 |

601 |

mV |

TMIN to TMAX |

|

|

30 |

|

|

15 |

|

|

60 |

1201 |

mV |

TEMPERATURE RANGE |

|

|

|

|

|

|

|

|

|

|

|

Rated Performance |

|

0 |

|

+70 |

0 |

|

+70 |

−55 |

|

+125 |

°C |

|

|

|

|

|

|

|

|

|

|

|

|

POWER SUPPLIES |

|

|

|

|

|

|

|

|

|

|

|

Operational Range |

|

±4.5 |

|

±15 |

±4.5 |

|

±15 |

±4.5 |

|

±15 |

V |

Current Consumption |

|

|

|

|

|

|

|

|

|

|

|

+VS |

|

|

8.5 |

10.21 |

|

8.5 |

10.21 |

|

8.5 |

10.21 |

mA |

−VS |

|

|

18.5 |

22.21 |

|

18.5 |

22.21 |

|

18.5 |

22.21 |

mA |

1 Tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. 2 Resistance value and absolute current outputs subject to 20% tolerance.

3 Specification assumes the external op amp is trimmed for negligible input offset. 4 Includes all errors.

Rev. B | Page 4 of 20

AD539

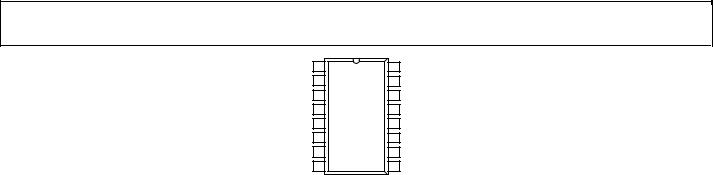

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

|

COMP |

|

NC |

W1 |

Z1 |

|

|

|

HF V |

|

|

||||

|

|

X |

|

|

|

|

|

|

3 |

2 |

1 |

20 |

19 |

|

|

VY1 4 |

|

|

|

|

|

18 |

CHAN1 OUTPUT |

+VS 5 |

|

AD539 |

|

17 |

BASE COMMON |

||

NC 6 |

|

TOP VIEW |

|

16 |

NC |

||

–VS 7 |

(Not to Scale) |

15 BASE COMMON |

|||||

VY2 8 |

|

|

|

|

|

14 |

CHAN2 OUTPUT |

|

9 |

10 |

11 |

12 |

13 |

|

|

|

COMMON |

COMMON |

NCNOTESW2 Z2 |

|

|

||

|

INPUT |

OUTPUT |

|

1. NC = NO CONNECT. DO NOT |

|||

|

|

CONNECT TO THIS PIN. |

|||||

|

|

|

|

||||

09679-002

|

|

Figure 2. 20-Lead LLC Pin Configuration (E-20-1) |

Table 2. 20-Lead LLC Pin Function Descriptions |

||

Pin No. |

Mnemonic |

Description |

1 |

NC |

No Connect. Do not connect to this pin. |

2 |

VX |

Control Channel Input. |

3 |

HF COMP |

High Frequency Compensation. |

4 |

VY1 |

Channel 1 Input. |

5 |

+VS |

Positive Supply Rail. |

6 |

NC |

No Connect. Do not connect to this pin. |

7 |

–VS |

Negative Supply Rail. |

8 |

VY2 |

Channel 2 Input. |

9 |

INPUT COMMON |

Internal Common Connection for the Input Amplifier Circuitry. |

10 |

OUTPUT COMMON |

Internal Common Connection for the Output Amplifier Circuitry. |

11 |

NC |

No Connect. |

12 |

W2 |

6 kΩ Feedback Resistor for Channel 2. |

13 |

Z2 |

6 kΩ Feedback Resistor for Channel 2. |

14 |

CHAN2 OUTPUT |

Channel 2 Product of VX and VY2. |

15 |

BASE COMMON |

Increases Negative Output Compliance. |

16 |

NC |

No Connect. Do not connect to this pin. |

17 |

BASE COMMON |

Increases Negative Output Compliance. |

18 |

CHAN1 OUTPUT |

Channel 1 Product of VX and VY1. |

19 |

Z1 |

6 kΩ Feedback Resistor for Channel 1. |

20 |

W1 |

6 kΩ Feedback Resistor for Channel 1. |

|

|

|

Rev. B | Page 5 of 20

AD539

VX |

1 |

|

16 |

W1 |

|

HF COMP |

2 |

|

15 |

Z1 |

|

VY1 |

3 |

AD539 |

14 |

CHAN1 OUTPUT |

|

+VS |

4 |

TOP VIEW |

13 |

BASE COMMON |

|

–VS |

5 |

(Not to Scale) |

12 |

BASE COMMON |

|

VY2 |

6 |

|

11 |

CHAN2 PUTPUT |

|

INPUT COMMON |

7 |

|

10 |

Z2 |

09679-003 |

OUTPUT COMMON |

8 |

|

9 |

W2 |

|

|

|

|

|

|

Figure 3. 16-Lead PDIP and SBDIP Pin Configurations (N-16, D-16)

Table 3. 16-Lead PDIP and SBDIP Pin Function Descriptions

Pin No. |

Mnemonic |

Description |

1 |

VX |

Control Channel Input. |

2 |

HF COMP |

High Frequency Compensation. |

3 |

VY1 |

Channel 1 Input. |

4 |

+VS |

Positive Supply Rail. |

5 |

–VS |

Negative Supply Rail. |

6 |

VY2 |

Channel 2 Input. |

7 |

INPUT COMMON |

Internal Common Connection for the Input Amplifier Circuitry. |

8 |

OUTPUT COMMON |

Internal Common Connection for The Output Amplifier Circuitry. |

9 |

W2 |

6 kΩ Feedback Resistor for Channel 2. |

10 |

Z2 |

6 kΩ Feedback Resistor for Channel 2. |

11 |

CHAN2 OUTPUT |

Channel 2 Product of VX and VY2. |

12 |

BASE COMMON |

Increases Negative Output Compliance. |

13 |

BASE COMMON |

Increases Negative Output Compliance. |

14 |

CHAN1 OUTPUT |

Channel 1 Product of VX and VY1. |

15 |

Z1 |

6 kΩ Feedback Resistor for Channel 1. |

16 |

W1 |

6 kΩ Feedback Resistor for Channel 1. |

|

|

|

Rev. B | Page 6 of 20

Loading...

Loading...