ANALOG DEVICES AD5582, AD5583 Service Manual

a 12-Quad,/10-BitParallelDigital-Input,to-AnalogVoltageConvertersOutput,

AD5582/AD5583

FEATURES

12-Bit Linearity and Monotonic AD5582

10-Bit Linearity and Monotonic AD5583 Wide Operating Range: Single 5 V to 15 V or

Dual 5 V Supply

Unipolar or Bipolar Operation

Double Buffered Registers Enable Independent or Simultaneous Multichannel Update

4Independent Rail-to-Rail Reference Inputs

20mA High Current Output Drive Parallel Interface

Data Readback Capability

5s Settling Time

Built-In Matching Resistor Simplifies Negative Reference

Unconditionally Stable Under Any Capacitive Loading Compact Footprint: TSSOP-48

Extended Temperature Range: 40 C to 125 C

APPLICATIONS

Process Control Equipment Closed-Loop Servo Control Data Acquisition Systems Digitally Controlled Calibration Optical Network Control Loops

4 m to 20 mA Current Transmitter

GENERAL DESCRIPTION

The AD5582/AD5583 family of quad, 12-/10-bit, voltage output digital-to-analog converters is designed to operate from a single 5 V to 15 V or dual ±5 V supply. It offers the user ease of use in singleor dual-supply systems. Built using an advance BiCMOS process, this high performance DAC is dynamically stable, capable of high current drive, and in small form factor.

The applied external reference VREF determines the full-scale output voltage ranges from VSS to VDD, resulting in a wide selection of full-scale outputs. For multiplying and wide dynamic applications, ac reference inputs can be as high as |VDD – VSS|. Two built-in precision trimmed resistors are available and can be configured easily to provide four-quadrant multiplications.

Adoubled-buffered parallel interface offers a fast settling time.

Acommon level sensitive load DAC strobe (LDAC) input allows

additional simultaneous update of all DAC outputs. An external asynchronous reset (RS) forces all registers to the zero code state when the MSB = 0 or to midscale when the MSB = 1.

Both parts are offered in the same pinout and package to allow users to select the appropriate resolution for a given application without PCB layout changes.

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

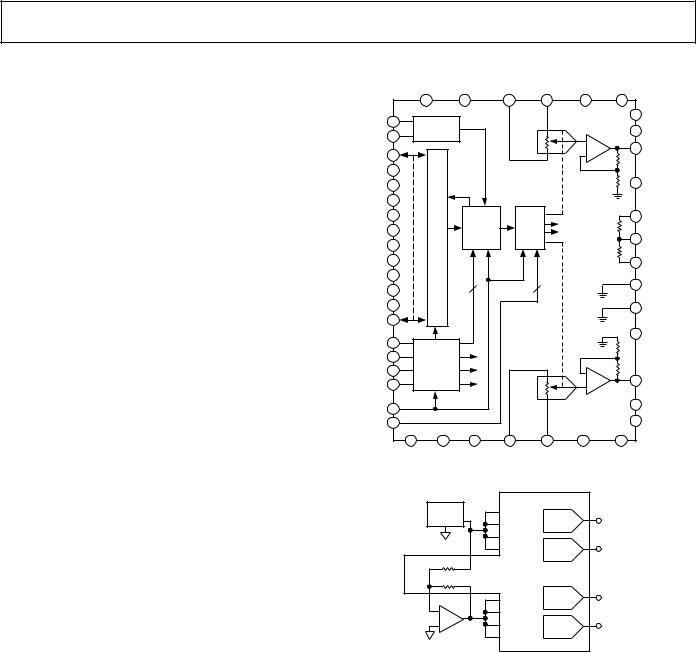

AD5582 FUNCTIONAL BLOCK DIAGRAM

|

|

VDD3 |

VSS3 |

VREFLA |

VREFHA |

VREFLB |

VREFHB |

|

|

|

|

38 |

37 |

10 |

|

9 |

7 |

8 |

|

A1 |

|

ADDR |

|

|

|

|

|

3 |

VDD1 |

33 |

|

|

|

|

AD5582 |

VSS1 |

|||

A0 |

32 |

DECODE |

|

|

|

|

|

4 |

|

|

|

|

|

|

+ |

|

|

||

|

|

|

|

|

|

|

5 |

VOA |

|

DB11 |

31 |

|

|

|

|

|

– |

||

|

|

|

|

|

|

|

|||

DB10 |

30 |

|

|

|

|

|

|

|

|

DB9 |

29 |

|

|

|

|

|

|

2 |

VOB |

|

|

|

|

|

|

|

|

||

DB8 |

28 |

I |

|

|

|

|

|

|

|

DB7 |

26 |

N |

DO |

|

|

|

|

11 |

R1 |

T |

IN |

DAC |

|

||||||

DB6 |

|

E |

|

20k |

|

||||

25 |

R |

REG |

REG |

|

|

|

|||

DB5 |

24 |

F |

DI |

|

|

|

|

12 |

RCT |

A |

|

|

|

|

20k |

|

|||

|

|

|

|

|

|

|

|||

DB4 |

23 |

C |

|

|

|

|

|

||

|

|

|

|

|

13 |

R2 |

|||

E |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

DB3 |

21 |

|

|

|

|

|

|

|

AGND1 |

DB2 |

20 |

|

4 |

|

|

4 |

|

1 |

|

|

|

|

|

|

|

||||

DB1 |

19 |

|

|

|

|

|

|

48 |

AGND2 |

|

|

|

|

|

|

|

|

||

DB0 |

18 |

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

47 |

VOC |

CS |

34 |

|

|

|

|

|

|

|

|

R/W 35 |

CONTROL |

|

|

|

|

|

|

|

|

DVDD |

14 |

LOGIC |

|

|

|

|

– |

|

|

|

|

|

|

|

44 |

VOD |

|||

MSB |

17 |

|

|

|

|

|

+ |

||

|

|

|

|

|

|

|

|||

RS |

16 |

|

|

|

|

|

|

46 |

VDD2 |

LDAC |

15 |

|

|

|

|

|

|

45 |

VSS2 |

|

22 |

27 |

36 |

40 |

|

39 |

41 |

42 |

|

|

DGND1 DGND2 DGND3 |

VREFHD |

VREFLD |

VREFHC |

VREFLC |

|

|||

2.5V |

AD5582/AD5583 |

|

|

ADR421 |

VREFHA |

|

|

REF |

2.5V |

||

DAC A |

|||

|

VREFHB |

|

|

|

VREFHC |

|

|

|

VREFHD DAC B |

2.5V |

|

R1 |

|

|

|

RCT |

R2 |

|

|

|

|

|

VREFLA |

DAC C |

2.5V |

|

– |

|

|

|

|

VREFLB |

|

|

|

|

+ |

VREFLC |

DAC D |

2.5V |

|

|

2.5V |

|

|

|

|

VREFLD |

|

|

DIGITAL CIRCUITRY OMITTED FOR CLARITY

Figure 1. Using Built-In Matching Resistors to Generate a Negative Voltage Reference

The AD5582 is well suited for DAC8412 replacement in medium voltage applications in new designs, as well as any other general purpose multichannel 10to 12-bit applications.

The AD5582/AD5583 are specified over the extended industrial (–40∞C to +125∞C) temperature range and offered in a thin and compact 1.1 mm TSSOP-48 package.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

AD5582/AD5583–SPECIFICATIONS

ELECTRICAL CHARACTERISTICS |

(VDD = +5 V, VSS = –5 V, DVDD = +5 V 10%, VREFH = +2.5 V, VREFL = –2.5 V, |

|

|||||

–40 C < TA < +125 C, unless otherwise noted.) |

|

|

|

||||

|

|

|

|

|

|

|

|

Parameter |

Symbol |

Condition |

Min |

Typ1 |

Max |

Unit |

|

STATIC PERFORMANCE |

|

|

|

|

|

|

|

Resolution2 |

N |

AD5582 |

|

12 |

|

Bits |

|

Relative Accuracy3 |

|

AD5583 |

|

10 |

|

Bits |

|

INL |

|

|

–1 |

|

+1 |

LSB |

|

Differential Nonlinearity3 |

DNL |

Monotonic |

–1 |

|

|

LSB |

|

Zero-Scale Error |

VZSE |

Data = 000H for AD5582 |

–2 |

|

+2 |

LSB |

|

|

|

and AD5583 |

|

|

|

|

|

Gain Error |

VGE |

Data = 0xFFFH for AD5582 |

–2 |

|

+2 |

LSB |

|

|

VGE |

Data = 0x3FFH for AD5583 |

–4 |

|

+4 |

LSB |

|

Gain Error |

VGE |

VDD = 2.7 V to 4.5 V |

–4 |

|

+4 |

LSB |

|

Full-Scale Tempco4 |

TCVFS |

|

|

|

1.5 |

|

ppm/∞C |

REFERENCE INPUT |

|

|

|

|

|

|

|

VREFH Input Range |

VREFH |

|

|

VREFL + 0.5 |

|

VDD |

V |

VREFL Input Range5 |

VREFL |

|

|

VSS |

|

VREFH – 0.5 |

V |

Input Resistance |

RREF |

Data = 555H (Minimum RREF) |

12 |

20 |

|

kΩ1 |

|

Input Capacitance4 |

CREF |

for AD5582 and 155H for AD5583 |

|

80 |

|

pF |

|

|

|

|

|

||||

REF Input Current |

IREF |

Data = 555H for AD5582 |

|

|

500 |

μA |

|

REF Multiplying Bandwidth |

BWREF |

Code = Full Scale |

|

|

1.3 |

MHz |

|

R1–R2 Matching |

R1/R2 |

AD5582 |

|

|

±0.025 |

% |

|

|

|

AD5583 |

|

|

±0.100 |

% |

|

ANALOG OUTPUT |

|

|

|

|

|

±2 |

|

Output Current6 |

IOUT |

Data = 800H for AD5582 and |

|

|

mA |

||

Output Current6 |

|

200H for AD5583, VOUT ≤ 2 mV |

|

|

|

|

|

IOUT |

Data = 800H for AD5582 and |

|

|

|

|

||

|

|

200H for AD5583, VOUT ≤ |–8 mV| |

|

|

+20 |

mA |

|

Capacitive Load4, 7 |

|

VOUT ≤ ±15 mV |

|

|

–20 |

mA |

|

CL |

No Oscillation |

|

Note 7 |

|

pF |

||

LOGIC INPUTS |

|

DVDD = 5 V ± 10% |

|

|

|

|

|

Logic Input Low Voltage |

VIL |

|

|

0.8 |

V |

||

|

|

DVDD = 3 V ± 10% |

|

|

0.4 |

V |

|

Logic Input High Voltage |

VIH |

DVDD = 5 V ± 10% |

2.4 |

|

|

V |

|

|

|

DVDD = 3 V ± 10% |

2.1 |

|

|

V |

|

Input Leakage Current |

IIL |

|

|

|

0.01 |

1 |

μA |

Input Capacitance4 |

CIL |

|

|

|

5 |

|

pF |

Output Voltage High |

VOH |

IOH = –0.8 mA |

2.4 |

|

|

V |

|

Output Voltage Low |

VOL |

IOL = 1.2 mA, TA = 85∞C, |

|

|

0.4 |

V |

|

|

|

IOL = 0.6 mA, DVDD = 3 V |

|

|

|

|

|

|

|

IOL = 1.0 mA, TA = 125∞C, |

|

|

0.4 |

V |

|

|

|

IOL = 0.5 mA, DVDD = 3 V |

|

|

|

|

|

AC CHARACTERISTICS |

|

|

|

|

|

|

V/μs |

Output Slew Rate |

SR |

Data = Zero Scale to Full Scale |

|

2 |

|

||

|

|

to Zero Scale |

|

|

|

|

|

Settling Time8 |

tS |

To ±0.1% of Full Scale |

|

5 |

|

μs |

|

DAC Glitch |

Q |

Code 7FFH to 800H to 7FFH |

|

100 |

|

nV-s |

|

|

|

for AD5582 and 1FFH to 200H |

|

|

|

|

|

Digital Feedthrough |

VOUT/tCS |

to 1FFH for AD5583 |

|

|

|

|

|

Data = Midscale, CS Toggles at |

|

5 |

|

nV-s |

|||

|

|

f = 16 MHz |

|

|

|

|

|

Analog Crosstalk |

VOUT/VREF |

VREF = 1.5 V dc + 1 V p-p, |

|

–80 |

|

dB |

|

|

|

Data = 000H, f = 100 kHz |

|

|

|

nV/ Hz |

|

Output Noise |

eN |

f = 1 kHz |

|

33 |

|

||

–2– |

REV. A |

AD5582/AD5583

Parameter |

Symbol |

Condition |

Min |

Typ1 |

Max |

Unit |

SUPPLY CHARACTERISTICS |

|

|

|

|

|

|

Single-Supply Voltage Range |

VDD |

VSS = 0 V |

3 |

|

18 |

V |

Dual-Supply Voltage Range |

VDD/VSS |

VDD = +2.7 V to +6.5 V, |

–9 |

|

+9 |

V |

Digital Logic Supply |

DVDD |

VSS = –6.5 V to –2.7 V |

2.7 |

|

8 |

V |

|

|

|||||

Positive Supply Current6 |

IDD |

VIL = 0 V, No Load |

|

1.7 |

3 |

mA |

Negative Supply Current |

ISS |

VIL = 0 V, No Load |

|

1.5 |

3 |

mA |

Power Dissipation |

PDISS |

VIL = 0 V, No Load |

|

16 |

30 |

mW |

Power Supply Sensitivity |

PSS |

VDD = ±5% |

|

30 |

|

ppm/V |

NOTES

1Typical specifications represent average readings measured at 25∞C.

2DAC Output Equation: VOUT = VREFL + [(VREFH – VREFL) D/2N], where D = data loaded in corresponding DAC Register A, B, C, D, and N equals the number of bits; AD5582 = 12 bits, AD5583 = 10 bits. One LSB step voltage = (VREFH – VREFL)/4096 V and (VREFH – VREFL)/1024 V for AD5582 and AD5583, respectively.

3The first two codes (000H, 001H) of the AD5583 and the first four codes (000H, 001H, 002H, 003H) of the AD5582 are excluded from the linearity error measurement in single-supply operation.

4These parameters are guaranteed by design and not subject to production testing.

5Dual-supply operation, VREFL = VSS, exclude the lowest eight codes for the AD5582 and two codes for the AD5583 for INL and DNL errors. 6Short circuit output and supply currents are 24 mA and 25 mA, respectively.

7Part is stable under any capacitive loading conditions.

8The settling time specification does not apply for negative-going transitions within the last 3 LSBs of ground in single-supply operation.

Specifications subject to change without notice.

|

|

(VDD = 15 V, VSS = 0 V, DVDD = 5 V 10%, VREFH = 10 V, VREFL = 0 V, |

|

||

ELECTRICAL CHARACTERISTICS –40 C < TA < +125 C, unless otherwise noted.) |

|

|

|||

Parameter |

Symbol |

Condition |

Min |

Typ1 Max |

Unit |

STATIC PERFORMANCE |

|

|

|

|

|

Resolution2 |

N |

AD5582 |

|

12 |

Bits |

Relative Accuracy3 |

|

AD5583 |

|

10 |

Bits |

INL |

|

–1 |

+1 |

LSB |

|

Differential Nonlinearity3 |

DNL |

Monotonic |

–1 |

|

LSB |

Zero-Scale Error |

VZSE |

Data = 000H for AD5582 |

–2 |

+2 |

LSB |

|

|

and AD5583 |

|

|

|

Gain Error |

VGE |

Data = 0xFFFH for AD5582 |

–2 |

+2 |

LSB |

|

VGE |

Data = 0x3FFH for AD5583 |

–4 |

+4 |

LSB |

Full-Scale Tempco4 |

TCVFS |

|

|

1.5 |

ppm/∞C |

REFERENCE INPUT |

|

|

|

|

|

VREFH Input Range |

VREFH |

|

VREFL + 0.5 |

VDD |

V |

VREFL Input Range5 |

VREFL |

|

VSS |

VREFH – 0.5 |

V |

Input Resistance |

RREF |

Data = 555H (Minimum RREF) |

12 |

20 |

kΩ1 |

Input Capacitance4 |

CREF |

for AD5582 and 155H for AD5583 |

|

80 |

pF |

|

|

||||

REF Input Current |

IREF |

Data = 555H for AD5582 |

|

1000 |

μA |

REF Multiplying Bandwidth |

BWREF |

Code = Full Scale |

|

1.3 |

MHz |

R1–R2 Matching |

R1/R2 |

AD5582 |

|

±0.025 |

% |

|

|

AD5583 |

|

±0.100 |

% |

ANALOG OUTPUT |

|

|

|

|

|

Output Current6 |

IOUT |

Data = 800H for AD5582 and |

|

2 |

mA |

Output Current6 |

|

200H for AD5583, VOUT ≤ 2 mV |

|

|

|

IOUT |

Data = 800H for AD5582 and |

|

|

|

|

|

|

200H for AD5583, VOUT ≤ |–8 mV| |

|

+20 |

mA |

Capacitive Load4, 7 |

|

VOUT ≤ 15 mV |

|

–20 |

mA |

CL |

No Oscillation |

|

Note 7 |

pF |

|

REV. A |

–3– |

AD5582/AD5583

ELECTRICAL CHARACTERISTICS (continued)

Parameter |

Symbol |

Condition |

Min |

Typ1 |

Max |

Unit |

LOGIC INPUTS/OUTPUTS |

|

|

|

|

|

|

Logic Input Low Voltage |

VIL |

DVDD = 3 V ± 10% |

|

|

0.8 |

V |

|

|

|

|

0.4 |

V |

|

Logic Input High Voltage |

VIH |

DVDD = 3 V ± 10% |

2.4 |

|

|

V |

|

|

2.1 |

|

|

V |

|

Input Leakage Current |

IIL |

|

|

|

|

μA |

Input Capacitance4 |

CIL |

|

|

|

|

pF |

Output Voltage High |

VOH |

IOH = –0.8 mA |

2.4 |

|

|

V |

Output Voltage Low |

VOL |

IOL = 1.2 mA, TA = 85 C, |

|

|

0.4 |

V |

|

|

IOL = 0.6 mA, DVDD = 3 V |

|

|

|

|

|

VOL |

IOL = 1.0 mA, TA = 125 C, |

|

|

0.4 |

V |

|

|

IOL = 0.5 mA, DVDD = 3 V |

|

|

|

|

AC CHARACTERISTICS |

|

|

|

|

|

V/μs |

Output Slew Rate |

SR |

Data = Zero Scale to Full Scale |

|

2 |

|

|

|

|

to Zero Scale |

|

|

|

|

Settling Time8 |

tS |

To ±0.1% of Full Scale |

|

14 |

|

μs |

DAC Glitch |

Q |

Code 7FFH to 800H to 7FFH for |

|

100 |

|

nV-s |

|

|

AD5582 and 1FFH to 200H to |

|

|

|

|

Digital Feedthrough |

VOUT/tCS |

1FFH for AD5583 |

|

|

|

|

Data = Midscale, CS Toggles at |

|

5 |

|

nV-s |

||

|

|

f = 16 MHz |

|

|

|

|

Analog Crosstalk |

VOUT/VREF |

VREF = 1.5 V dc + 1 V p-p, |

|

–80 |

|

dB |

|

|

Data = 000H, f = 100 kHz |

|

|

|

nV/ Hz |

Output Noise |

eN |

f = 1 kHz |

|

33 |

|

|

SUPPLY CHARACTERISTICS |

|

|

|

|

|

|

Single-Supply Voltage Range |

VDD |

VSS = 0 V |

3 |

|

16.5 |

V |

Dual-Supply Voltage Range |

VDD/VSS |

VDD = +2.7 V to +6.5 V, |

–6.5 |

|

+6.5 |

V |

Digital Logic Supply |

DVDD |

VSS = –6.5 V to –2.7 V |

2.7 |

|

6.5 |

V |

|

|

|||||

Positive Supply Current6 |

IDD |

VIL = 0 V, No Load |

|

2.3 |

3.5 |

mA |

Power Dissipation |

PDISS |

VIL = 0 V, No Load |

|

34.5 |

52.5 |

mW |

Power Supply Sensitivity |

PSS |

VDD = ±5% |

|

30 |

|

ppm/V |

NOTES

1Typical specifications represent average readings measured at 25∞C.

2DAC Output Equation: VOUT = VREFL + [(VREFH – VREFL) D/2N], where D = data in decimal loaded in corresponding DAC Register A, B, C, D, and N equals the number of bits; AD5582 = 12 bits, AD5583 = 10 bits. One LSB step voltage = (VREFH – VREFL)/4096 V and = (VREFH – VREFL)/1024 V for AD5582 and AD5583, respectively.

3The first two codes (000H, 001H) of the AD5583 and the first four codes (000H, 001H, 002H, 003H) of the AD5582 are excluded from the linearity error measurement in single-supply operation.

4These parameters are guaranteed by design and not subject to production testing.

5Dual-supply operation, VREFL = VSS, exclude the lowest eight codes for the AD5582 and two codes for the AD5583 for INL and DNL errors. 6Short circuit output and supply currents are 24 mA and 25 mA, respectively.

7Part is stable under any capacitive loading conditions.

8The settling time specification does not apply for negative-going transitions within the last 3 LSBs of ground in single-supply operation.

Specifications subject to change without notice.

–4– |

REV. A |

AD5582/AD5583

TIMING CHARACTERISTICS |

(VDD = 15 V or 5 V, VSS = 0 V, DVDD = 5 V 10%, VREFH = 10 V, VREFL = 0 V, –40 C < TA < +125 C, |

|||||||

unless otherwise noted.) |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

|

Condition |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

INTERFACE TIMING* |

|

|

|

|

|

|

|

|

Chip Select Write Pulse Width |

|

tWCS |

|

|

20 |

|

|

ns |

Chip Select Read Pulse Width |

|

tRCS |

|

|

130 |

|

|

ns |

Write Setup |

|

tWS |

|

|

35 |

|

|

ns |

Write Hold |

|

tWH |

|

|

0 |

|

|

ns |

Address Setup |

|

tAS |

|

|

35 |

|

|

ns |

Address Hold |

|

tAH |

|

|

0 |

|

|

ns |

Load Setup |

|

tLS |

|

|

0 |

|

|

ns |

Load Hold |

|

tLH |

|

|

0 |

|

|

ns |

Write Data Setup |

|

tWDS |

|

|

35 |

|

|

ns |

Write Data Hold |

|

tWDH |

|

|

0 |

|

|

ns |

Load Data Pulse Width |

|

tLDW |

|

|

20 |

|

|

ns |

Reset Pulse Width |

|

tRESET |

|

|

20 |

|

|

ns |

Read Data Hold |

|

tRDH |

|

|

0 |

|

|

ns |

Read Data Setup |

|

tRDS |

|

|

0 |

|

|

ns |

Data to Hi-Z |

|

tDZ |

|

CL = 10 pF |

|

|

100 |

ns |

Chip Select to Data |

|

tCSD |

|

CL = 10 pF |

|

|

100 |

ns |

Chip Select Repetitive Pulse Width |

|

tCSP |

|

|

10 |

|

|

ns |

Load Setup in Double Buffer Mode |

|

tLDS |

|

|

20 |

|

|

ns |

Load Data Hold |

|

tLDH |

|

|

0 |

|

|

ns |

*All input control signals are specified with tR = tF = 2 ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. Specifications subject to change without notice.

TIMING CHARACTERISTICS |

(VDD = 15 V or 5 V, VSS = 0 V, DVDD = 3 V 10%, VREFH = 10 V, VREFL = 0 V, –40 C < TA < +125 C, |

|||||||

unless otherwise noted.) |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

|

Condition |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

INTERFACE TIMING* |

|

|

|

|

|

|

|

|

Chip Select Write Pulse Width |

|

tWCS |

|

|

35 |

|

|

ns |

Chip Select Read Pulse Width |

|

tRCS |

|

|

130 |

|

|

ns |

Write Setup |

|

tWS |

|

|

50 |

|

|

ns |

Write Hold |

|

tWH |

|

|

0 |

|

|

ns |

Address Setup |

|

tAS |

|

|

50 |

|

|

ns |

Address Hold |

|

tAH |

|

|

0 |

|

|

ns |

Load Setup |

|

tLS |

|

|

0 |

|

|

ns |

Load Hold |

|

tLH |

|

|

0 |

|

|

ns |

Write Data Setup |

|

tWDS |

|

|

50 |

|

|

ns |

Write Data Hold |

|

tWDH |

|

|

0 |

|

|

ns |

Load Data Pulse Width |

|

tLDW |

|

|

35 |

|

|

ns |

Reset Pulse Width |

|

tRESET |

|

|

35 |

|

|

ns |

Read Data Hold |

|

tRDH |

|

|

0 |

|

|

ns |

Read Data Setup |

|

tRDS |

|

|

0 |

|

|

ns |

Data to Hi-Z |

|

tDZ |

|

CL = 10 pF |

80 |

|

100 |

ns |

Chip Select to Data |

|

tCSD |

|

CL = 10 pF |

80 |

|

100 |

ns |

Chip Select Repetitive Pulse Width |

|

tCSP |

|

|

20 |

|

|

ns |

Load Setup in Double Buffer Mode |

|

tLDS |

|

|

35 |

|

|

ns |

Load Data Hold |

|

tLDH |

|

|

0 |

|

|

ns |

*All input control signals are specified with tR = tF = 2 ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V. Specifications subject to change without notice.

REV. A |

–5– |

AD5582/AD5583

ABSOLUTE MAXIMUM RATINGS* |

|

|

|

VDD to VSS . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

–0.3 V to +18 V |

|

VDD to GND . . . . . . . . . . . . . . . . . . . |

. . . . . . |

–0.3 V to +18 V |

|

VSS to GND . . . . . . . . . . . . . . . . . . . . |

. . . . . . . |

+0.3 V to –9 V |

|

VDD to VREF+ . . . . . . . . . . . . . . . . . . . |

. . . . . . |

–0.3 V to +18 V |

|

VREF– to VSS . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

–0.3 V to +18 |

V |

VREFH to VREFL . . . . . . . . . . . . . . . . . . |

. . . . . . |

–0.3 V to +18 |

V |

DVDD to GND . . . . . . . . . . . . . . . . . . |

. . . . . . . |

. . . . . . . . . 8 V |

|

Logic Inputs to GND . . . . . . . . . . . |

VSS – 0.3 V, VDD + 0.3 |

V |

|

VOUT to GND . . . . . . . . . . . . . . . . . |

VSS – 0.3 V, VDD + 0.3 |

V |

|

IOUT Short Circuit to GND . . . . . . . . |

. . . . . . . |

. . . . . . . 24 mA |

|

Thermal Resistance Junction to Ambient, JA . |

. . . . . 115∞C/W |

||

Thermal Resistance Junction to Case, JC . . . . . . . . . . 42∞C/W Maximum Junction Temperature (TJ Max) . . . . . . . . . . 150∞C

Package Power Dissipation = (TJ Max – TA)/ JA

Operating Temperature Range . . . . . . . . . . –40∞C to +125∞C Storage Temperature Range . . . . . . . . . . . . –65∞C to +150∞C Lead Temperature

RV-48 (Soldering, 60 secs) . . . . . . . . . . . . . . . . . . . . 300∞C

*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ORDERING GUIDE1

|

Resolution |

Temperature |

Package |

Package |

Container |

Top |

Model |

(Bits) |

Range |

Description |

Option |

Quantity |

Marking2 |

AD5582YRV-REEL1 |

12 |

–40∞C to +125∞C |

TSSOP-48 |

RV-48 |

2500 |

AD5582Y |

AD5583YRV-REEL |

10 |

–40∞C to +125∞C |

TSSOP-48 |

RV-48 |

2500 |

AD5583Y |

AD5582YRV1 |

12 |

–40∞C to +125∞C |

TSSOP-48 |

RV-48 |

39 |

AD5582Y |

AD5583YRV |

10 |

–40∞C to +125∞C |

TSSOP-48 |

RV-48 |

39 |

AD5583Y |

NOTES

1The AD5582 contains 4116 transistors. The die size measures 108 mil 144 mil.

2First row marking is shown in the table above. Second row marking contains date code in YYWW format. Third row marking contains the lot number.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD5582/AD5583 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING! |

ESD SENSITIVE DEVICE |

–6– |

REV. A |

Loading...

Loading...