Analog Devices AD606JR-REEL, AD606JR, AD606JN, AD606JCHIPS, AD606JR-REEL7 Datasheet

a 50 MHz, 80 dB Demodulating

Logarithmic Amplifier with Limiter Output

AD606

FEATURES

Logarithmic Amplifier Performance –75 dBm to +5 dBm Dynamic Range ≤1.5 nV/√Hz Input Noise

Usable to >50 MHz

37.5 mV/dB Voltage Output On-Chip Low-Pass Output Filter

Limiter Performance

61 dB Output Flatness over 80 dB Range

638 Phase Stability at 10.7 MHz over 80 dB Range

Adjustable Output Amplitude Low Power

+5 V Single Supply Operation

65 mW Typical Power Consumption CMOS-Compatible Power-Down to 325 mW typ <5 ms Enable/Disable Time

APPLICATIONS

Ultrasound and Sonar Processing Phase-Stable Limiting Amplifier to 100 MHz Received Signal Strength Indicator (RSSI) Wide Range Signal and Power Measurement

PRODUCT DESCRIPTION

The AD606 is a complete, monolithic logarithmic amplifier using a 9-stage “successive-detection” technique. It provides both logarithmic and limited outputs. The logarithmic output is from a three-pole post-demodulation low-pass filter and provides

a loadable output voltage of +0.1 V dc to +4 V dc. The logarithmic scaling is such that the output is +0.5 V for a sinusoidal input of –75 dBm and +3.5 V at an input of +5 dBm; over this range the logarithmic linearity is typically within ± 0.4 dB. All scaling parameters are proportional to the supply voltage.

The AD606 can operate above and below these limits, with reduced linearity, to provide as much as 90 dB of conversion range. A second low-pass filter automatically nulls the input offset of the first stage down to the submicrovolt level. Adding external capacitors to both filters allows operation at input frequencies as low as a few hertz.

The AD606’s limiter output provides a hard-limited signal output as a differential current of ± 1.2 mA from open-collector outputs. In a typical application, both of these outputs are loaded by 200 Ω resistors to provide a voltage gain of more than 90 dB from the input. Transition times are 1.5 ns, and the phase is stable to within ±3° at 10.7 MHz for signals from

–75 dBm to +5 dBm.

The logarithmic amplifier operates from a single +5 V supply and typically consumes 65 mW. It is enabled by a CMOS logic level voltage input, with a response time of <5 µs. When disabled, the standby power is reduced to <1 mW within 5 µs.

The AD606J is specified for the commercial temperature range of 0°C to +70°C and is available in 16-lead plastic DIPs or SOICs. Consult the factory for other packages and temperature ranges.

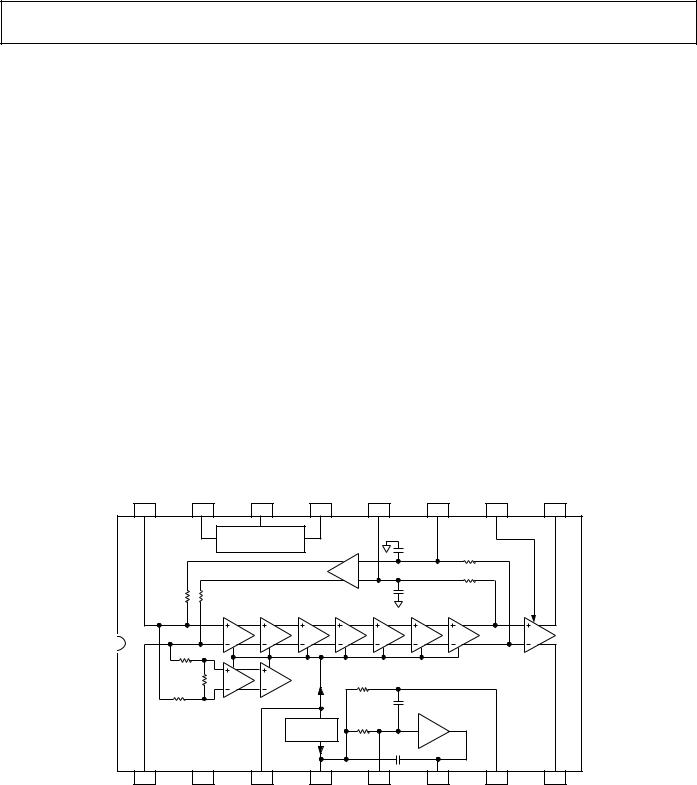

FUNCTIONAL BLOCK DIAGRAM

INHI |

COMM |

PRUP |

VPOS |

FIL1 |

|

FIL2 |

LADJ |

LMHI |

|

16 |

|

15 |

14 |

13 |

12 |

|

11 |

10 |

9 |

|

|

|

REFERENCE |

|

|

|

|

|

|

|

|

|

AND POWER-UP |

30pF |

|

|

|

||

|

|

|

|

|

360kV |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

|

|

|

|

30kV |

|

30kV |

|

|

30pF |

|

360kV |

|

|

|

|

|

|

|

|

|

|||

|

|

|

OFFSET-NULL |

|

|

||||

|

|

|

|

|

|

|

|||

|

|

|

|

|

LOW-PASS FILTER |

|

|

||

1.5kV |

|

|

|

|

|

|

|

FINAL |

|

|

|

|

|

|

MAIN SIGNAL PATH |

|

|||

|

|

|

|

|

|

LIMITER |

|||

|

|

|

|

|

11.15dB/STAGE |

|

|||

250V |

|

|

|

|

|||||

|

|

|

|

|

|

|

|||

|

|

|

|

12mA/dB |

9.375kV |

|

TWO-POLE |

|

|

1.5kV |

HIGH-END |

2pF |

|

|

|

||||

|

|

|

SALLEN-KEY |

|

|

||||

|

|

DETECTORS |

|

|

|

|

|

||

|

|

|

9.375kV |

|

FILTER |

|

|

||

|

|

|

|

ONE-POLE |

|

|

|

||

|

|

|

|

X2 |

|

|

|||

|

|

|

|

|

|

|

|||

AD606 |

|

FILTER |

|

|

|

||||

|

|

|

|

|

|

||||

|

2mA/dB |

2pF |

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

3 |

4 |

5 |

|

6 |

7 |

8 |

INLO |

COMM |

ISUM |

ILOG |

BFIN |

|

VLOG |

OPCM |

LMLO |

|

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 1999 |

AD606–SPECIFICATIONS (@ TA = +258C and supply = +5 V unless otherwise noted; dBm assumes 50 V)

Model |

|

|

AD606J |

|

|

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

SIGNAL INPUT |

|

|

|

|

|

Log Amp fMAX |

AC Coupled; Sinusoidal Input |

|

50 |

|

MHz |

Limiter fMAX |

AC Coupled; Sinusoidal Input |

|

100 |

|

MHz |

Dynamic Range |

|

|

80 |

|

dB |

Input Resistance |

Differential Input |

500 |

2,500 |

|

Ω |

Input Capacitance |

Differential Input |

|

2 |

|

pF |

|

|

|

|

|

|

SIGNAL OUTPUT |

|

|

|

|

|

Limiter Flatness |

–75 dBm to +5 dBm Input Signal at 10.7 MHz |

–1.5 |

|

+1.5 |

dB |

|

With Pin 9 to VPOS via a 200 Ω Resistor |

|

|

|

|

|

and Pin 8 to VPOS via a 200 Ω Resistor |

|

|

|

|

Output Current |

At Pins 8 or 9, Proportional to VPOS, LADJ Grounded |

|

1.2 |

|

mA |

|

LADJ Open Circuited |

|

0.48 |

|

mA |

Phase Variation with Input Level |

–75 dBm to +5 dBm Input Signal at 10.7 MHz |

|

± 3 |

|

Degrees |

|

|

|

|

|

|

LOG (RSSI) OUTPUT |

At 10.7 MHz; (0.0075 × VPOS)/dB |

|

|

|

|

Nominal Slope |

|

37.5 |

|

mV/dB |

|

|

At 45 MHz |

|

35 |

|

mV/dB |

Slope Accuracy |

Untrimmed at 10.7 MHz |

–15 |

± 5 |

+15 |

% |

Intercept |

Sinusoidal Input; Independent of VPOS |

|

–88.33 |

|

dBm |

Logarithmic Conformance |

–75 dBm to +5 dBm Input Signal at 10.7 MHz |

–1.5 |

0.4 |

+1.5 |

dB |

Nominal Output |

Input Level = –75 dBm |

|

0.5 |

|

V |

|

Input Level = –35 dBm |

|

2 |

|

V |

|

Input Level = +5 dBm |

|

3.5 |

|

V |

Accuracy over Temperature |

After Calibration at –35 dBm at 10.7 MHz |

–3 |

|

+3 |

dB |

|

TMIN to TMAX |

|

|

|

|

Video Response Time |

From Onset of Input Signal Until Output Reaches |

|

400 |

|

ns |

|

95% of Final Value |

|

|

|

|

|

|

|

|

|

|

POWER-DOWN INTERFACE |

|

|

|

|

µs |

Power-Up Response Time |

Time Delay Following HI Transition Until |

|

3.5 |

|

|

|

Device Meets Full Specifications |

|

|

|

|

|

AC Coupled with 100 pF Coupling Capacitors |

|

|

|

|

Input Bias Current |

Logical HI Input (See Figure 12) |

|

1 |

|

nA |

|

Logical LO Input |

|

4 |

|

µA |

|

|

|

|

|

|

POWER SUPPLY |

|

|

|

|

|

Operating Range |

|

4.5 |

|

5.5 |

V |

Powered-Up Current |

Zero Signal Input |

|

13 |

|

mA |

|

TMIN to TMAX |

|

13 |

20 |

mA |

Powered-Down Current |

TMIN to TMAX |

|

65 |

200 |

µA |

Specifications subject to change without notice.

–2– |

REV. B |

AD606

ABSOLUTE MAXIMUM RATINGS1 |

|

Supply Voltage VPOS . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . +9 V |

Internal Power Dissipation2 . . . . . . . . . . . . . |

. . . . . . 600 mW |

Operating Temperature Range . . . . . . . . . . . |

. . 0°C to +70°C |

Storage Temperature Range . . . . . . . . . . . . |

–65°C to +150°C |

Lead Temperature Range (Soldering 60 sec) . |

. . . . . . . +300°C |

NOTES

1Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2Specification is for device in free air: 16-Lead Plastic DIP Package: θJA = 85°C/W 16-Lead SOIC Package: θJA = 100°C/W

ORDERING GUIDE

|

Temperature |

Package |

Package |

Model |

Range |

Description |

Option |

|

|

|

|

AD606JN |

0°C to +70°C |

16-Lead Plastic DIP |

N-16 |

AD606JR |

0°C to +70°C |

16-Lead Narrow-Body |

R-16A |

|

|

SOIC |

|

AD606JR-REEL |

0°C to +70°C |

13" Tape and Reel |

R-16A |

AD606JR-REEL7 |

0°C to +70°C |

7" Tape and Reel |

R-16A |

AD606-EB |

|

Evaluation Board |

|

AD606JCHIPS |

0°C to +70°C |

Die |

|

|

|

|

|

PIN DESCRIPTION

Plastic DIP (N)

and

Small Outline (R)

Packages

INLO |

|

|

|

|

|

INHI |

1 |

|

|

|

16 |

||

COMM |

|

|

|

|

|

COMM |

2 |

|

|

|

15 |

||

ISUM |

|

|

|

|

|

PRUP |

3 |

|

|

|

14 |

||

ILOG |

|

AD606 |

|

VPOS |

||

|

|

|||||

4 |

13 |

|||||

BFIN |

|

TOP VIEW |

|

FIL1 |

||

5 |

(Not to Scale) |

12 |

||||

VLOG |

|

|

|

|

|

FIL2 |

6 |

|

|

|

11 |

||

OPCM |

|

|

|

|

|

LADJ |

7 |

|

|

|

10 |

||

LMLO |

|

|

|

|

|

LMHI |

8 |

|

|

|

9 |

||

|

|

|

|

|

|

|

PIN FUNCTION DESCRIPTIONS

Pin |

Mnemonic |

Function |

|

|

|

1 |

INLO |

DIFFERENTIAL RF INPUT |

|

|

–75 dBm to +5 dBm, Inverting, AC Coupled. |

2 |

COMM |

POWER SUPPLY COMMON |

|

|

Connect to Ground. |

3 |

ISUM |

LOG DETECTOR SUMMING NODE |

4 |

ILOG |

LOG CURRENT OUTPUT |

|

|

Normally No Connection; 2 µA/dB Output |

|

|

Current. |

5 |

BFIN |

BUFFER INPUT |

|

|

Optionally Used to Realize Low Frequency |

|

|

Post-Demodulation Filters. |

6 |

VLOG |

BUFFERED LOG OUTPUT |

|

|

37.5 mV/dB (100 mV to 4.5 V). |

7 |

OPCM |

OUTPUT COMMON |

|

|

Connect to Ground. |

8 |

LMLO |

DIFFERENTIAL LIMITER OUTPUT |

|

|

1.2 mA Full-Scale Output Current. Open |

|

|

Collector Output Must Be “Pulled” Up to |

|

|

VPOS with R ≤ 400 Ω. |

9 |

LMHI |

DIFFERENTIAL LIMITER OUTPUT |

|

|

1.2 mA Full-Scale Output Current. Open |

|

|

Collector Output Must Be “Pulled” Up to |

|

|

VPOS with R ≤ 400 Ω. |

10 |

LADJ |

LIMITER LEVEL ADJUSTMENT |

|

|

Optionally Used to Adjust Limiter Output |

|

|

Current. |

11 |

FIL1 |

OFFSET LOOP LOW-PASS FILTER |

|

|

Normally No Connection; a Capacitor Between |

|

|

FIL1 and FIL2 May Be Added to Lower the |

|

|

Filter Cutoff Frequency. |

12 |

FIL2 |

OFFSET LOOP LOW-PASS FILTER |

|

|

Normally No Connection; See Above. |

13 |

VPOS |

POSITIVE SUPPLY |

|

|

Connect to +5 V at 13 mA. |

14 |

PRUP |

POWER UP |

|

|

CMOS (5 V) Logical High = Device On |

|

|

(≈ 65 mW). |

|

|

CMOS (0 V) Logical Low = Device Off |

|

|

(≈ 325 µW). |

15 |

COMM |

POWER SUPPLY COMMON |

|

|

Connect to Ground. |

16 |

INHI |

DIFFERENTIAL RF INPUT |

|

|

–75 dBm to +5 dBm, Noninverting, AC-Coupled. |

|

|

|

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD606 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. B |

–3– |

AD606

INPUT LEVEL CONVENTIONS

RF logarithmic amplifiers usually have their input specified in “dBm,” meaning “decibels with respect to 1 mW.” Unfortunately, this is not precise for several reasons.

1.Log amps respond not to power but to voltage. In this respect, it would be less ambiguous to use “dBV” (decibels referred to 1 V) as the input metric. Also, power is dependent on the rms (root mean-square) value of the signal, while log amps are not inherently rms responding.

2.The response of a demodulating log amp depends on the waveform. Convention assumes that the input is sinusoidal. However, the AD606 is capable of accurately handling any input waveform, including ac voltages, pulses and square waves, Gaussian noise, and so on. See the AD640 data sheet, which covers the effect of waveform on logarithmic intercept, for more information.

3.The impedance in which the specified power is measured is

not always stated. In the log amp context it is invariably assumed to be 50 Ω. Thus, 0 dBm means “1 mW rms in 50 Ω,”

and corresponds to an rms voltage of (1 mW × 50 Ω), or 224 mV.

Popular convention requires the use of dBm to simplify the comparison of log amp specifications. Unless otherwise stated, sinusoidal inputs expressed as dBm in 50 Ω are used to specify the performance of the AD606 throughout this data sheet. We will also show the corresponding rms voltages where it helps to clarify the specification. Noise levels will likewise be given in dBm; the response to Gaussian noise is 0.5 dB higher than for a sinusoidal input of the same rms value.

Note that dynamic range, being a simple ratio, is always specified simply as “dB”, and the slope of the logarithmic transfer function is correctly specified as “mV/dB,” NOT as “mV/dBm.”

LOGARITHMIC SLOPE AND INTERCEPT

A generalized logarithmic amplifier having an input voltage VIN and output voltage VLOG must satisfy a transfer function of the form

VLOG = VY log10 (VIN /VX )

where, in the case of the AD606, the voltage VIN is the difference between the voltages on pins INHI and INLO, and the voltage VLOG is that measured at the output pin VLOG. VY and VX are fixed voltages that determine the slope and intercept of the logarithmic amplifier, respectively. These parameters are inherent in the design of a particular logarithmic amplifier, although may be adjustable, as in the AD606. When VIN = VX, the logarithmic argument is one, hence the logarithm is zero. VX is, therefore, called the logarithmic intercept voltage because the output voltage VLOG crosses zero for this input. The slope voltage VY is can also be interpreted as the “volts per decade” when using base-10 logarithms as shown here.

Note carefully that VLOG and VLOG in the above paragraph (and elsewhere in this data sheet) are different. The first is a voltage; the second is a pin designation.

This equation suggests that the input VIN is a dc quantity, and, if VX is positive, that VIN must likewise be positive, since the logarithm of a negative number has no simple meaning. In fact, in the AD606, the response is independent of the sign of VIN because of the particular way in which the circuit is built. This is part of the demodulating nature of the amplifier, which

results in an alternating input voltage being transformed into a quasi-dc (rectified and filtered) output voltage.

The single supply nature of the AD606 results in common-mode level of the inputs INHI and INLO being at about +2.5 V (using the recommended +5 V supply). In normal ac operation, this bias level is developed internally and the input signal is coupled in through dc blocking capacitors. Any residual dc offset voltage in the first stage limits the logarithmic accuracy for small inputs. In ac operation, this offset is automatically and continuously nulled via a feedback path from the last stage, provided that the pins INHI and INLO are not shorted together, as would be the case if transformer coupling were used for the signal.

While any logarithmic amplifier must eventually conform to the basic equation shown above, which, with appropriate elaboration, can also fully account for the effect of the signal waveform on the effective intercept,1 it is more convenient in RF applications to use a simpler expression. This simplification results from first, assuming that the input is always sinusoidal, and second, using a decibel representation for the input level. The standard representation of RF levels is (incorrectly, in a log amp context) in terms of power, specifically, decibels above 1 milliwatt (dBm) with a presumed impedance level of 50 Ω. That being the case, we can rewrite the transfer function as

VLOG = VY (PIN ± PX )

where it must be understood that PIN means the sinusoidal input power level in a 50 Ω system, expressed in dBm, and PX is the intercept, also expressed in dBm. In this case, PIN and PX are simple, dimensionless numbers. (PX is sometimes called the “logarithmic offset,” for reasons which are obvious from the above equation.) VY is still defined as the logarithmic slope, usually specified as so many millivolts per decibel, or mV/dB.

In the case of the AD606, the slope voltage, VY, is nominally

750 mV when operating at VPOS = 5 V. This can also be expressed as 37.5 mV/dB or 750 mV/decade; thus, the 80 dB

range equates to 3 V. Figure 1 shows the transfer function of the AD606. The slope is closely proportional to VPOS, and can more generally be stated as VY = 0.15 × VPOS. Thus, in those applications where the scaling must be independent of supply voltage, this must be stabilized to the required accuracy. In applications where the output is applied to an A/D converter, the reference

|

4 |

|

|

|

|

|

|

|

3.5 |

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

DC |

2.5 |

|

|

|

|

|

|

Volts |

|

|

|

|

|

|

|

|

SLOPE = 37.5mV/dB |

|

|

|

|||

2 |

|

|

|

|

|

|

|

– |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VLOG |

1.5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

0.5 |

|

INTERCEPT |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

AT –88.33dBm |

|

|

|

|

|

|

|

|

|

|

|

|

|

–100 |

–80 |

–60 |

–40 |

–20 |

0 |

+20 |

INPUT SIGNAL – dBm

Figure 1. Nominal Transfer Function

1See, for example, the AD640 data sheet, which is published in Section 3 of the Special Linear Reference Manual or Section 9.3 of the 1992 Amplifier Applications Guide.

–4– |

REV. B |

Loading...

Loading...