Texas Instruments SMJ4C1024-10FQ, SMJ4C1024-10HJ, SMJ4C1024-10HK, SMJ4C1024-10HL, SMJ4C1024-10JD Datasheet

...

SMJ4C1024 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

DOrganization . . . 1048576 × 1-Bit

DProcessed to MIL-STD-883, Class B

DSingle 5-V Supply (10% Tolerance)

DPerformance Ranges:

|

ACCESS ACCESS ACCESS |

READ |

||

|

TIME |

TIME |

TIME |

OR |

|

ta(R) |

ta(C) |

ta(CA) |

WRITE |

|

(tRAC) (tCAC) (tAA) |

CYCLE |

||

|

(MAX) |

(MAX) |

(MAX) |

(MIN) |

'4C1024-80 |

80 ns |

20 ns |

40 ns |

150 ns |

'4C1024-10 |

100 ns |

25 ns |

45 ns |

190 ns |

'4C1024-12 |

120 ns |

30 ns |

55 ns |

220 ns |

'4C1024-15 |

150 ns |

40 ns |

70 ns |

260 ns |

DEnhanced Page-Mode Operation for Faster Memory Access

±Higher Data Bandwidth Than Conventional Page Mode Parts

±Random Single-Bit Access Within a Row With a Column Address

DOne of TI's CMOS Megabit Dynamic

Random-Access Memory (DRAM) Family Including SMJ44C256 Ð 256K × 4

Enhanced Page Mode

DCAS-Before-RAS (CBR) Refresh

DLong Refresh Period

512-Cycle Refresh in 8 ms (Max)

D3-State Unlatched Output

DLow Power Dissipation

DAll Inputs/Outputs and Clocks Are TTL-Compatible

DPackaging Offered:

±20/26-Pin J-Leaded Ceramic Surface Mount Package (HJ Suffix)

±18-Pin 300-Mil Ceramic Dual-In-Line Package (JD Suffix)

±20-Pin Ceramic Flatpack (HK Suffix)

±20/26-Terminal Leadless Ceramic Surface Mount Package (FQ/HL Suffixes)

±20-Pin Ceramic Zig-Zag In-Line Package (SV Suffix)

DOperating Temperature Range

± 55°C to 125°C

|

|

|

HJ PACKAGE |

|

|

|

|

|

|

JD PACKAGE |

|

||||||

|

|

|

|

( TOP VIEW ) |

|

|

|

|

|

|

|

( TOP VIEW ) |

|

||||

|

D |

|

|

|

|

|

|

VSS |

|

|

|

|

|

|

|

|

|

|

|

1 |

20 |

|

|

|

|

D |

|

1 |

18 |

|

VSS |

||||

|

|

|

|

|

|

|

|

||||||||||

|

|

||||||||||||||||

|

W |

|

2 |

19 |

|

|

Q |

|

|

W |

|

|

2 |

17 |

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

RAS |

|

3 |

18 |

|

|

CAS |

|

RAS |

|

|

3 |

16 |

|

CAS |

|||

|

|

|

|

|

|

||||||||||||

TF |

|

4 |

17 |

|

|

NC |

|

|

|

||||||||

NC |

|

5 |

16 |

|

|

A9 |

|

TF |

|

4 |

15 |

|

A9 |

||||

|

|

|

|

|

|

|

|

|

|

A0 |

|

5 |

14 |

|

A8 |

||

|

|

|

|

|

|

|

|

|

|

A1 |

|

6 |

13 |

|

A7 |

||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

A0 |

|

6 |

15 |

|

|

A8 |

|

A2 |

|

7 |

12 |

|

A6 |

||||

|

|

|

|

|

|

||||||||||||

|

|

|

|

A3 |

|

8 |

11 |

|

A5 |

||||||||

A1 |

|

7 |

14 |

|

|

A7 |

|

|

|

||||||||

|

|

|

|

VCC |

|

9 |

10 |

|

A4 |

||||||||

A2 |

|

8 |

13 |

|

|

A6 |

|

|

|

||||||||

A3 |

|

9 |

12 |

|

|

A5 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VCC |

|

10 |

11 |

|

|

A4 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

HK PACKAGE ( TOP VIEW )

|

D |

|

|

1 |

20 |

|

|

|

VSS |

|||

|

|

|

||||||||||

|

W |

|

|

|

|

|

2 |

19 |

|

|

|

Q |

|

|

|

|

|

||||||||

RAS |

|

|

|

|

3 |

18 |

|

|

|

CAS |

||

|

|

|

|

|||||||||

TF |

|

|

4 |

17 |

|

|

|

NC |

||||

|

|

|

|

|||||||||

NC |

|

|

5 |

16 |

|

|

|

A9 |

||||

|

|

|

|

|||||||||

A0 |

|

|

6 |

15 |

|

|

|

A8 |

||||

|

|

|

|

|||||||||

A1 |

|

|

7 |

14 |

|

|

|

A7 |

||||

|

|

|

|

|||||||||

A2 |

|

|

8 |

13 |

|

|

|

A6 |

||||

|

|

|

|

|||||||||

A3 |

|

|

9 |

12 |

|

|

|

A5 |

||||

|

|

|

|

|||||||||

VCC |

|

|

10 |

11 |

|

|

|

A4 |

||||

|

|

|

|

|

||||||||

FQ / HL PACKAGES |

SV PACKAGE |

( TOP VIEW ) |

( SIDE VIEW ) |

|

D |

|

10 |

11 |

|

VSS |

|

A9 |

|

1 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||||||||

|

W |

|

9 |

12 |

|

Q |

|

Q |

|

2 |

|

|

CAS |

|||

|

|

|

|

|

3 |

|

|

VSS |

||||||||

|

|

|

|

|

|

|

|

|

D |

|

4 |

|

|

|||

RAS |

|

8 |

13 |

|

CAS |

|

|

|

|

|||||||

|

|

|

|

|

||||||||||||

|

|

|

|

5 |

|

|

W |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

||

TF |

|

7 |

14 |

|

NC |

RAS |

|

7 |

|

|

TF |

|||||

|

|

|

||||||||||||||

NC |

|

6 |

15 |

|

A9 |

|

NC |

|

8 |

|

|

|||||

|

|

|

|

9 10 |

|

|

NC |

|||||||||

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

A0 |

|

1112 |

|

|

A1 |

||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

A2 |

|

1314 |

|

|

A3 |

||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||||||

A0 |

|

5 |

16 |

|

A8 |

|

VCC |

|

1516 |

|

|

A4 |

||||

|

|

|||||||||||||||

|

|

|||||||||||||||

A1 |

|

4 |

17 |

|

A7 |

|

A5 |

|

1718 |

|

|

A6 |

||||

|

|

|||||||||||||||

A2 |

|

3 |

18 |

|

A6 |

|

A7 |

|

1920 |

|

|

A8 |

||||

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|||||||||

A3 |

|

2 |

19 |

|

A5 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||||||||

VCC |

|

1 |

20 |

|

A4 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443

Copyright 1996, Texas Instruments Incorporated

1

SMJ4C1024 1048576 BY 1-BIT

DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

|

|

|

PIN NOMENCLATURE |

|

A0 ± A9 |

Address Inputs |

|

|

CAS |

Column Address Strobe |

|

|

D |

Data In |

|

|

NC |

No Internal Connection |

|

|

Q |

Data Out |

|

|

RAS |

|

Row Address Strobe |

|

TF |

Test Function |

|

|

VCC |

5-V Supply |

|

|

VSS |

Ground |

|

|

W |

Write Enable |

|

|

|

|

|

description

The SMJ4C1024 is a 1048576-bit DRAM organized as 1048576 words of one bit each. It employs technology for high performance, reliability, and low power at a low cost.

This device features maximum RAS access times of 80 ns, 100 ns, 120 ns, and 150 ns. Maximum power dissipation is as low as 305 mW operating and 16.5 mW standby on 150-ns devices.

IDD peaks are typIcally 140 mA and a ±1 V input voltage undershoot can be tolerated, minimizing system noise.

All inputs and outputs, including clocks, are compatible with series 54 TTL. All addresses and data-in lines are latched on-chip to simplify system design. Data out is unlatched to allow greater system flexibility.

The SMJ4C1024 is offered in an 18-pin ceramic dual-in-line package (JD suffix), a 20/26-terminal leadless ceramic carrier package (FQ/HL suffixes), a 20/26-pin J-leaded carrier package (HJ suffix), a 20-pin flatpack (HK suffix), and a 20-pin ceramic zig-zag in-line package (SV suffix). They are characterized for operation from

± 55°C to 125°C.

2 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ4C1024 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

logic symbol²

5 |

RAM 1024K 1 |

|

|

||

20D10/21D0 |

|

|

|

|

|

A0 |

|

|

|

|

|

6 |

|

|

|

|

|

A1 |

|

|

|

|

|

7 |

|

|

|

|

|

A2 |

|

|

|

|

|

8 |

|

|

|

|

|

A3 |

|

|

|

|

|

10 |

|

|

|

0 |

|

A4 |

|

A |

|

|

|

11 |

|

1 048 575 |

|

||

A5 |

|

|

|

||

12 |

|

|

|

|

|

A6 |

|

|

|

|

|

13 |

|

|

|

|

|

A7 |

|

|

|

|

|

14 |

|

|

|

|

|

A8 |

|

|

|

|

|

15 |

20D19/21D9 |

|

|

|

|

A9 |

|

|

|

|

|

|

C20 [ROW] |

|

|

|

|

3 |

G23 [REFRESH ROW] |

|

|

||

24 [PWR DWN] |

|

|

|

|

|

RAS |

|

|

|

|

|

|

C21 [COL] |

|

|

|

|

16 |

G24 |

|

|

|

|

& |

|

|

|

|

|

CAS |

23C22 |

|

|

||

|

|

|

|

||

2 |

23,21D |

24EN |

|

|

|

W |

|

17 |

|||

1 |

A, 22D |

|

|

A |

|

D |

|

|

Q |

||

²This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

The pin numbers shown are for the 18-pin JD package.

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

3 |

SMJ4C1024 1048576 BY 1-BIT

DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

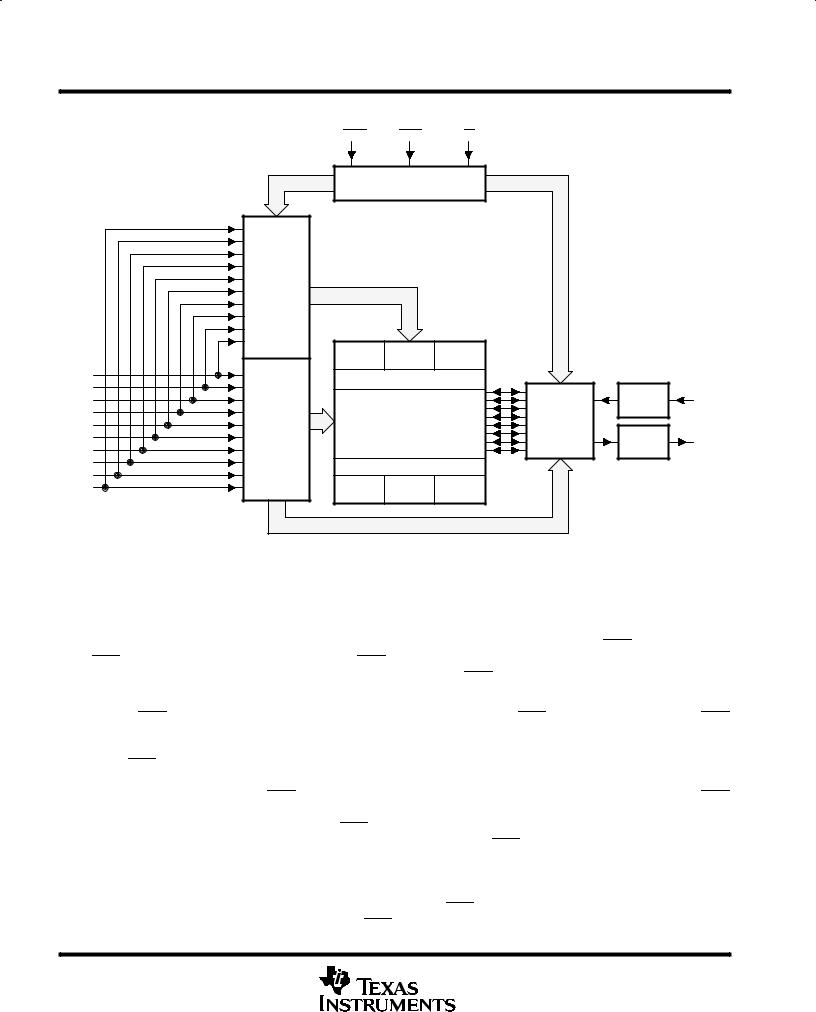

functional block diagram

RAS |

CAS |

W |

Timing and Control

|

Row |

|

|

|

|

|

|

|

Address |

|

|

|

|

|

|

|

Buffers |

|

|

|

|

|

|

|

(10) |

|

|

|

|

|

|

|

|

256K |

Row |

256K |

|

|

|

A0 |

|

Array |

Decode |

Array |

|

|

|

|

Sense Amplifiers |

|

|

|

|||

A1 |

|

|

|

|

|||

|

|

|

|

|

Data In |

|

|

A2 |

|

|

|

|

I/O |

D |

|

Column |

|

|

|

Reg. |

|||

A3 |

|

|

|

|

|||

Column Decode |

Buffers |

|

|

||||

A4 |

Address |

|

|

||||

1 of 8 |

|

|

|||||

|

|

|

Data |

|

|||

A5 |

Buffers |

|

|

|

Q |

||

|

|

|

Selection |

||||

A6 |

(10) |

|

|

|

Out Reg. |

||

|

|

|

|

|

|||

A7 |

|

Sense Amplifiers |

|

|

|

||

A8 |

|

256K |

Row |

256K |

|

|

|

A9 |

|

|

|

|

|||

|

Array |

Decode |

Array |

|

|

|

|

|

|

|

|

|

|||

operation

enhanced page mode

Enhanced page-mode operation allows faster memory access by keeping the same row address while selecting random column addresses. The time for row-address setup and hold and for address multiplexing is eliminated. The maximum number of columns that can be accessed is determined by the maximum RAS low time and the CAS page-cycle time used. With minimum CAS page-cycle time, all 1024 columns specified by column addresses A0 through A9 can be accessed without intervening RAS cycles.

Unlike conventional page-mode DRAMs, the column-address buffers in this device are activated on the falling edge of RAS. The buffers act as transparent or flow-through latches while CAS is high. The falling edge of CAS latches the column addresses. This feature lets the SMJ4C1024 operate at a higher data bandwidth than conventional page-mode parts, since data retrieval begins as soon as the column address is valid rather than when CAS goes low. This performance improvement is referred to as enhanced page mode. A valid column address can be presented immediately after the row-address hold time has been satisfied, usually well in

advance of the falling edge of CAS. In this case, data is obtained after ta(C) maximum (access time from CAS low) if ta(CA) maximum (access time from column address) has been satisfied. If the column addresses for the

next page cycle are valid at the same time CAS goes high, access time for the next cycle is determined by the later occurrence of ta(CA) or ta(CP) (access time from rising edge of CAS).

address (A0±A9)

Twenty address bits are required to decode one of 1048576 storage cell locations. Ten row-address bits are set up on inputs A0 through A9 and latched onto the chip by RAS. The ten column-address bits are set up on pins A0 through A9 and latched onto the chip by CAS. All addresses must be stable on or before the falling edges

4 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ4C1024 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

address (A0±A9) (continued)

of RAS and CAS. RAS is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder. CAS is used as a chip select to activate the output buffer as well as to latch the address bits into the column-address buffer.

write enable (W)

The read or write mode is selected through W. A logic high on the W input selects the read mode and a logic low selects the write mode. The write-enable pin can be driven from standard TTL circuits without a pullup resistor. The data input is disabled when the read mode is selected. When W goes low prior to CAS (early write), data out remains in the high-impedance state for the entire cycle, permitting common input/output operation.

data in (D)

Data-in is written during a write or a read-modify-write cycle. Depending on the mode of operation, the falling edge of CAS or W strobes data into the on-chip latch. In an early-write cycle, W is brought low prior to CAS, and the data is strobed in by CAS with setup and hold times referenced to this signal. In a delayed-write or a read-modify-write cycle, CAS is already low, and the data is strobed in by W with setup and hold times referenced to this signal.

data out (Q)

The 3-state output buffers provide direct TTL compatibility (no pullup resistor required) with a fanout of two series 54 TTL loads. Data out is the same polarity as data in. The output is in the high-impedance (floating) state

until CAS is brought low. In a read cycle, the output becomes valid after the access time ta(C). The access time from CAS low (ta(C)) begins with the negative transition of CAS as long as ta(R) and ta(CA) are satisfied. The output

becomes valid after the access time has elapsed and remains valid while CAS is low; when CAS goes high, the output returns to a high-impedance state. In a delayed-write or read-modify-write cycle, the output follows the sequence for the read cycle.

refresh

A refresh operation must be performed at least once every 8 ms to retain data. This can be achieved by strobing each of the 512 rows (A0±A8). A normal read or write cycle refreshes all bits in each selected row. A RAS-only operation can be used by holding CAS at the high (inactive) level, conserving power as the output buffer remains in the high-impedance state. Externally generated addresses must be used for a RAS-only refresh. Hidden refresh can be performed while maintaining valid data at the output pin. This is accomplished by holding CAS at VIL after a read operation and cycling RAS after a specified precharge period, similar to a RAS-only refresh cycle.

CAS-before-RAS (CBR) refresh

CBR refresh is used by bringing CAS low earlier than RAS (see parameter td(CLRL)R) and holding it low after

RAS falls (parameter td(RLCH)R). For successive CBR refresh cycles, CAS can remain low while cycling RAS. The external address is ignored and the refresh address is generated internally. The external address is also

ignored during the hidden refresh cycles.

power up

To achieve proper device operation, an initial pause of 200 μs followed by a minimum of eight initialization cycles is required after full VCC level is achieved.

test function (TF) pin

During normal device operation, TF must be disconnected or biased at a voltage ≤ VCC.

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

5 |

SMJ4C1024 1048576 BY 1-BIT

DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Voltage range on any pin (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . ± 1 |

V to 7 V |

Voltage range on VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . ± 1 |

V to 7 V |

Short-circuit output current, IOS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

. 50 mA |

Power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . |

. . 1 W |

Operating free-air temperature range, TA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

± 55°C to 125°C |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

± 65°C to 150°C |

|

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to VSS.

recommended operating conditions

|

|

MIN |

NOM |

MAX |

UNIT |

|

|

|

|

|

|

VCC |

Supply voltage |

4.5 |

5 |

5.5 |

V |

VIH |

High-level input voltage |

2.4 |

|

6.5 |

V |

VIL |

Low-level input voltage (see Note 2) |

± 1 |

|

0.8 |

V |

TA |

Minimum operating free-air temperature |

± 55 |

|

|

°C |

TC |

Maximum operating case temperature |

|

|

125 |

°C |

NOTE 2: |

The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used for logic-voltage levels only. |

||||

6 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ4C1024 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|

PARAMETER |

|

|

|

|

TEST |

'4C1024-80 |

'4C1024-10 |

'4C1024-12 |

'4C1024-15 |

UNIT |

||||

|

|

|

CONDITIONS |

MIN MAX |

MIN MAX |

MIN MAX |

MIN MAX |

||||||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOH |

High-level |

|

IOH = ± 5 mA |

|

|

|

|

|

2.4 |

2.4 |

2.4 |

2.4 |

V |

||

output voltage |

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VOL |

Low-level |

|

IOL = 4.2 mA |

|

|

|

|

|

0.4 |

0.4 |

0.4 |

0.4 |

V |

||

output voltage |

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

II |

Input current |

|

VCC = 5.5 V, |

|

VI = 0 V to 6.5 V, |

± 10 |

± 10 |

± 10 |

± 10 |

μA |

|||||

(leakage) |

|

All other pins = 0 V to VCC |

|||||||||||||

|

|

|

|

|

|

|

|||||||||

|

Output |

|

VCC = 5.5 V, |

|

VO = 0 V to VCC, |

|

|

|

|

|

|||||

IO |

current |

|

|

± 10 |

± 10 |

± 10 |

± 10 |

μA |

|||||||

|

|

|

|

|

|

|

|

|

|||||||

|

CAS high |

|

|

|

|

|

|||||||||

|

(leakage) |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reador |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC1 |

write-cycle |

|

VCC = 5.5 V, |

|

Minimum cycle |

75 |

70 |

60 |

55 |

mA |

|||||

|

current |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Standby |

|

After one memory cycle, |

|

|

|

|

|

|||||||

ICC2 |

|

RAS and CAS high, |

3 |

3 |

3 |

3 |

mA |

||||||||

current |

|

||||||||||||||

|

|

VIH = 2.4 V |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Average |

|

VCC = 5.5 V, |

|

Minimum cycle, |

|

|

|

|

|

|||||

|

refresh |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RAS cycling, |

|

|

|

|

|

|

|

|

|

|

|||

ICC3 |

current |

|

|

|

|

|

|

70 |

65 |

55 |

50 |

mA |

|||

|

|

|

|

|

|

|

|

|

|||||||

|

CAS high (RAS only), |

||||||||||||||

|

(RAS only or |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RAS low after CAS low (CBR) |

|

|

|

|

|

||||||||

|

CBR) |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

ICC4 |

Average page |

|

VCC = 5.5 V, |

|

tPC = minimum, |

50 |

45 |

35 |

30 |

mA |

|||||

current |

|

|

|

|

|

|

|

|

|

||||||

|

RAS low, |

|

|

CAS cycling |

|||||||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

capacitance over recommended ranges of supply voltage and operating free-air temperature, f = 1 MHz (see Note 3)

|

PARAMETER |

HL / JD / FQ |

HJ |

HK |

SV |

UNIT |

|

|

|

|

|

|

|

||

|

MIN |

MAX |

MIN MAX |

MIN MAX |

MIN MAX |

||

|

|

|

|||||

|

|

|

|

|

|

|

|

Ci(A) |

Input capacitance, address inputs |

|

6 |

7 |

8 |

9 |

pF |

Ci(D) |

Input capacitance, data input |

|

5 |

5 |

6 |

7 |

pF |

Ci(RC) |

Input capacitance, strobe inputs |

|

7 |

7 |

8 |

8 |

pF |

Ci(W) |

Input capacitance, write-enable input |

|

7 |

7 |

7 |

7 |

pF |

Co |

Output capacitance |

|

7 |

9 |

10 |

8 |

pF |

NOTE 3: Capacitance is sampled only at initial design and after any major change. Samples are tested at 0 V and 25°C with a 1-MHz signal applied to the pin under test. All other pins are open.

switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 1)

|

PARAMETER |

ALT. |

'4C1024-80 |

'4C1024-10 |

'4C1024-12 |

'4C1024-15 |

UNIT |

|

||||||

|

SYMBOL |

MIN MAX |

MIN MAX |

MIN MAX |

MIN MAX |

|

||||||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

ta(C) |

Access time from |

|

low |

tCAC |

20 |

25 |

30 |

40 |

ns |

|

||||

CAS |

|

|||||||||||||

ta(CA) |

Access time from column address |

tAA |

40 |

45 |

55 |

70 |

ns |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

ta(R) |

Access time from |

RAS |

low |

tRAC |

80 |

100 |

120 |

150 |

ns |

|

||||

ta(CP) |

Access time from column precharge |

tCPA |

40 |

40 |

60 |

75 |

ns |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||

tdis(CH) |

Output disable time after |

CAS |

high |

tOFF |

20 |

25 |

30 |

35 |

ns |

|

||||

(see Note 4) |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

NOTE 4: tdis(CH) is specified when the output is no longer driven. The output is disabled by bringing |

CAS |

high. |

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

7 |

SMJ4C1024 1048576 BY 1-BIT

DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Note 5)

|

|

|

|

|

|

|

|

|

ALT. |

'4C1024-80 |

'4C1024-10 |

'4C1024-12 |

'4C1024-15 |

UNIT |

|||||

|

|

|

|

|

|

|

|

|

SYMBOL |

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tc(rd) |

Cycle time, read |

tRC |

150 |

|

190 |

|

220 |

|

260 |

|

ns |

||||||||

(see Note 6) |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tc(W) |

Cycle time, write |

tWC |

150 |

|

190 |

|

220 |

|

260 |

|

ns |

||||||||

tc(rdW) |

Cycle time, |

tRWC |

175 |

|

220 |

|

265 |

|

315 |

|

ns |

||||||||

read-write/read-modify-write |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tc(P) |

Cycle time, page-mode read |

tPC |

50 |

|

55 |

|

65 |

|

80 |

|

ns |

||||||||

or write (see Note 7) |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tc(PM) |

Cycle time, page-mode |

tPRWC |

75 |

|

85 |

|

110 |

|

135 |

|

ns |

||||||||

read-modify-write |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

tw(CH) |

Pulse duration, |

|

|

high |

tCP |

10 |

|

10 |

|

15 |

|

25 |

|

ns |

|||||

CAS |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

tw(CL) |

Pulse duration, |

CAS |

low |

tCAS |

20 |

10000 |

25 |

10000 |

30 |

10000 |

40 |

10000 |

ns |

||||||

(see Note 8) |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Pulse duration, |

|

high |

|

|

|

|

|

|

|

|

|

|

||||||

tw(RH) |

RAS |

tRP |

60 |

|

80 |

|

90 |

|

100 |

|

ns |

||||||||

(precharge) |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

Pulse duration, nonpage |

|

|

|

|

|

|

|

|

|

|

||||||||

tw(RL) |

mode, RAS low |

tRAS |

80 |

10000 |

100 |

10000 |

120 |

10000 |

150 |

10000 |

ns |

||||||||

|

(see Note 9) |

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

tw(RL)P |

Pulse duration, page mode, |

tRASP |

80 |

100000 |

100 |

100000 |

120 |

100000 |

150 |

100000 |

ns |

||||||||

RAS low (see Note 9) |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

tw(WL) |

Pulse duration, write |

tWP |

15 |

|

15 |

|

20 |

|

25 |

|

ns |

||||||||

tsu(CA) |

Setup time, column address |

tASC |

0 |

|

3 |

|

3 |

|

3 |

|

ns |

||||||||

before CAS low |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

tsu(RA) |

Setup time, row address |

tASR |

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||||||||

before RAS low |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

tsu(D) |

Setup time, data |

tDS |

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||||||||

(see Note 10) |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

tsu(rd) |

Setup time, read before |

CAS |

|

tRCS |

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||||||

low |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

Setup time, |

|

low before |

|

|

|

|

|

|

|

|

|

|

||||||

tsu(WCL) |

W |

tWCS |

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||||||||

CAS low (see Note 11) |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

tsu(WCH) |

Setup time, |

W |

low before |

tCWL |

20 |

|

25 |

|

30 |

|

40 |

|

ns |

||||||

CAS high |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

Setup time, |

|

low before |

|

|

|

|

|

|

|

|

|

|

||||||

tsu(WRH) |

W |

tRWL |

20 |

|

25 |

|

30 |

|

40 |

|

ns |

||||||||

RAS high |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

th(CA) |

Hold time, column address |

tCAH |

15 |

|

20 |

|

20 |

|

25 |

|

ns |

||||||||

after CAS low |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

th(RA) |

Hold time, row address after |

tRAH |

12 |

|

15 |

|

15 |

|

20 |

|

ns |

||||||||

RAS low |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES: 5. Timing measurements in this table are referenced to VIL max and VIH min.

6.All cycle times assume tt = 5 ns.

7.To assure tc(P) min, tsu(CA) should be ≥ tw(CH).

8.In a read-modify-write cycle, td(CLWL) and tsu(WCH) must be observed.

9.In a read-modify-write cycle, td(RLWL) and tsu(WRH) must be observed.

10.Referenced to the later of CAS or W in write operations

11.Early write operation only

8 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ4C1024 1048576 BY 1-BIT DYNAMIC RANDOM-ACCESS MEMORY

SGMS023E ± DECEMBER 1988 ± REVISED MARCH 1996

timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Note 5) (continued)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ALT. |

'4C1024-80 |

'4C1024-10 |

'4C1024-12 |

'4C1024-15 |

UNIT |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SYMBOL |

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

MIN |

MAX |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

th(RLCA) |

Hold time, column address after |

tAR |

60 |

|

70 |

|

80 |

|

100 |

|

ns |

||||||||||||||||||

RAS low (see Note 12) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

th(D) |

Hold time, data (see Note 10) |

tDH |

15 |

|

20 |

|

25 |

|

30 |

|

ns |

||||||||||||||||||

|

Hold time, data after |

|

|

|

|

|

|

|

|

low |

|

|

|

|

|

|

|

|

|

|

|||||||||

th(RLD) |

RAS |

|

|

|

tDHR |

60 |

|

70 |

|

85 |

|

110 |

|

ns |

|||||||||||||||

(see Note 12) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Hold time, read after |

|

|

|

|

|

|

|

high |

|

|

|

|

|

|

|

|

|

|

||||||||||

th(CHrd) |

CAS |

|

|

tRCH |

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||||||||||||||||

(see Note 13) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

th(RHrd) |

Hold time, read after |

RAS |

|

|

high |

tRRH |

10 |

|

10 |

|

10 |

|

10 |

|

ns |

||||||||||||||

(see Note 13) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

Hold time, write after |

|

|

|

|

|

|

low |

|

|

|

|

|

|

|

|

|

|

|||||||||||

th(CLW) |

CAS |

tWCH |

15 |

|

20 |

|

25 |

|

30 |

|

ns |

||||||||||||||||||

(see Note 11) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

th(RLW) |

Hold time, write after |

RAS |

low |

tWCR |

60 |

|

70 |

|

85 |

|

100 |

|

ns |

||||||||||||||||

(see Note 12) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

td(RLCH) |

Delay time, |

|

|

low to |

|

|

|

|

|

|

high |

tCSH |

80 |

|

100 |

|

120 |

|

150 |

|

ns |

||||||||

RAS |

CAS |

|

|

|

|

||||||||||||||||||||||||

td(CHRL) |

Delay time, |

|

|

high to |

|

|

|

|

|

|

low |

tCRP |

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||||||||

CAS |

RAS |

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

td(CLRH) |

Delay time, |

CAS |

low to |

RAS |

high |

tRSH |

20 |

|

25 |

|

30 |

|

40 |

|

ns |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

td(CLWL) |

Delay time, |

CAS |

low to |

W |

low |

tCWD |

20 |

|

25 |

|

40 |

|

50 |

|

ns |

||||||||||||||

(see Note 14) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

Delay time, |

|

|

low to |

|

|

|

|

|

|

low |

|

|

|

|

|

|

|

|

|

|

||||||||

td(RLCL) |

RAS |

CAS |

tRCD |

22 |

60 |

28 |

75 |

28 |

90 |

33 |

110 |

ns |

|||||||||||||||||

(see Note 15) |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

Delay time, |

|

|

low to column |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

td(RLCA) |

RAS |

tRAD |

17 |

40 |

20 |

55 |

20 |

65 |

25 |

80 |

ns |

||||||||||||||||||

address (see Note 15) |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

Delay time, column address to |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

td(CARH) |

RAS |

|

tRAL |

40 |

|

45 |

|

55 |

|

70 |

|

ns |

|||||||||||||||||

high |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

td(CACH) |

Delay time, column address to |

CAS |

|

tCAL |

40 |

|

45 |

|

55 |

|

70 |

|

ns |

||||||||||||||||

high |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

td(RLWL) |

Delay time, |

RAS |

low to |

W |

low |

tRWD |

80 |

|

100 |

|

130 |

|

160 |

|

ns |

||||||||||||||

(see Note 14) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

td(CAWL) |

Delay time, column address to |

W |

|

tAWD |

40 |

|

45 |

|

65 |

|

80 |

|

ns |

||||||||||||||||

low (see Note 14) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

Delay time, |

|

|

low to |

|

|

|

|

|

|

high |

|

|

|

|

|

|

|

|

|

|

||||||||

td(RLCH)R |

RAS |

CAS |

tCHR |

20 |

|

25 |

|

25 |

|

30 |

|

ns |

|||||||||||||||||

(see Note 16) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

td(CLRL)R |

Delay time, |

CAS |

low to |

RAS |

low |

tCSR |

10 |

|

10 |

|

10 |

|

15 |

|

ns |

||||||||||||||

(see Note 16) |

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

td(RHCL)R |

Delay time, |

|

|

high to |

|

|

|

|

|

|

low |

tRPC |

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||||||||

RAS |

CAS |

|

|

|

|

||||||||||||||||||||||||

trf |

Refresh time interval |

tREF |

|

8 |

|

8 |

|

8 |

|

8 |

ms |

||||||||||||||||||

tt |

Transition time (see Note 17) |

Ð |

Ð |

|

Ð |

|

Ð |

|

Ð |

|

ns |

||||||||||||||||||

NOTES: 5. Timing measurements in this table are referenced to VIL max and VIH min.

10.Referenced to the later of CAS or W in write operations.

11.Early-write operation only

12.The minimum value is measured when td(RLCL) is set td(RLCL) min as a reference.

13.Either th(RHrd) or th(CHrd) must be satisfied for a read cycle.

14.Read-modify-write operation only

15.Maximum value specified only to assure access time.

16.CBR refresh only

17.Transition times (rise and fall) for RAS and CAS are to be minimum of 3 ns and a maximum of 50 ns.

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

9 |

Loading...

Loading...