Texas Instruments SN65LVDS31-32, SN65LVDS31-32A, SN65LVDS31D, SN65LVDS31DR, SN65LVDS31NS Datasheet

...

SN55LVDS31, SN65LVDS31, SN65LVDS3487, SN65LVDS9638 HIGH-SPEED DIFFERENTIAL LINE DRIVERS

DMeets or Exceeds the Requirements of ANSI TIA/EIA-644 Standard

DLow-Voltage Differential Signaling With

Typical Output Voltage of 350 mV and a 100-Ω Load

DTypical Output Voltage Rise and Fall Times of 500 ps (400 Mbps)

DTypical Propagation Delay Times of 1.7 ns

DOperates From a Single 3.3-V Supply

DPower Dissipation 25 mW Typical per Driver at 200 MHz

DDriver at High Impedance When Disabled or With VCC = 0

DBus-Terminal ESD Protection Exceeds 8 kV

DLow-Voltage TTL (LVTTL) Logic Input Levels

DPin-Compatible With the AM26LS31, MC3487, and µA9638

description

The SN55LVDS31, SN65LVDS31, SN65LVDS3487, and SN65LVDS9638 are differential line drivers that implement the electrical characteristics of low-voltage differential signaling (LVDS). This signaling technique lowers the output voltage levels of 5 V differential standard levels (such as TIA/EIA-422B) to reduce the power, increase the switching speeds, and allow operation with a 3.3-V supply rail. Any of the four current-mode drivers will deliver a minimum differential output voltage magnitude of 247 mV into a 100-Ω load when enabled.

The intended application of these devices and signaling technique is for point-to-point baseband data transmission over controlled impedance media of approximately 100 Ω. The transmission media may be printed-circuit board traces, backplanes, or cables. The ultimate rate and distance of data transfer is dependent upon the attenuation characteristics of the media and the noise coupling to the environment.

SLLS261F ± JULY 1997 ± REVISED MARCH 2000

SN55LVDS31 . . . J OR W

SN65LVDS31D

(Marked as LVDS31 or 65LVDS31)

|

|

|

(TOP VIEW) |

|

|

|

|

|

|||||

|

1A |

|

|

|

|

|

|

|

|

VCC |

|

|

|

|

|

|

1 |

|

16 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||||

|

1Y |

|

|

2 |

|

15 |

|

|

4A |

|

|

||

|

|

|

|

|

|

|

|

||||||

|

1Z |

|

|

3 |

|

14 |

|

|

4Y |

|

|

||

|

|

|

|

|

|

|

|

||||||

|

G |

|

|

4 |

|

13 |

|

|

4Z |

|

|

||

|

|

|

|

|

|

|

|

||||||

|

2Z |

|

|

5 |

|

12 |

|

|

G |

|

|

|

|

|

2Y |

|

|

6 |

|

11 |

|

|

3Z |

|

|

||

|

|

|

|

|

|

|

|

||||||

|

2A |

|

|

7 |

|

10 |

|

|

3Y |

|

|

||

|

|

|

|

|

|

|

|

||||||

|

GND |

|

|

8 |

|

9 |

|

|

3A |

|

|

||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SN55LVDS31FK |

|

|

|||||||||

|

|

|

(TOP VIEW) |

|

|

|

|

|

|||||

|

1Y |

|

|

1A |

NC |

CC |

4A |

|

|

||||

|

|

|

V |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

3 |

2 |

1 |

20 |

|

19 |

|

|

|

||||

1Z |

4 |

|

|

|

|

|

|

|

18 |

4Y |

|||

G |

5 |

|

|

|

|

|

|

|

17 |

4Z |

|||

NC |

6 |

|

|

|

|

|

|

|

16 |

NC |

|||

2Z |

|

|

|

|

|

|

|

|

|

|

|||

7 |

|

|

|

|

|

|

|

15 |

G |

|

|||

2Y |

8 |

|

|

|

|

|

|

|

14 |

3Z |

|||

|

9 |

10 |

11 |

12 |

|

13 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

2A |

|

|

GND |

NC |

3A |

3Y |

|

|

||||

SN65LVDS3487D

(Marked as LVDS3487 or 65LVDS3487)

|

(TOP VIEW) |

|

|||

1A |

|

1 |

16 |

|

VCC |

|

|

||||

1Y |

|

2 |

15 |

|

4A |

|

|

||||

1Z |

|

3 |

14 |

|

4Y |

|

|

||||

1,2EN |

|

4 |

13 |

|

4Z |

|

|

||||

2Z |

|

5 |

12 |

|

3,4EN |

|

|

||||

2Y |

|

6 |

11 |

|

3Z |

|

|

||||

2A |

|

7 |

10 |

|

3Y |

|

|

||||

GND |

|

8 |

9 |

|

3A |

|

|

||||

|

|

|

|

|

|

SN65LVDS9638D (Marked as DK638 or LVDS38) SN65LVDS9638DGN (Marked as L38)

(TOP VIEW)

The |

SN65LVDS31, SN65LVDS3487, and |

VCC |

|

|

1 |

8 |

|

1Y |

|

|

|

||||||

SN65LVDS9638 are characterized for operation |

1A |

|

|

2 |

7 |

|

1Z |

|

from |

±40°C to 85°C. The SN55LVDS31 is |

|

|

|||||

2A |

|

|

3 |

6 |

|

2Y |

||

characterized for operation from ±55°C to 125°C. |

GND |

|

|

4 |

5 |

|

2Z |

|

|

|

|

||||||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 2000, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

SN55LVDS31, SN65LVDS31, SN65LVDS3487, SN65LVDS9638

HIGH-SPEED DIFFERENTIAL LINE DRIVERS

SLLS261F ± JULY 1997 ± REVISED MARCH 2000

AVAILABLE OPTIONS

|

|

|

PACKAGE |

|

|

TA |

|

|

|

|

|

SMALL OUTLINE |

MSOP |

CHIP CARRIER |

CERAMIC DIP |

FLAT PACK |

|

|

(D) |

(DGN) |

(FK) |

(J) |

(W) |

|

|

|

|

|

|

|

SN65LVDS31D |

Ð |

Ð |

Ð |

Ð |

± 40°C to 85°C |

|

|

|

|

|

SN65LVDS3487D |

Ð |

Ð |

Ð |

Ð |

|

|

|

|

|

|

|

|

SN65LVDS9638D |

SN65LVDS9638DGN |

Ð |

Ð |

Ð |

|

|

|

|

|

|

± 55°C to 125°C |

Ð |

Ð |

SN55LVDS31FK |

SN55LVDS31J |

SN55LVDS31W |

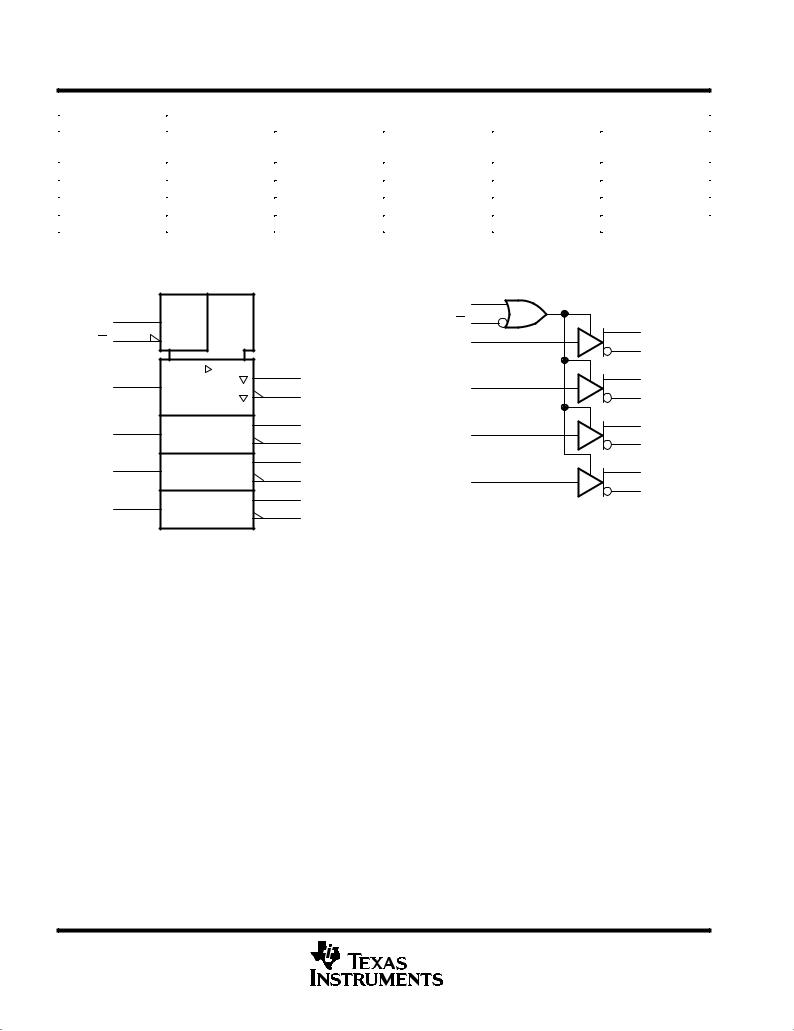

logic symbol² |

|

'LVDS31 logic diagram (positive logic) |

|||

|

SN55LVDS31, SN65LVDS31 |

|

|

|

|

|

≥ 1 |

|

4 |

|

|

4 |

|

G |

|

||

EN |

|

12 |

2 |

||

G |

|

G |

|||

12 |

|

|

1 |

1Y |

|

G |

|

|

1A |

3 |

|

|

|

|

|

1Z |

|

1 |

2 |

1Y |

7 |

6 |

|

|

2Y |

||||

1A |

3 |

1Z |

2A |

5 |

|

|

|

|

2Z |

||

7 |

6 |

2Y |

9 |

10 |

|

|

3Y |

||||

2A |

5 |

2Z |

3A |

11 |

|

|

10 |

|

3Z |

||

9 |

3Y |

|

14 |

||

11 |

15 |

||||

3A |

3Z |

4Y |

|||

|

14 |

4A |

13 |

||

15 |

4Y |

|

4Z |

||

|

|

|

|||

4A |

13 |

4Z |

|

|

|

|

|

|

|

||

²This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

|

|

|

|

|

SN55LVDS31, SN65LVDS31, SN65LVDS3487, SN65LVDS9638 |

|||||||||

|

|

|

|

|

|

|

HIGH-SPEED DIFFERENTIAL LINE DRIVERS |

|||||||

|

|

|

|

|

|

|

SLLS261F ± JULY 1997 ± REVISED MARCH 2000 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

logic symbol² |

|

|

|

|

|

'LVDS3487 logic diagram (positive logic) |

||||||||

|

|

|

SN65LVDS3487 |

|

|

|

|

|

|

|

|

|

||

4 |

|

|

|

|

|

|

|

|

2 |

|

|

|||

1, 2EN |

|

EN |

|

|

1 |

|

1Y |

|||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

2 |

|

1A |

|

|

3 |

1Z |

|||

|

|

|

|

|

|

|

||||||||

1 |

|

|

|

1Y |

4 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||

1A |

|

|

|

|

3 |

|

|

|

|

|

|

|

||

|

|

1Z |

1,2EN |

|

|

6 |

|

|

||||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

6 |

7 |

|

2Y |

||||||

7 |

|

|

|

2Y |

|

|||||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

2A |

5 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

||||||

2A |

|

|

|

5 |

2Z |

2Z |

||||||||

|

|

|

|

|

|

|

||||||||

12 |

|

|

|

|

9 |

|

10 |

3Y |

||||||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|||||||||

3, 4EN |

|

EN |

|

|

3A |

11 |

3Z |

|||||||

|

|

|

||||||||||||

9 |

|

|

|

10 |

3Y |

12 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

3,4EN |

|

|

|

|

|

|

||||

3A |

|

|

|

|

11 |

3Z |

15 |

|

14 |

4Y |

||||

|

|

|

|

|

14 |

|

|

|

|

|||||

15 |

|

4Y |

4A |

|

|

13 |

4Z |

|||||||

|

|

|

||||||||||||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||

4A |

|

|

13 |

4Z |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

²This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

logic symbol² |

|

|

'LVDS9638 logic diagram (positive logic) |

|||||

|

SN65LVDS9638 |

|

|

8 |

1Y |

|||

|

|

8 |

2 |

|||||

|

|

|

|

|

||||

2 |

|

1Y |

1A |

|

7 |

1Z |

||

|

|

|

||||||

1A |

|

7 |

|

|

|

|

|

|

|

|

1Z |

|

|

|

|

|

|

|

|

6 |

3 |

6 |

2Y |

|||

|

|

|||||||

3 |

|

2Y |

|

|

|

|||

2A |

|

5 |

2A |

|

5 |

2Z |

||

|

|

|||||||

|

|

2Z |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

²This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

SN55LVDS31, SN65LVDS31, SN65LVDS3487, SN65LVDS9638 HIGH-SPEED DIFFERENTIAL LINE DRIVERS

SLLS261F ± JULY 1997 ± REVISED MARCH 2000

Function Tables

SN55LVDS31, SN65LVDS31

|

INPUT |

|

|

ENABLES |

OUTPUTS |

||||||||

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

|

G |

Y |

Z |

|||||||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

H |

|

|

X |

H |

L |

||||

|

L |

|

|

H |

|

|

X |

L |

H |

||||

|

H |

|

|

X |

|

|

L |

H |

L |

||||

|

L |

|

|

X |

|

|

L |

L |

H |

||||

|

X |

|

|

L |

|

|

H |

Z |

Z |

||||

|

Open |

|

|

H |

|

|

X |

L |

H |

||||

|

Open |

|

|

X |

|

|

L |

L |

H |

||||

H = high level, |

L = low level, |

X = irrelevant, |

|||||||||||

Z = high impedance (off) |

|

|

|

|

|

|

|

||||||

|

|

|

|

SN65LVDS3487 |

|

|

|||||||

|

|

|

|

|

|

|

|

||||||

|

INPUT |

|

ENABLE |

|

OUTPUTS |

|

|||||||

|

A |

|

EN |

|

|

|

|

Y |

Z |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

H |

|

H |

|

|

|

|

H |

L |

|

|||

|

L |

|

H |

|

|

|

|

L |

H |

|

|||

|

X |

|

L |

|

|

|

|

Z |

Z |

|

|||

|

OPEN |

|

H |

|

|

|

|

L |

H |

|

|||

|

H = high level, |

L = low level, |

X = irrelevant, |

||||||||||

|

Z = high impedance (off) |

|

|

|

|||||||||

|

|

|

|

SN65LVDS9638 |

|

|

|||||||

|

|

|

|

|

|

||||||||

|

|

INPUT |

|

OUTPUTS |

|

|

|||||||

|

|

|

A |

|

|

|

Y |

Z |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

H |

|

|

|

H |

L |

|

|

|||

|

|

|

L |

|

|

|

L |

H |

|

|

|||

|

|

OPEN |

|

|

L |

H |

|

|

|||||

|

|

H = high level, |

L = low level |

|

|

||||||||

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

SN55LVDS31, SN65LVDS31, SN65LVDS3487, SN65LVDS9638

HIGH-SPEED DIFFERENTIAL LINE DRIVERS

|

|

|

|

SLLS261F ± JULY 1997 ± REVISED MARCH 2000 |

|

|

|

|

|

|

|

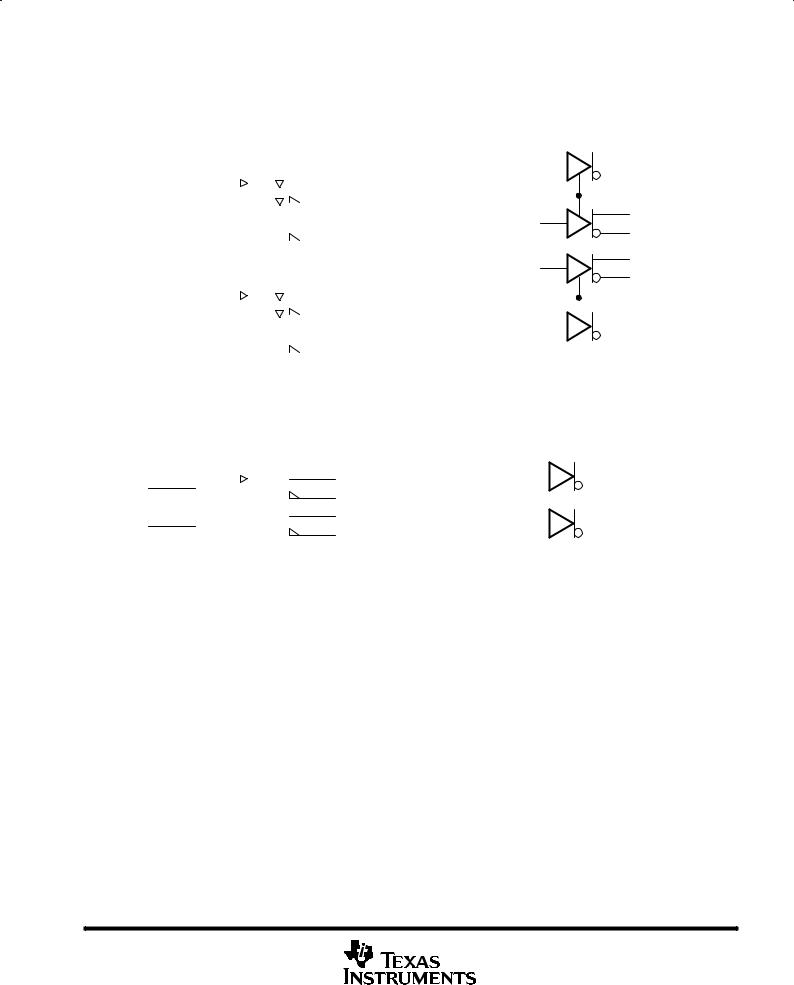

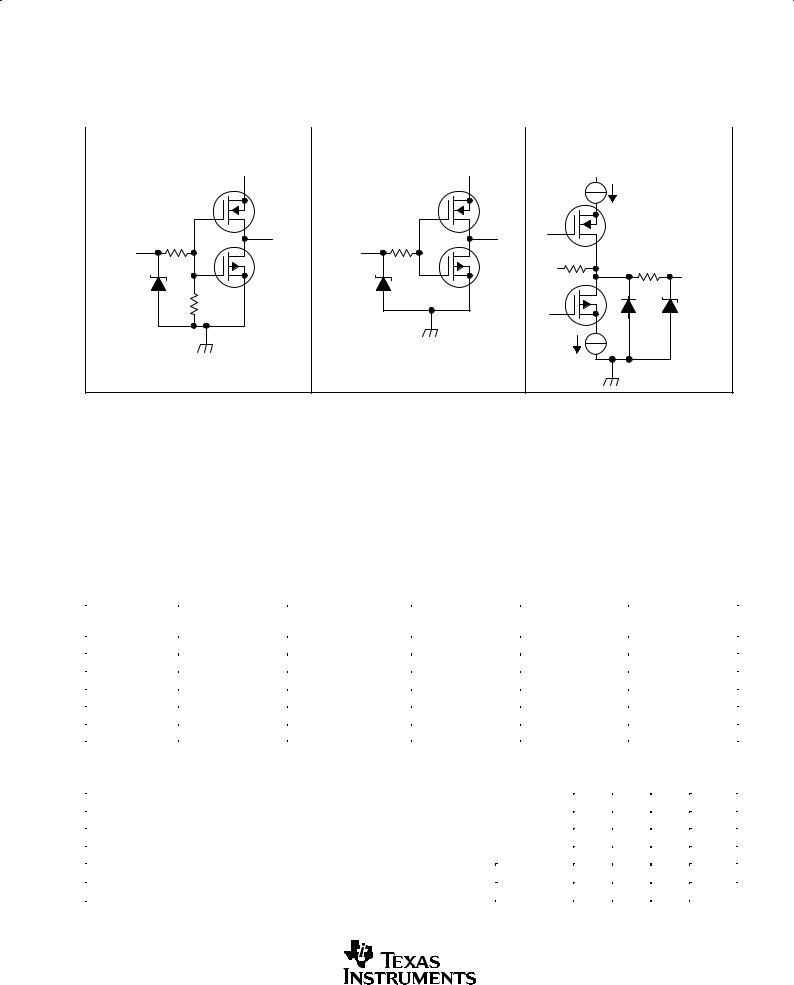

equivalent input and output schematic diagrams |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

EQUIVALENT OF EACH A INPUT |

EQUIVALENT OF G, |

G, 1,2EN OR |

TYPICAL OF ALL OUTPUTS |

||

|

3,4EN INPUTS |

|

|

||

V |

|

|

V |

VCC |

|

CC |

|

|

CC |

|

|

50 Ω |

|

50 Ω |

|

Input |

Input |

10 kΩ |

Ω |

|

|

||

|

|

5 |

|

|

|

|

Y or Z |

7 V |

7 V |

|

Output |

300 kΩ |

|

|

7 V |

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage range, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.5 V to 4 V Input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.5 V to VCC + 0.5 V Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . See Dissipation Rating Table

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±65_C to 150°C Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C

² Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages, except differential I/O bus voltages, are with respect to the network ground terminal.

DISSIPATION RATING TABLE

|

T ≤ 25°C |

DERATING FACTOR³ |

T = 70°C |

T = 85°C |

T = 125°C |

|

PACKAGE |

A |

ABOVE TA = 25°C |

A |

A |

A |

|

POWER RATING |

POWER RATING |

POWER RATING |

POWER RATING |

|||

|

||||||

D (8) |

725 mW |

5.8 mW/°C |

464 mW |

377 mW |

Ð |

|

|

|

|

|

|

|

|

D (16) |

950 mW |

7.6 mW/°C |

608 mW |

494 mW |

Ð |

|

|

|

|

|

|

|

|

DGN |

2.14 W |

17.1 mW/°C |

1.37 W |

1.11 W |

Ð |

|

FK |

1375 mW |

11.0 mW/°C |

880 mW |

715 mW |

275 mW |

|

|

|

|

|

|

|

|

J |

1375 mW |

11.0 mW/°C |

880 mW |

715 mW |

275 mW |

|

W |

1000 mW |

8.0 mW/°C |

640 mW |

520 mW |

200 mW |

³ This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

recommended operating conditions

|

|

MIN |

NOM |

MAX |

UNIT |

|

|

|

|

|

|

|

|

Supply voltage, VCC |

|

3 |

3.3 |

3.6 |

V |

|

High-level input voltage, VIH |

|

2 |

|

|

V |

|

Low-level input voltage, VIL |

|

|

|

0.8 |

V |

|

Operating free-air temperature, TA |

SN65 prefix |

± 40 |

|

85 |

°C |

|

|

|

|

|

|

||

SN55 prefix |

± 55 |

|

125 |

|

||

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

5 |

SN55LVDS31, SN65LVDS31, SN65LVDS3487, SN65LVDS9638

HIGH-SPEED DIFFERENTIAL LINE DRIVERS

SLLS261F ± JULY 1997 ± REVISED MARCH 2000

SN65LVDSxxxx electrical characteristics over recommended operating conditions (unless otherwise noted)

|

|

|

|

|

|

SN65LVDS31, |

|

||

|

PARAMETER |

TEST CONDITIONS |

'3487, ' 9638 |

UNIT |

|||||

|

|

|

|

|

|

MIN |

TYP² |

MAX |

|

VOD |

Differential output voltage magnitude |

|

|

|

247 |

340 |

454 |

mV |

|

|

|

|

RL = 100 Ω, |

See Figure 2 |

|

|

|

|

|

VOD |

Change in differential output voltage magnitude |

± 50 |

|

50 |

mV |

||||

between logic states |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

VOC(SS) |

Steady-state common-mode output voltage |

See Figure 3 |

|

1.125 |

1.2 |

1.375 |

mV |

||

VOC(SS) |

Change in steady-state common-mode output voltage |

|

|

|

±50 |

|

50 |

V |

|

between logic states |

See Figure 3 |

|

|

||||||

|

|

|

|

|

|

||||

VOC(PP) |

Peak-to-peak common-mode output voltage |

|

|

|

|

50 |

150 |

mV |

|

|

|

|

VI = 0.8 V or 2 V, |

Enabled, |

|

9 |

20 |

mA |

|

|

|

|

No load |

|

|

||||

|

|

SN65LVDS31, |

|

|

|

|

|

||

|

|

VI = 0.8 or 2 V, |

RL = 100 Ω, |

|

|

|

|

||

|

|

'3487 |

|

25 |

35 |

mA |

|||

ICC |

Supply current |

Enabled |

|

|

|||||

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

|

VI = 0 or VCC, |

Disabled |

|

0.25 |

1 |

mA |

|||

|

|

|

|

||||||

|

|

SN65LVDS9638 |

VI = 0.8 V or 2 V |

|

No load |

|

4.7 |

8 |

mA |

|

|

|

|

|

|

|

|

||

|

|

|

RL = 100 Ω |

|

9 |

13 |

mA |

||

|

|

|

|

|

|

||||

IIH |

High-level input current |

VIH = 2 |

|

|

4 |

20 |

µA |

||

IIL |

Low-level input current |

VIL = 0.8 V |

|

|

0.1 |

10 |

µA |

||

IOS |

Short-circuit output current |

VO(Y) or VO(Z) = 0 |

|

|

± 4 |

± 24 |

mA |

||

VOD = 0 |

|

|

|

± 12 |

mA |

||||

|

|

|

|

|

|

||||

IOZ |

High-impedance output current |

VO = 0 or 2.4 V |

|

|

|

± 1 |

µA |

||

IO(OFF) |

Power-off output current |

VCC = 0, |

VO = 2.4 V |

|

|

± 1 |

µA |

||

CI |

Input capacitance |

|

|

|

|

3 |

|

pF |

|

² All typical values are at TA = 25°C and with VCC = 3.3 V.

SN65LVDSxxxx switching characteristics over recommended operating conditions (unless otherwise noted)

|

|

|

SN65LVDS31, |

|

||

|

PARAMETER |

TEST CONDITIONS |

'3487, ' 9638 |

|

UNIT |

|

|

|

|

MIN |

TYP² |

MAX |

|

tpLH |

Propagation delay time, low-to-high-level output |

|

0.5 |

1.4 |

2 |

ns |

tpHL |

Propagation delay time, high-to-low-level output |

|

1 |

1.7 |

2.5 |

ns |

tr |

Differential output signal rise time (20% to 80%) |

RL = 100 Ω, CL = 10 pF, |

0.4 |

0.5 |

0.6 |

ns |

tf |

Differential output signal fall time (80% to 20%) |

See Figure 2 |

0.4 |

0.5 |

0.6 |

ns |

tsk(p) |

Pulse skew (|tPHL ± tPLH|) |

|

|

0.3 |

0.6 |

ns |

t |

Channel-to-channel output skew³ |

|

|

0 |

0.3 |

ns |

sk(o) |

|

|

|

|

|

|

t |

Part-to-part skew§ |

|

|

|

800 |

ps |

sk(pp) |

|

|

|

|

|

|

tpZH |

Propagation delay time, high-impedance-to-high-level output |

|

|

5.4 |

15 |

ns |

tpZL |

Propagation delay time, high-impedance-to-low-level output |

See Figure 4 |

|

2.5 |

15 |

ns |

tpHZ |

Propagation delay time, high-level-to-high-impedance output |

|

8.1 |

15 |

ns |

|

|

|

|||||

tpLZ |

Propagation delay time, low-level-to-high-impedance output |

|

|

7.3 |

15 |

ns |

² All typical values are at TA = 25°C and with VCC = 3.3 V.

³tsk(o) is the skew between specified outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical specified loads.

§tsk(pp) is the magnitude of the different in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, same temperature, and have identical packages and test circuits.

6 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...