Texas Instruments SM320C40GFM33, SM320C40GFM40, SM320C40GFM50, SM320C40GFS60, SM320C40HFHM33 Datasheet

...

A A E

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

SMJ: QML Processing to MIL±PRF±38535

SM: Standard Processing

TMP: Commercial Level Processing TAB

Operating Temperature Ranges:

±Military (M) ±55°C to 125°C

±Special (S) ±55°C to 100°C

±Commercial (C) ±25°C to 85°C

±Commercial (L) 0°C to 70°C

Highest Performance Floating-Point Digital Signal Processor (DSP)

±'C40-60:

33-ns Instruction Cycle Time:

60 MFLOPS, 30 MIPS, 330 MOPS,

384 MBps

±'C40-50:

40-ns Instruction Cycle Time:

50 MFLOPS, 25 MIPS, 275 MOPS,

320 MBps

±'C40-40:

50-ns Instruction Cycle Time:

40 MFLOPS, 20 MIPS, 220 MOPS,

256 MBps

Six Communications Ports

6-Channel Direct Memory Access (DMA) Coprocessor

Single-Cycle Conversion to and From IEEE-745 Floating-Point Format

Single Cycle 1/x, 1/ x

Source-Code Compatible With SMJ320C30

Validated Ada Compiler

Single-Cycle 40-Bit Floating-Point, 32-Bit Integer Multipliers

12 40-Bit Registers, 8 Auxiliary Registers,

14 Control Registers, and 2 Timers

IEEE Standard 1149.1² Test-Access Port (JTAG)

Two Identical External Data and Address Buses Supporting Shared Memory Systems and High Data-Rate, Single-Cycle Transfers:

±High Port-Data Rate of 100 MBytes/s (Each Bus)

±16G-Byte Continuous Program/Data/Peripheral Address Space

±Memory-Access Request for Fast, Intelligent Bus Arbitration

±Separate Address-, Data-, and Control-Enable Pins

±Four Sets of Memory-Control Signals Support Different Speed Memories in Hardware

Packaging:

±325-Pin Ceramic Grid Array (GF Suffix)

±352-Lead Ceramic Quad Flatpack (HFH Suffix)

±324-Pad JEDEC-Standard TAB Frame

Fabricated Using 0.72- m Enhanced Performance Implanted CMOS (EPIC ) Technology by Texas Instruments (TI )

Separate Internal Program, Data, and DMA Coprocessor Buses for Support of Massive Concurrent Input/Output (I/O) of Program and Data Throughput, Maximizing Sustained Central Processing Unit (CPU) Performance

On-Chip Program Cache and Dual-Access/Single-Cycle RAM for Increased Memory-Access Performance

±512-Byte Instruction Cache

±8K Bytes of Single-Cycle Dual-Access Program or Data RAM

±ROM-Based Bootloader Supports Program Bootup Using 8-, 16-, or 32-Bit Memories Over Any One of the Communications Ports

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

² IEEE Standard 1149.1-1990, IEEE Standard Test-Access Port and Boundary-Scan Architecture. EPIC and TI are trademarks of Texas Instruments Incorporated.

A A |

#& ')% +#'& #* |

,)) &+ |

* |

' |

(, $# +#'& + |

|||

)' , +* |

'& ')% |

+' |

*( # # +#'&* |

( ) |

+" |

+ )%* |

' |

. * &*+),% &+* |

*+ & ) |

- )) &+/ |

)' , +#'& ()' **#&! |

' * &'+ |

& ** )#$/ #& $, |

||||

+ *+#&! ' |

$$ ( ) % + )* |

|

|

|

|

|

||

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443

Copyright 2000, Texas Instruments Incorporated

& ()' , +* '%($# &+ +' 0 0 8 |

$$ |

( ) % + )* |

) + *+ |

||

,&$ ** '+" )-#* |

&'+ & |

$$ '+" ) |

()' , +* |

()' , +#'& |

|

()' **#&! ' * |

&'+ & ** )#$/ |

#& $, |

+ *+#&! ' $$ |

( ) % + )* |

|

|

|

|

|

|

1 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

description

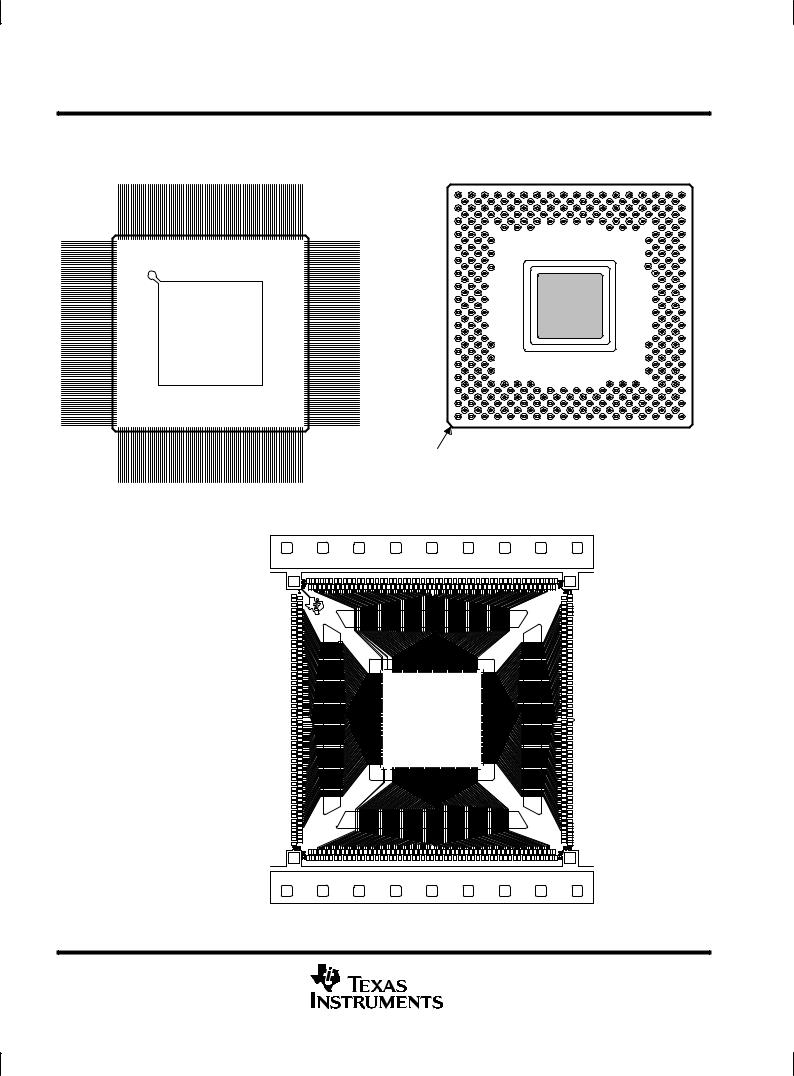

352-LEAD HFH QUAD FLATPACK PACKAGE |

|

|

325-PIN GF GRID ARRAY PACKAGE |

|

|

|

|||||||||||||||||||||||

(TOP VIEW)² |

|

|

|

|

|

|

|

(BOTTOM VIEW)² |

|

|

|

|

|

|

|

|

|

||||||||||||

352 |

265 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

264 |

AK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AJ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AG |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

88 |

177 |

|

2 |

4 |

6 |

8 |

10 |

12 |

14 |

16 |

18 |

20 |

22 |

24 |

26 |

28 |

30 32 |

34 |

|||||||||||

|

|

1 |

3 |

5 |

7 |

9 |

11 |

13 |

15 |

17 |

19 |

21 |

23 |

25 |

27 |

29 31 |

33 |

35 |

|||||||||||

|

|

Pin A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

89 |

176 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TAB 325-LEAD OLB/ILB

TAPE AUTOMATED BONDING (TAB) PACKAGE

(TOP VIEW)²

1

² See the pin assignments tables and the signal description table for location and description of all pins.

2 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

description (continued)

The '320C40 digital signal processors (DSPs) are 32-bit, floating-point processors manufactured in 0.72- m, double-level metal CMOS technology. The '320C40 is a part of the fourth-generation DSPs from Texas Instruments and is designed primarily for parallel processing.

operation

The '320C40 has six on-chip communication ports for processor-to-processor communication with no external hardware and simple communication software. This allows connectivity to other 'C4x processors with no external-glue logic. The communication ports remove input/output bottlenecks, and the independent smart DMA coprocessor is able to handle the CPU input/output burden.

central processing unit

The '320C40 CPU is configured for high-speed internal parallelism for the highest sustained performance. The key features of the CPU are:

Eight operations/cycle:

±40/32-bit floating-point/integer multiply

±40/32-bit floating-point/integer arithmetic logic unit (ALU) operation

±Two data accesses

±Two address-register updates

IEEE floating-point conversion

Divide and square-root support

'C3x assembly language compatibility

Byte and halfword accessibility

DMA coprocessor

The DMA coprocessor allows concurrent I/O and CPU processing for the highest sustained CPU performance. The key features of the DMA processor are:

Link pointers that allow DMA channels to autoinitialize without CPU intervention

Parallel CPU operation and DMA transfers

Six DMA channels that support memory-to-memory data transfers

Split-mode operation doubles the available DMA channels to 12 when data transfers to and from a communication port are required.

communication ports

The '320C40 is the first DSP with on-chip communication ports for processor-to-processor communication with no external hardware and simple communication software. The features of the communication ports are:

Direct interprocessor communication and processor I/O

Six communication ports for direct interprocessor communication and processor I/O

20M-byte/s bidirectional interface on each communication port for high-speed multiprocessor interface

Separate 8-word-deep input and output FIFO buffers for processor-to-processor communication and I/O

Automatic arbitration and handshaking for direct processor-to-processor connection

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

3 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

communication-port software reset ('C40 silicon revision ≥ 5.0)

The input and output FIFO levels for a communication port can be flushed by writing at least two back-to-back values to its communication-port software-reset address as specified in Table 1. This feature is not present in 'C40 silicon revision < 5.0. This software reset flushes any word or byte already present in the FIFOs but it does not affect the status of the communication-port pins. Figure 1 shows an example of communication-port-software reset.

Table 1. Communication-Port Software-Reset Address

0 |

0x0100043 |

|

|

1 |

0x0100053 |

|

|

2 |

0x0100063 |

|

|

3 |

0x0100073 |

|

|

4 |

0x0100083 |

|

|

5 |

0x0100093 |

;±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±-±±±;

;RESET1:Flush's FIFO data for communication port 1;

;±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±-±±±;

RESET1 push |

AR0 |

; |

Save registers |

push |

R0 |

; |

|

push |

RC |

; |

|

ldhi |

010h,AR0 |

; Set AR0 to base address of COM 1 |

|

or |

050h,AR0 |

; |

|

flush: rpts |

1 |

; Flush FIFO data with back-to-back write |

|

sti |

R0,*+AR0(3) |

; |

|

rpts |

10 |

; |

Wait |

nop |

|

; |

|

ldi |

*+AR0(0),R0 |

; Check for new data from other port |

|

and |

01FE0h,R0 |

; |

|

bnz |

flush |

; |

|

pop |

RC |

; |

Restore registers |

pop |

R0 |

; |

|

pop |

AR0 |

; |

|

rets |

|

; |

Return |

Figure 1. Example of Communication-Port-Software Reset

4 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

NMI with bus-grant feature ('C40 silicon revision ≥ 5.0)

The '320C40 devices have a software-configurable feature that forces the internal-peripheral bus to ready when the NMI signal is asserted. This feature is not present in 'C40 silicon revision < 5.0. The NMI bus-grant feature is enabled when bits 19±18 of the status register (ST) are set to 10b. When enabled, a peripheral bus-grant signal is generated on the falling edge of NMI. When NMI is asserted and this feature is not enabled, the CPU stalls on access to the peripheral bus if it is not ready. A stall condition occurs when writing to a full FIFO or reading an empty FIFO. This feature is useful in correcting communication-port errors when used in conjunction with the communication-port software-reset feature.

IDLE2 clock-stop power-down mode ('C40 silicon revision ≥ 5.0)

The '320C40 has a clock-stop mode or power-down mode (IDLE2) to achieve extremely low power consumption. When an IDLE2 instruction is executed, the clocks are halted with H1 being held high. To exit IDLE2, assert one of the IIOF3±IIOF0 pins configured as an external interrupt instead of a general-purpose I/O. A macro showing how to generate the IDLE2 opcode is given in Figure 2. During this power-down mode:

No instructions are executed

The CPU, peripherals, and internal memory retain their previous state.

The external-bus outputs are idle. The address lines remain in their previous state, the data lines are in the high-impedance state, and the output-control signals are inactive.

;±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±-±-±;

; IDLE2: Macro to generate idle2 opcode |

; |

; ±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±±-±±;

IDLE2 .macro

.word 06000001h

.endm

Figure 2. Example of Software Subroutine Using IDLE2

IDLE2 is exited when one of the five external interrupts (NMI and IIOF3±IIOF0) is asserted low for at least four input clocks (two H1 cycles). The clocks then start after a delay of two input clocks (one H1 cycle). The clocks can start in the opposite phase; that is, H1 can be high when H3 was high before the clocks were stopped. However, the H1 and H3 clocks remain 180° out of phase with each other.

During IDLE2 operation, an external interrupt can be recognized and serviced by the CPU if it is enabled before entering IDLE2 and asserted for at least two H1 cycles. For the processor to recognize only one interrupt, the interrupt pin must be configured for edge-trigger mode or asserted less than three cycles in level-trigger mode. Any external interrupt pin can wake up the device from IDLE2, but for the CPU to recognize that interrupt, it must also be enabled. If an interrupt is recognized and executed by the CPU, the instruction following the IDLE2 instruction is not executed until after execution of a return opcode.

When the device is in emulation mode, the CPU executes an IDLE2 instruction as if it were an IDLE instruction. The clocks continue to run for correct operation of the emulator.

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

5 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

development tools

The 'C40 is supported by a host of parallel-processing development tools for developing and simulating code easily and for debugging parallel-processing systems. The code generation tools include:

An ANSI C compiler optimized with a runtime support library that supports use of communication ports and DMA.

Third-party support for C, C++, and Ada compilers

Several operating systems available for parallel-processing support, as well as DMA and communication port drivers

An assembler and linker with support for mapping program and data to parallel processors

The simulation tools include:

Parallel DSP system-level simulation with LAI hardware verification (HV) model and full function (FF) model

TI software simulator with high-level language debugger interface for simulating a single processor

The hardware development and verification tools include:

Parallel processor in-circuit emulator and high-level language debugger: XDS510

Parallel processor development system (PPDS) with four '320C40s, local and global memory, and communication port connections

XDS510 is a trademark of Texas Instruments Incorporated.

6 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ320C40 TMP320C40 DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

block diagram

D31±D0

A30±A0 DE

DE  AE

AE

STAT3±STAT0 LOCK

LOCK STRB0,STRB1

STRB0,STRB1 R/W0,RW1

R/W0,RW1 PAGE0,PAGE1

PAGE0,PAGE1 RDY0,RDY1

RDY0,RDY1  CE0,CE1

CE0,CE1

X1

X2/CLKIN

ROMEN

RESET

RESETLOC0,

RESETLOC1

NMI

IIOF3±IIOF0

IACK

H1

H3

CVSS

DVDD

DVSS

IVSS

LADVDD

LDDVDD

VDDL

VSSL

SUBS

|

Cache |

RAM Block 0 |

RAM Block 1 |

ROM Block |

|||

(512 Bytes) |

|

(4K Bytes) |

(4K Bytes) |

(Reserved) |

|||

32 |

32 |

32 |

32 |

32 |

32 |

32 |

32 |

PDATA Bus

PADDR Bus

DDATA Bus

M

U DADDR 1 Bus

X

DADDR 2 Bus

DMADATA Bus

DMAADDR Bus

32 |

32 |

32 |

32 |

32 |

IR

PC |

MUX |

|

|

|

|

|

CPU1 |

|

|

|

|

|

|

CPU2 |

|

|

C |

|

|

|

REG11 |

|

|

|

|

|

|

|

|

|

o |

C |

R |

R |

REG2 |

|

|

n |

|

|

||||

P |

E |

E |

|

|

||

t |

|

|

|

|||

U |

G |

G |

|

|

|

|

r |

|

|

|

|||

1 |

1 |

2 |

|

|

|

|

o |

|

|

|

|||

|

|

40 |

40 |

40 |

40 |

|

l |

|

|

||||

|

|

|

|

32-Bit Barrel |

||

l |

|

|

Multiplier |

|||

e |

|

|

Shifter |

|

||

|

|

|

|

|

||

r |

|

|

|

|

ALU |

|

40 |

40 |

|

40 |

|

|

|

|||

|

|

40 |

||

40 |

Extended |

|||

|

||||

Precision |

|

|||

|

40 |

|||

32 |

Registers |

|||

|

(R0±R11) |

|

||

|

DISP, IR0, IR1 |

|

||

|

ARAU0 |

ARAU1 |

||

|

|

BK |

|

|

Continued on next page

32 |

|

32 |

|

|

|

||

32 |

Auxiliary |

32 |

|

32 |

Registers |

32 |

|

32 |

(AR0±AR7) |

||

|

|||

|

|

||

32 |

|

32 |

|

|

Other |

||

32 |

|

||

Registers |

|

||

|

(14) |

|

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

7 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

block diagram (continued)

page |

PDATA Bus |

|

|

|

|

|

|

|

|

LD31±LD0 |

|

|

|

|

|

|

|

|

|

||

PADDR Bus |

|

|

|

|

|

|

|

|

LA30±LA0 |

|

previous |

|

|

|

|

|

|

|

|

LDE |

|

|

|

|

|

|

|

|

|

|

||

DDATA Bus |

|

|

|

|

|

|

|

|

LAE |

|

|

|

|

|

|

|

|

|

LSTAT3±LSTAT0 |

||

|

|

|

|

|

|

M |

|

|

||

|

|

|

|

|

|

|

|

LLOCK |

||

DADDR 1 Bus |

|

|

|

|

|

U |

|

|

||

from |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

X |

|

|

LSTRB0±LSTRB1 |

|

DADDR 2 Bus |

|

|

|

|

|

|

|

|

LR/W0±LR/W1 |

|

Continued |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

LPAGE0±LPAGE1 |

||

|

|

|

|

|

|

|

|

|

||

DMADATA Bus |

|

|

|

|

|

|

|

|

LRDY0±LRDY1 |

|

|

|

|

|

|

|

|

|

|

LCE0, LCE1 |

|

DMAADDR Bus |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

32 |

|

MUX |

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

||

|

|

|

|

|

COM Port 0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

32 |

Input |

|

CREQ0 |

|

|

|

|

|

32 |

|

|

FIFO |

|

CACK0 |

|

|

|

DMA Coprocessor |

|

32 |

Output |

PAU |

CSTRB0 |

|

Ports |

||

|

|

|

|

CRDY0 |

|

|||||

|

DMA Channel 0 |

|

|

|

FIFO |

|

|

|||

|

|

|

32 |

|

C0D7±C0D0 |

|||||

|

|

|

Port Control Registers |

Communication |

||||||

|

DMA Channel 1 |

|

|

|

|

|

||||

|

DMA Channel 2 |

|

P |

|

|

|

|

|

||

|

DMA Channel 3 |

32 |

e |

|

|

|

|

|

||

|

r |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

|

DMA Channel 4 |

P |

i |

32 |

COM Port 5 |

|

|

|||

|

DMA Channel 5 |

e |

p |

|

|

|

||||

|

r |

h |

32 |

Input |

|

CREQ5 |

|

|||

|

|

|

|

|

||||||

|

|

|

i |

e |

|

CACK5 |

|

Six |

||

|

|

|

|

FIFO |

|

|

||||

|

|

|

p |

r |

32 |

|

PAU |

CSTRB5 |

|

|

|

Six DMA Channels |

h |

a |

Output |

|

|

||||

|

|

|

CRDY5 |

|

|

|||||

|

|

|

e |

l |

32 |

FIFO |

|

C5D7±C5D0 |

||

|

|

|

r |

A |

Port Control Registers |

|||||

|

|

|

a |

|

|

|

|

|||

|

|

|

l |

d |

32 |

|

|

|

|

|

|

|

|

|

d |

|

Timer 0 |

|

|

|

|

|

|

|

D |

r |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

a |

e |

32 |

Global Control Register |

|

|

|

|

|

|

|

t |

s |

|

Time Period Register |

|

TCLK0 |

||

|

|

|

a |

s |

|

|

|

|

||

|

|

|

|

Timer Counter Register |

|

|

|

|||

|

|

|

|

|

32 |

|

|

|

||

|

|

|

B |

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

u |

u |

|

Timer 1 |

|

|

|

|

|

|

|

s |

s |

32 |

Global Control Register |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

Time Period Register |

TCLK1 |

|

Timer Counter Register |

|

32 |

Port Control |

|

|

Global |

|

32 |

Local |

|

|

|

8 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

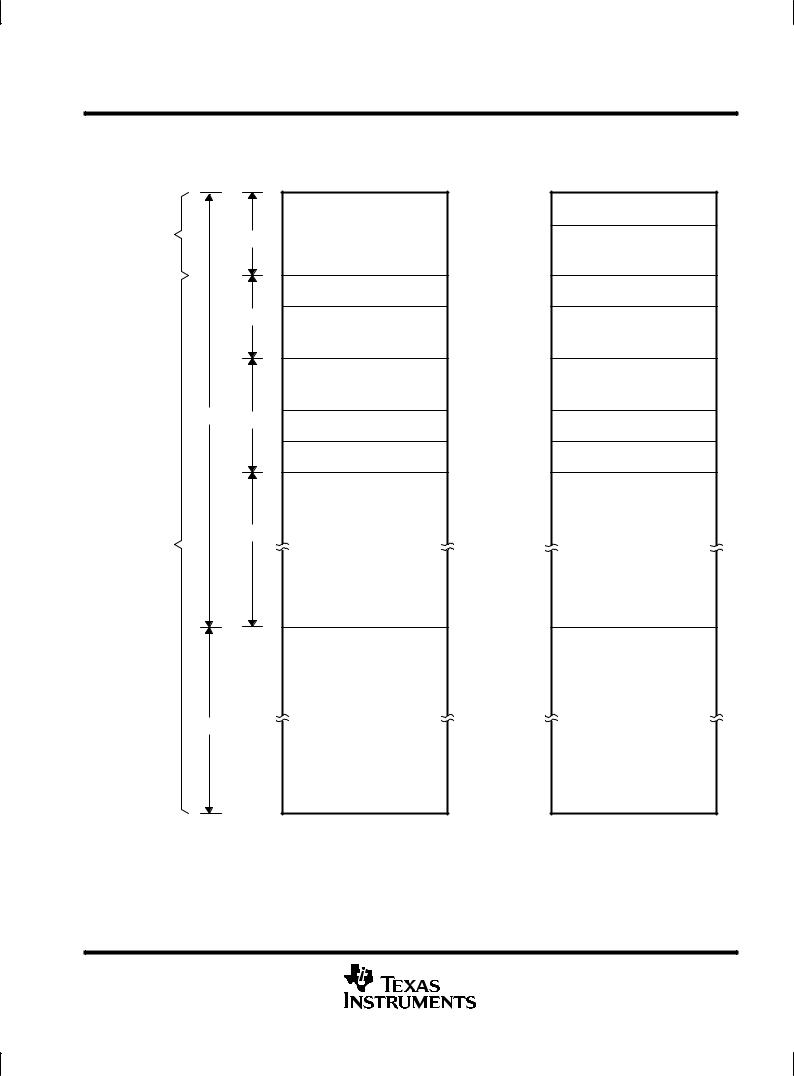

memory map

Figure 3 shows the memory map for the '320C40. See the TMS320C4x User's Guide (literature number SPRU063) for a detailed description of this memory mapping.

Structure |

|

Accessible Local Bus |

|

Depends |

1M |

||

(External) |

|||

Upon |

|||

|

|

||

ROMEN Bit |

|

|

Peripherals (Internal)

1M |

Reserved

|

|

|

Reserved |

|

2G |

1M |

1K RAM BLK 0 (Internal) |

|

|

||

|

|

|

|

|

|

|

1K RAM BLK 1 (Internal) |

Structure |

|

2G±3M |

|

|

|

Local Bus |

|

Identical |

|

|

|

|

|

|

(External) |

|

2G |

|

Global Bus (External) |

|

|

|

(a) Internal ROM Disabled

(ROMEN = 0)

Microprocessor Mode

000000000h

000000FFFh

000001000h

0000FFFFFh

000100000h

0001000FFh

000100100h

0001FFFFFh

000200000h

0002FF7FFh

0002FF800h

0002FFBFFh

0002FFC00h

0002FFFFFh

000300000h

07FFFFFFFh

080000000h

0FFFFFFFFh

Boot-Loader ROM

(Internal)

Reserved

Peripherals (Internal)

Reserved

Reserved

1K RAM BLK 0 (Internal)

1K RAM BLK 1 (Internal)

Local Bus

(External)

Global Bus (External)

(b) Internal ROM Enabled

(ROMEN = 1)

Microcomputer Mode

Figure 3. Memory Map for '320C40

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

9 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

signal descriptions

This section gives signal descriptions for the SMJ320C40 device. The SMJ320C40 signal descriptions table lists each signal, the number of pins, operating mode(s) (that is, input, output, or high-impedance state as indicated by I, O, or Z, respectively), and function. All pins labeled NC are not to be connected by the user. A line over a signal name (for example, RESET) indicates that the signal is active low (true at a logic-0 level). The signals are grouped according to functions.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SMJ320C40 Signal Descriptions |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGNAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NAME |

NO. OF |

TYPE² |

|

|

|

|

|

|

|

|

|

|

|

|

DESCRIPTION |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

PINS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GLOBAL BUS EXTERNAL INTERFACE (80 PINS) |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D31±D0 |

32 |

I/O/Z |

|

32-bit data port of the global bus external interface |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Data-bus-enable signal for the global bus external interface |

|||||||||||||||

|

DE |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A30±A0 |

31 |

O/Z |

|

31-bit address port of the global bus external interface |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Address-bus-enable signal for the global bus external interface |

|||||||||||||||

|

AE |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

STAT3±STAT0 |

4 |

O |

|

Status signals for the global bus external interface |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

O |

|

Lock signal for the global bus external interface |

|||||||||||||||

|

LOCK |

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

³ |

|

1 |

O/Z |

|

Access strobe 0 for the global bus external interface |

||||||||||||||||

|

STRB0 |

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

³ |

|

|

1 |

O/Z |

|

Read/write signal for |

|

|

|

|

|

|

accesses |

||||||||||||||

|

R/W0 |

|

STRB0 |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

PAGE0³ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

1 |

O/Z |

|

Page signal for |

STRB0 |

accesses |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

³ |

|

|

1 |

I |

|

Ready signal for |

|

|

|

|

|

accesses |

|||||||||||

|

RDY0 |

|

STRB0 |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

³ |

|

|

|

|

1 |

I |

|

Control enable for the |

|

|

|

|

|

|

|

|

|

|

signals |

|||||||

|

CE0 |

|

STRB0, |

|

PAGE0, and R/W0 |

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

³ |

|

1 |

O/Z |

|

Access strobe 1 for the global bus external interface |

||||||||||||||||

|

STRB1 |

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

³ |

|

|

1 |

O/Z |

|

Read/write signal for |

|

|

|

|

|

|

accesses |

||||||||||||||

|

R/W1 |

|

STRB1 |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

PAGE1³ |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

1 |

O/Z |

|

Page signal for |

STRB1 |

accesses |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

³ |

|

|

1 |

I |

|

Ready signal for |

|

|

|

|

|

accesses |

|||||||||||

|

RDY1 |

|

STRB1 |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

³ |

|

|

|

|

1 |

I |

|

Control enable for the |

|

|

|

|

|

|

|

|

|

|

signals |

|||||||

|

CE1 |

|

STRB1, |

|

PAGE1, and R/W1 |

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOCAL BUS EXTERNAL INTERFACE (80 PINS) |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

LD31±LD0 |

32 |

I/O/Z |

|

32-bit data port of the local bus external interface |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Data-bus-enable signal for the local bus external interface |

|||||||||||||||

|

LDE |

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

LA30±LA0 |

31 |

O/Z |

|

31-bit address port of the local bus external interface |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Address-bus-enable signal for the local bus external interface |

|||||||||||||||

|

LAE |

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

LSTAT3±LSTAT0 |

4 |

O |

|

Status signals for the local bus external interface |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

O |

|

Lock signal for the local bus external interface |

|||||||||||||||

|

LLOCK |

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

³ |

1 |

O/Z |

|

Access strobe 0 for the local bus external interface |

|||||||||||||||

|

LSTRB0 |

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

O/Z |

|

Read/write signal for |

|

|

|

|

|

|

|

accesses |

|||||||

|

LR/W0 |

|

|

|

LSTRB0 |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

LPAGE0 |

1 |

O/Z |

|

Page signal for |

LSTRB0 |

accesses |

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Ready signal for |

|

|

|

|

|

|

accesses |

||||||||

|

LRDY0 |

|

|

LSTRB0 |

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Control enable for the |

|

|

|

|

|

|

|

|

|

|

|

signals |

|||

|

LCE0 |

|

|

LSTRB0, |

LPAGE0, and LR/W0 |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

³ |

1 |

O/Z |

|

Access strobe 1 for the local bus external interface |

|||||||||||||||

|

LSTRB1 |

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

O/Z |

|

Read/write signal for |

|

|

|

|

|

|

|

accesses |

|||||||

|

LR/W1 |

|

|

LSTRB1 |

||||||||||||||||||||||||||||||

² I = input, O = output, Z = high impedance

³STRB0, STRB1 and associated signals (R/W1, R/W0, PAGE0, PAGE1, etc.) are effective over the address ranges defined by the STRB ACTIVE bits.

§ HFH package has additional power and ground pins to reduce noise problems.

10 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SMJ320C40 |

TMP320C40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIGITAL SIGNAL |

PROCESSORS |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

signal descriptions (continued) |

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

SMJ320C40 Signal Descriptions (Continued) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGNAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NAME |

NO. OF |

TYPE² |

|

|

|

|

|

|

|

DESCRIPTION |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

PINS |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOCAL BUS EXTERNAL INTERFACE (80 PINS) (CONTINUED) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LPAGE1 |

1 |

O/Z |

|

Page signal for |

LSTRB1 |

accesses |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

1 |

I |

|

Ready signal for |

|

|

|

accesses |

|

|

||||

|

LRDY1 |

|

|

|

|

|

|

LSTRB1 |

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

1 |

I |

|

Control enable for the |

|

|

|

|

|

signals |

|

|

||

|

LCE1 |

|

|

|

|

|

|

LSTRB1, |

LPAGE1, and LR/W1 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

COMMUNICATION PORT 0 INTERFACE (12 PINS) |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

C0D7±C0D0 |

8 |

I/O |

|

Communication port 0 data bus |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 0 token-request signal |

|

|

||||||||

|

CREQ0 |

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 0 token-request-acknowledge signal |

|

|

||||||||

|

CACK0 |

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 0 data-strobe signal |

|

|

||||||||

|

CSTRB0 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 0 data-ready signal |

|

|

||||||||

|

CRDY0 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

COMMUNICATION PORT 1 INTERFACE (12 PINS) |

|

|

|||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

C1D7±C1D0 |

8 |

I/O |

|

Communication port 1 data bus |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 1 token-request signal |

|

|

||||||||

|

CREQ1 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 1 token-request-acknowledge signal |

|

|

||||||||

|

CACK1 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 1 data-strobe signal |

|

|

||||||||

|

CSTRB1 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 1 data-ready signal |

|

|

||||||||

|

CRDY1 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

COMMUNICATION PORT 2 INTERFACE (12 PINS) |

|

|

|||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

C2D7±C2D0 |

8 |

I/O |

|

Communication port 2 data bus |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 2 token-request signal |

|

|

||||||||

|

CREQ2 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 2 token-request-acknowledge signal |

|

|

||||||||

|

CACK2 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 2 data-strobe signal |

|

|

||||||||

|

CSTRB2 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 2 data-ready signal |

|

|

||||||||

|

CRDY2 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

COMMUNICATION PORT 3 INTERFACE (12 PINS) |

|

|

|||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

C3D7±C3D0 |

8 |

I/O |

|

Communication port 3 data bus |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 3 token-request signal |

|

|

||||||||

|

CREQ3 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 3 token-request-acknowledge signal |

|

|

||||||||

|

CACK3 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 3 data-strobe signal |

|

|

||||||||

|

CSTRB3 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 3 data-ready signal |

|

|

||||||||

|

CRDY3 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

COMMUNICATION PORT 4 INTERFACE (12 PINS) |

|

|

|||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

C4D7±C4D0 |

8 |

I/O |

|

Communication port 4 data bus |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 4 token-request signal |

|

|

||||||||

|

CREQ4 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 4 token-request-acknowledge signal |

|

|

||||||||

|

CACK4 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 4 data-strobe signal |

|

|

||||||||

|

CSTRB4 |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 4 data-ready signal |

|

|

||||||||

|

CRDY4 |

|

|

|

|

||||||||||||||||

² I = input, O = output, Z = high impedance

³STRB0, STRB1 and associated signals (R/W1, R/W0, PAGE0, PAGE1, etc.) are effective over the address ranges defined by the STRB ACTIVE bits.

§ HFH package has additional power and ground pins to reduce noise problems.

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

11 |

SMJ320C40 TMP320C40

DIGITAL SIGNAL PROCESSORS

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000

signal descriptions (continued)

SMJ320C40 Signal Descriptions (Continued)

|

|

|

|

|

|

|

|

|

|

SIGNAL |

|

|

|

|

|

|

|

|

|

|

|

NAME |

NO. OF |

TYPE² |

|

|

|

DESCRIPTION |

|||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

PINS |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COMMUNICATION PORT 5 INTERFACE (12 PINS) |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C5D7±C5D0 |

8 |

I/O |

|

Communication port 5 data bus |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 5 token-request signal |

||

|

CREQ5 |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 5 token-request-acknowledge signal |

||

|

CACK5 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 5 data-strobe signal |

||

|

CSTRB5 |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I/O |

|

Communication port 5 data-ready signal |

||

|

CRDY5 |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

INTERRUPTS, I/O FLAGS, RESET, TIMER (12 PINS) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

IIOF3±IIOF0 |

4 |

I/O |

|

Interrupt and I/O flags |

||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Nonmaskable interrupt. |

|

is sensitive to a low-going edge. |

|

NMI |

|

|

|

|

NMI |

|||||||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

O |

|

Interrupt acknowledge |

||

|

IACK |

|

|

|

|||||||||||||

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

Reset signal |

||

|

RESET |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

||||||||||

|

RESETLOC1± |

2 |

I |

|

Reset-vector location pins |

||||||||||||

|

RESETLOC0 |

|

|||||||||||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

||||||||||||

|

ROMEN |

1 |

I |

|

On-chip ROM enable (0 = disable, 1 = enable) |

||||||||||||

|

|

|

|

|

|

||||||||||||

|

TCLK0 |

1 |

I/O |

|

Timer 0 pin |

||||||||||||

|

|

|

|

|

|

||||||||||||

|

TCLK1 |

1 |

I/O |

|

Timer 1 pin |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLOCK (4 PINS) |

||

|

|

|

|

|

|

||||||||||||

|

X1 |

1 |

O |

|

Crystal pin |

||||||||||||

|

|

|

|

|

|

||||||||||||

|

X2/CLKIN |

1 |

I |

|

Crystal/oscillator pin |

||||||||||||

|

|

|

|

|

|

||||||||||||

|

H1 |

1 |

O |

|

H1 clock |

||||||||||||

|

|

|

|

|

|

||||||||||||

|

H3 |

1 |

O |

|

H3 clock |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POWER AND GROUND (70 PINS)§ |

||

|

CVSS |

15§ |

I |

|

Ground pins |

||||||||||||

|

DVSS |

15§ |

I |

|

Ground pins |

||||||||||||

|

IVSS |

6§ |

I |

|

Ground pins |

||||||||||||

|

DVDD |

13 |

I |

|

5-VDC supply pins |

||||||||||||

|

GADVDD |

3§ |

I |

|

5-VDC supply pins |

||||||||||||

|

GDDVDD |

3§ |

I |

|

5-VDC supply pins |

||||||||||||

|

LADVDD |

3§ |

I |

|

5-VDC supply pins |

||||||||||||

|

LDDVDD |

3§ |

I |

|

5-VDC supply pins |

||||||||||||

|

SUBS |

1 |

I |

|

Substrate pin (tie to ground) |

||||||||||||

|

|

|

|

|

|

||||||||||||

|

VDDL |

4 |

I |

|

5-VDC supply pins |

||||||||||||

|

VSSL |

4 |

I |

|

Ground pins |

||||||||||||

² I = input, O = output, Z = high impedance

³STRB0, STRB1 and associated signals (R/W1, R/W0, PAGE0, PAGE1, etc.) are effective over the address ranges defined by the STRB ACTIVE bits.

§ HFH package has additional power and ground pins to reduce noise problems.

12 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

|

|

|

|

|

|

|

SMJ320C40 |

TMP320C40 |

|

|

|

|

|

|

|

|

DIGITAL SIGNAL |

PROCESSORS |

|

|

|

|

|

|

|

|

SGUS017F ± OCTOBER 1993 ± REVISED APRIL 2000 |

||

|

|

|

|

|

|

|

|

||

signal descriptions (continued) |

|

|

|

||||||

|

|

|

|

|

SMJ320C40 Signal Descriptions (Continued) |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGNAL |

|

|

|

|

|

|

|

|

|

NAME |

NO. OF |

TYPE² |

|

DESCRIPTION |

|

|

|

|

|

|

|

|

||||

|

|

|

PINS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EMULATION (7 PINS) |

|

|

|

|

|

|

|

|

|

|

|

|

|

TCK |

|

1 |

I |

|

IEEE 1149.1 test port clock |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TDO |

|

1 |

O/Z |

|

IEEE 1149.1 test port data out |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TDI |

|

1 |

I |

|

IEEE 1149.1 test port data in |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TMS |

|

1 |

I |

|

IEEE 1149.1 test port mode select |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I |

|

IEEE 1149.1 test port reset |

|

|

|

TRST |

|

|

|

|

|

|||

|

EMU0 |

|

1 |

I/O |

|

Emulation pin 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EMU1 |

|

1 |

I/O |

|

Emulation pin 1 |

|

|