ANALOG DEVICES AD5242 Service Manual

a 256-Position DigitalIPotentiometers2C® Compatible

|

|

|

AD5241/AD5242 |

|||

FEATURES |

|

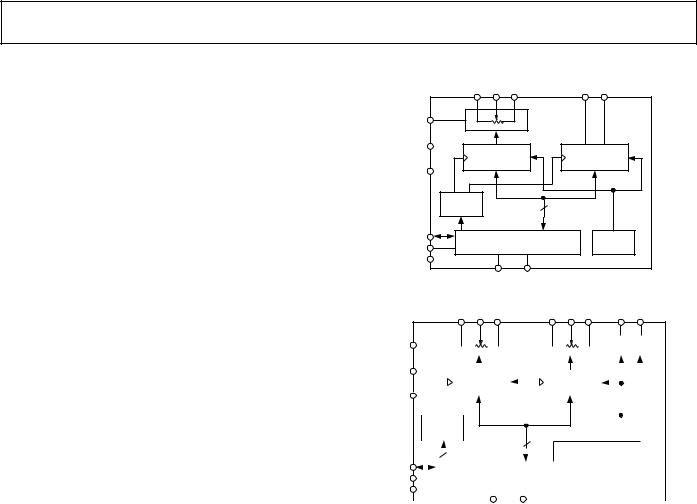

FUNCTIONAL BLOCK DIAGRAM |

|

|||

256 Positions |

|

A1 |

W1 B1 |

O1 |

O2 |

|

10 k , 100 k , 1 M |

|

|

||||

Low Tempco 30 ppm/ C |

|

|

|

|

|

|

Internal Power ON Midscale Preset |

SHDN |

|

|

AD5241 |

|

|

Single-Supply 2.7 V to 5.5 V or |

|

|

|

|

|

|

Dual-Supply 2.7 V for AC or Bipolar Operation |

VDD |

|

RDAC |

REGISTER 2 |

|

|

I2C Compatible Interface with Readback Capability |

|

REGISTER 1 |

|

|||

VSS |

|

|

|

|||

Extra Programmable Logic Outputs |

|

|

|

|

|

|

|

|

|

|

|

|

|

Self-Contained Shutdown Feature |

|

ADDR |

|

|

|

|

Extended Temperature Range –40 C to +105 C |

|

|

|

|

|

|

|

DECODE |

|

8 |

|

|

|

APPLICATIONS |

SDA |

|

|

|

PWR-ON |

|

Multimedia, Video, and Audio |

SERIAL INPUT REGISTER |

|

||||

SCL |

RESET |

|

||||

|

|

|

|

|||

Communications |

GND |

|

|

|

|

|

Mechanical Potentiometer Replacement |

|

|

AD0 |

AD1 |

|

|

Instrumentation: Gain, Offset Adjustment |

|

|

|

|

|

|

Programmable Voltage-to-Current Conversion |

|

A W1 B1 |

A2 W2 B2 |

O1 |

O2 |

|

Line Impedance Matching |

|

|||||

|

1 |

|

|

|

|

|

GENERAL DESCRIPTION |

SHDN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REGISTER |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

The AD5241/AD5242 provide a single-/dual-channel, 256- |

VDD |

|

|

|

|

|

|

|

|

|

|

|

|

RDAC |

|

|

|

|

|

|

|

|

|

|

|

RDAC |

|

|

|

|

|

|

|

|

|

||||||||

position, digitally controlled variable resistor (VR) device. These |

VSS |

|

|

|

|

|

|

|

|

|

|

REGISTER 1 |

|

|

|

|

|

|

|

|

|

|

REGISTER 2 |

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

devices perform the same electronic adjustment function as |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

potentiometer, trimmer, or variable resistor. Each VR offers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MacshbMADDR |

|

|

|

||||||||||||||||||||||||||||||||||||||||

completely programmable value of resistance between the A |

|

|

|

|

|

DECODE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

Terminal and the wiper, or the B Terminal and the wiper. |

|

|

|

|

|

|

|

|

|

|

1 |

|

AD5242 |

|

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

For AD5242, the fixed A-to-B terminal resistance of 10 kΩ, |

SDA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

100 kΩ, or 1 MΩ has a 1% channel-to-channel matching |

|

|

|

|

|

|

|

|

|

|

SERIAL INPUT REGISTER |

|

|

|

PWR-ON |

|

|

|

|||||||||||||||||||||||||

SCL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

tolerance. The nominal temperature coefficient of both parts is |

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 ppm/°C. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD0 |

|

AD1 |

|

|

|

|

|

|

|

|

|

|||||||||||||||

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 2002 |

AD5241/AD5242–SPECIFICATIONS

10 k , 100 k , 1 M VERSION |

(VDD = 3 V 10% or 5 V 10%, VA = +VDD, VB = 0 V, –40 C < TA < +105 C, unless |

||||||||

otherwise noted.) |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

Parameter |

|

Symbol |

|

Conditions |

Min |

Typ1 |

Max |

Unit |

|

DC CHARACTERISTICS, RHEOSTAT MODE (Specifications apply to all VRs.) |

|

± 0.4 |

|

|

|

||||

Resistor Differential Nonlinearity2 |

|

R-DNL |

|

RWB, VA = No Connect |

–1 |

+1 |

LSB |

||

|

|||||||||

Resistor Integral Nonlinearity2 |

|

R-INL |

|

RWB, VA = No Connect |

–2 |

± 0.5 |

+2 |

LSB |

|

Nominal Resistor Tolerance |

|

DR |

|

TA = 25°C, RAB = 10 kΩ |

–30 |

|

+30 |

% |

|

|

|

DR |

|

TA = 25°C, RAB = 100 kΩ/1 MΩ |

–30 |

|

+50 |

% |

|

Resistance Temperature Coefficient |

|

RAB/DT |

|

VAB = VDD, Wiper = No Connect |

|

30 |

|

ppm/°C |

|

Wiper Resistance |

|

RW |

|

IW = VDD /R, VDD = 3 V or 5 V |

|

60 |

120 |

Ω |

|

DC CHARACTERISTICS, POTENTIOMETER DIVIDER MODE (Specifications apply to all VRs.) |

|

|

|

|

|||||

Resolution |

|

N |

|

|

8 |

± 0.4 |

|

Bits |

|

|

|

|

|

||||||

Differential Nonlinearity3 |

|

DNL |

|

|

–1 |

+1 |

LSB |

||

Integral Nonlinearity3 |

|

INL |

|

|

–2 |

± 0.5 |

+2 |

LSB |

|

Voltage Divider Temperature |

|

|

|

|

|

|

|

ppm/°C |

|

Coefficient |

|

DVW/DT |

|

Code = 80H |

|

5 |

|

||

Full-Scale Error |

|

VWFSE |

|

Code = FFH |

–1 |

–0.5 |

0 |

LSB |

|

Zero-Scale Error |

|

VWZSE |

|

Code = 00H |

0 |

0.5 |

1 |

LSB |

|

RESISTOR TERMINALS |

|

|

|

|

|

|

|

|

|

Voltage Range4 |

|

VA, B, W |

|

|

VSS |

|

VDD |

V |

|

Capacitance5 A, B |

|

CA, B |

|

f = 1 MHz, Measured to GND, Code = 80H |

|

45 |

|

pF |

|

Capacitance5 W |

|

CW |

|

f = 1 MHz, Measured to GND, Code = 80H |

|

60 |

|

pF |

|

Common-Mode Leakage |

|

ICM |

|

VA = VB = VW |

|

1 |

|

nA |

|

DIGITAL INPUTS |

|

|

|

|

|

|

|

|

|

Input Logic High (SDA and SCL) |

|

VIH |

|

|

0.7 VDD |

VDD + 0.5 |

V |

||

Input Logic Low (SDA and SCL) |

|

VIL |

|

|

–0.5 |

|

+0.3 VDD |

V |

|

Input Logic High (AD0 and AD1) |

|

VIH |

|

VDD = 5 V |

2.4 |

|

VDD |

V |

|

Input Logic Low (AD0 and AD1) |

|

VIL |

|

VDD = 5 V |

0 |

|

0.8 |

V |

|

Input Logic High |

|

VIH |

|

VDD = 3 V |

2.1 |

|

VDD |

V |

|

|

|

|

MacshbM |

|

|||||

Input Logic Low |

|

VIL |

|

VDD = 3 V |

0 |

|

0.6 |

V |

|

Input Current |

|

IIL |

|

VIN = 0 V or 5 V |

|

|

1 |

µA |

|

Input Capacitance5 |

|

CIL |

|

|

|

3 |

|

pF |

|

DIGITAL OUTPUT |

|

VOL |

|

IOL = 3 mA |

|

|

0.4 |

V |

|

Output Logic Low (SDA) |

|

VOL |

|

IOL = 6 mA |

|

|

0.6 |

V |

|

Output Logic Low (O1 and O2) |

|

VOL |

|

ISINK = 1.6 mA |

|

|

0.4 |

V |

|

Output Logic High (O1 and O2) |

|

VOH |

|

ISOURCE = 40 µA |

4 |

|

|

V |

|

Three-State Leakage Current (SDA) |

|

IOZ |

|

VIN = 0 V or 5 V |

|

|

± 1 |

µA |

|

Output Capacitance5 |

|

COZ |

|

|

|

3 |

8 |

pF |

|

POWER SUPPLIES |

|

|

|

|

|

|

|

|

|

Power Single-Supply Range |

|

VDD RANGE |

|

VSS = 0 V |

2.7 |

|

5.5 |

V |

|

Power Dual-Supply Range |

|

VDD/SS RANGE |

± 2.3 |

|

|

± 2.7 |

V |

||

Positive Supply Current |

|

IDD |

|

VIH = 5 V or VIL = 0 V |

|

0.1 |

50 |

µA |

|

Negative Supply Current |

|

ISS |

|

VSS = –2.5 V, VDD = +2.5 V |

|

+0.1 |

–50 |

µA |

|

Power Dissipation6 |

|

PDISS |

|

VIH = 5 V or VIL = 0 V, VDD = 5 V |

|

0.5 |

250 |

µW |

|

Power Supply Sensitivity |

|

PSS |

|

|

–0.01 |

+0.002+0.01 |

%/% |

|

|

|

|

|

|

|

|

|

|

|

|

DYNAMIC CHARACTERISTICS5, 7, 8 |

|

BW_10 kΩ |

|

RAB = 10 kΩ, Code = 80H |

|

|

|

|

|

Bandwidth –3 dB |

|

|

|

650 |

|

kHz |

|||

|

|

BW_100 kΩ |

|

RAB = 100 kΩ, Code = 80H |

|

69 |

|

kHz |

|

|

|

BW_1 MΩ |

|

RAB = 1 MΩ, Code = 80H |

|

6 |

|

kHz |

|

Total Harmonic Distortion |

|

THDW |

|

VA = 1 V rms + 2 V dc, |

|

0.005 |

|

% |

|

|

|

|

|

VB = 2 V dc, f = 1 kHz |

|

|

|

|

|

VW Settling Time |

|

tS |

|

VA = VDD, VB = 0 V, ± 1 LSB Error Band, |

|

2 |

|

µs |

|

|

|

|

|

RAB = 10 kΩ |

|

|

|

|

|

Resistor Noise Voltage |

|

eN_WB |

|

RWB = 5 kΩ, f = 1 kHz |

|

14 |

|

nV√Hz |

|

–2– |

REV. B |

AD5241/AD5242

Parameter |

Symbol |

Conditions |

Min |

Typ1 Max |

Unit |

INTERFACE TIMING CHARACTERISTICS (Applies to all parts.5, 9) |

|

|

|

||

SCL Clock Frequency |

fSCL |

|

0 |

400 |

kHz |

tBUF Bus Free Time between |

t1 |

|

1.3 |

|

s |

STOP and START |

|

|

|

|

|

tHD; STA Hold Time (Repeated START) |

t2 |

After this period, the first clock |

600 |

|

ns |

|

|

pulse is generated. |

|

|

s |

tLOW Low Period of SCL Clock |

t3 |

|

1.3 |

|

|

tHIGH High Period of SCL Clock |

t4 |

|

0.6 |

50 |

s |

tSU; STA Setup Time for Repeated |

|

|

600 |

|

ns |

START Condition |

t5 |

|

|

||

tHD; DAT Data Hold Time |

t6 |

|

|

900 |

ns |

tSU; DAT Data Setup Time |

t7 |

|

100 |

|

ns |

tR Rise Time of Both |

t8 |

|

|

300 |

ns |

SDA and SCL Signals |

|

|

|

|

|

tF Fall Time of Both SDA and SCL Signals |

t9 |

|

|

300 |

ns |

tSU; STO Setup Time for STOP Condition |

t10 |

|

|

|

|

NOTES

1Typicals represent average readings at 25°C, VDD = 5 V.

2Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic. See Test Circuits.

3INL and DNL are measured at VW with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter. V A = VDD and VB = 0 V. DNL specification limits of ± 1 LSB maximum are guaranteed monotonic operating conditions. See Figure 10.

4Resistor terminals A, B, W have no limitations on polarity with respect to each other.

5Guaranteed by design and not subject to production test.

6PDISS is calculated from (IDD × VDD). CMOS logic level inputs result in minimum power dissipation.

7Bandwidth, noise, and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R value results in the minimum overall power consumption.

8All dynamic characteristics use V = 5 V.

See timing diagram for location of measured values.

Specifications subject to change without notice.

9 DD MacshbM

REV. B |

–3– |

AD5241/AD5242

ABSOLUTE MAXIMUM RATINGS*

(TA = 25°C, unless otherwise noted.)

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . |

. . |

. –0.3 V, +7 V |

VSS to GND . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . |

. . . 0 V , –7 V |

VDD to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . |

. . . . . . . . 7 V |

VA, VB, VW to GND . . . . . . . . . . . . . . . . . . . . |

. . |

. . . . VSS, VDD |

AX–BX, AX–WX, BX–WX at 10 kΩ in TSSOP-14 |

. . . ± 5.0 mA* |

|

AX–BX, AX–WX, BX–WX at 100 kΩ in TSSOP-14 |

. . ± 1.5 mA* |

|

AX–BX, AX–WX, BX–WX at 1 MΩ in TSSOP-14 |

. . . ± 0.5 mA* |

|

Digital Input Voltage to GND . . . . . . . . . . . . |

. . |

. . . . 0 V, 7 V |

Operating Temperature Range . . . . . . . . . . |

–40°C to +105°C |

|

Thermal Resistance θJA |

|

158°C/W |

SOIC (SOIC-14) . . . . . . . . . . . . . . . . . . . . |

. . . . . |

|

SOIC (SOIC-16) . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

73°C/W |

TSSOP-14 . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . |

206°C/W |

TSSOP-16 . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . |

180°C/W |

Maximum Junction Temperature (TJ max) . . |

. . . . . . |

. . 150°C |

Package Power Dissipation PD = (TJ max – TA)/θJA |

|

|

Storage Temperature . . . . . . . . . . . . . . . . . . |

–65°C to +150°C |

|

Lead Temperatures |

|

. 215°C |

R-14, R-16A, RU-14, RU-16 (Vapor Phase, 60 sec) |

||

R-14, R-16A, RU-14, RU-16 (Infrared, 15 sec) . . . . |

. 220°C |

|

*Max current increases at lower resistance and different packages.

ORDERING GUIDE

|

|

|

|

|

|

|

Number of |

|

|

|

Number of |

End to End |

Temperature |

Package |

Package |

Devices per |

|

Model |

|

Channels |

RAB ( ) |

Range ( C) |

Description |

Option |

Container |

|

AD5241BR10 |

|

1 |

10 k |

–40 to +105 |

SOIC-14 |

R-14 |

56 |

|

AD5241BR10-REEL7 |

1 |

10 k |

–40 to +105 |

SOIC-14 |

R-14 |

1000 |

|

|

AD5241BRU10-REEL7 |

1 |

10 k |

–40 to +105 |

TSSOP-14 |

RU-14 |

1000 |

|

|

AD5241BR100 |

1 |

100 k |

–40 to +105 |

SOIC-14 |

R-14 |

56 |

|

|

AD5241BR100-REEL7 |

1 |

100 k |

–40 to +105 |

SOIC-14 |

R-14 |

1000 |

|

|

AD5241BRU100-REEL7 |

1 |

100 k |

–40 to +105 |

TSSOP-14 |

RU-14 |

1000 |

|

|

AD5241BR1M |

1 |

1 M |

–40 to +105 |

SOIC-14 |

R-14 |

56 |

|

|

AD5241BRU1M-REEL7 |

1 |

1 M |

–40 to +105 |

TSSOP-14 |

RU-14 |

1000 |

|

|

AD5242BR10 |

|

MacshbM |

||||||

|

2 |

10 k |

–40 to +105 |

SOIC-16 |

R-16A |

48 |

|

|

AD5242BR10-REEL7 |

2 |

10 k |

–40 to +105 |

SOIC-16 |

R-16A |

1000 |

|

|

AD5242BRU10-REEL7 |

2 |

10 k |

–40 to +105 |

TSSOP-16 |

RU-16 |

1000 |

|

|

AD5242BR100 |

2 |

100 k |

–40 to +105 |

SOIC-16 |

R-16A |

48 |

|

|

AD5242BR100-REEL7 |

2 |

100 k |

–40 to +105 |

SOIC-16 |

R-16A |

1000 |

|

|

AD5242BRU100-REEL7 |

2 |

100 k |

–40 to +105 |

TSSOP-16 |

RU-16 |

1000 |

|

|

AD5242BR1M |

2 |

1 M |

–40 to +105 |

SOIC-16 |

R-16A |

48 |

|

|

AD5242BRU1M-REEL7 |

2 |

1 M |

–40 to +105 |

TSSOP-16 |

RU-16 |

1000 |

|

|

|

|

|

|

|

|

|

|

|

NOTES

1The AD5241/AD5242 die size is 69 mil × 78 mil, 5,382 sq. mil. Contains 386 transistors for each channel. Patent Number 5495245 applies. 2TSSOP packaged units are only available in 1,000-piece quantity Tape and Reel.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD5241/AD5242 feature proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING! |

ESD SENSITIVE DEVICE |

–4– |

REV. B |

AD5241/AD5242

|

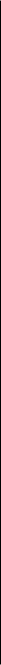

AD5241 PIN CONFIGURATION |

|

AD5242 PIN CONFIGURATION |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

O |

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

A |

|

1 |

|

14 |

|

O |

|

|

|

|

|

1 |

1 |

|

16 |

|||

|

|

|

1 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

W1 |

2 |

|

13 |

NC |

|

|

|

|

A1 |

2 |

|

15 |

W2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

B1 |

3 |

AD5241 |

12 |

O2 |

|

|

|

|

W1 |

3 |

AD5242 |

14 |

B2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

B1 |

|

|

O2 |

||||

|

|

V |

|

4 |

TOP VIEW |

11 |

|

V |

|

|

|

|

|

4 |

13 |

|||||

|

|

DD |

|

|

|

SS |

|

|

|

|

|

|

|

TOP VIEW |

|

|

|

|||

|

|

|

|

|

(Not to Scale) |

|

|

|

|

|

|

|

|

|

|

|

|

V |

||

|

|

SHDN |

5 |

10 |

|

DGND |

|

|

|

|

V |

|

5 |

(Not to Scale) |

12 |

|||||

|

|

|

|

|

|

|

|

|

|

DD |

|

|

|

SS |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DGND |

||||

|

|

SCL |

6 |

|

9 |

|

AD1 |

|

|

|

|

SHDN |

6 |

|

11 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

SCL |

|

|

|

AD1 |

||||

|

|

SDA |

7 |

|

8 |

|

AD0 |

|

|

|

|

7 |

|

10 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDA |

|

|

|

AD0 |

||

|

|

|

|

NC = NO CONNECT |

|

|

|

|

|

|

8 |

|

9 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||||||||||

|

AD5241 PIN FUNCTION DESCRIPTIONS |

|

AD5242 PIN FUNCTION DESCRIPTIONS |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Pin |

Mnemonic |

Description |

|

|

|

|

|

|

Pin |

Mnemonic |

Description |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

1 |

A1 |

Resistor Terminal A1 |

|

|

1 |

O1 |

Logic Output Terminal O1 |

|||||||||||||

2 |

W1 |

Wiper Terminal W1 |

|

|

|

2 |

A1 |

Resistor Terminal A1 |

||||||||||||

3 |

B1 |

Resistor Terminal B1 |

|

|

3 |

W1 |

Wiper Terminal W1 |

|||||||||||||

4 |

VDD |

Positive power supply, specified for opera- |

4 |

B1 |

Resistor Terminal B1 |

|||||||||||||||

|

|

tion from 2.2 V to 5.5 V. |

|

|

5 |

VDD |

Positive power supply, specified for opera- |

|||||||||||||

5 |

SHDN |

Active low, asynchronous connection of |

|

|

tion from 2.2 V to 5.5 V. |

|||||||||||||||

|

|

Wiper W to Terminal B, and open circuit |

6 |

SHDN |

Active low, asynchronous connection of |

|||||||||||||||

|

|

of Terminal A. RDAC register contents |

|

|

Wiper W to Terminal B, and open circuit |

|||||||||||||||

|

|

unchanged. SHDN should tie to VDD if |

|

|

of Terminal A. RDAC register contents |

|||||||||||||||

|

|

not used. |

|

|

|

|

|

|

|

|

unchanged. SHDN ould tie to VDD if |

|||||||||

6 |

SCL |

Serial Clock Input |

|

|

|

|

|

|

not u ed. |

|

|

|||||||||

7 |

SDA |

Serial Data Input/Output |

|

|

7 |

SCL |

Serial Clock Input |

|||||||||||||

|

AD0 |

|

|

|

|

|

|

|

|

MacshbM |

||||||||||

8 |

Programmable address bit for multiple |

8 |

SDA |

Serial Data Input/Output |

||||||||||||||||

|

|

|

|

|||||||||||||||||

|

|

package decoding. Bits AD0 and AD1 |

9 |

AD0 |

Programmable address bit for multiple |

|||||||||||||||

|

|

provide four possible addresses. |

|

|

package decoding. Bits AD0 and AD1 |

|||||||||||||||

9 |

AD1 |

Programmable address bit for multiple |

|

|

provide four possible addresses. |

|||||||||||||||

|

|

package decoding. Bits AD0 and AD1 |

10 |

AD1 |

Programmable address bit for multiple |

|||||||||||||||

|

|

provide four possible addresses. |

|

|

package decoding. Bits AD0 and AD1 |

|||||||||||||||

10 |

DGND |

Common Ground |

|

|

|

|

|

|

provide four possible addresses. |

|||||||||||

11 |

VSS |

Negative power supply, specified for |

11 |

DGND |

Common Ground |

|

|

|||||||||||||

12 |

O2 |

operation from 0 V to –2.7 V. |

12 |

VSS |

Negative power supply, specified for |

|||||||||||||||

Logic Output Terminal O2 |

|

|

|

|

operation from 0 V to –2.7 V. |

|||||||||||||||

13 |

NC |

No Connect |

|

|

|

|

|

|

13 |

O2 |

Logic Output Terminal O2 |

|||||||||

14 |

O1 |

Logic Output Terminal O1 |

|

|

14 |

B2 |

Resistor Terminal B2 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

15 |

W2 |

Wiper Terminal W2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

16 |

A2 |

Resistor Terminal A2 |

|

|||||

REV. B |

–5– |

Loading...

Loading...