Analog Devices AD2S80ATE-883B, AD2S80ATE, AD2S80ATD-883B, AD2S80ATD, AD2S80ASE-883B Datasheet

...

a |

Variable Resolution, Monolithic |

|

Resolver-to-Digital Converter |

||

|

|

|

|

|

AD2S80A |

|

|

|

FEATURES

Monolithic (BiMOS ll) Tracking R/D Converter 40-Pin DIP Package

44-Pin LCC Package

10-,12-,14- and 16-Bit Resolution Set by User Ratiometric Conversion

Low Power Consumption: 300 mW typ Dynamic Performance Set by User

High Max Tracking Rate 1040 RPS (10 Bits) Velocity Output

Industrial Temperature Range Versions Military Temperature Range Versions ESD Class 2 Protection (2,000 V min) /883 B Parts Available

APPLICATIONS

DC Brushless and AC Motor Control

Process Control

Numerical Control of Machine Tools

Robotics

Axis Control

Military Servo Control

GENERAL DESCRIPTION

The AD2S80A is a monolithic 10-, 12-, 14or 16-bit tracking resolver-to-digital converter contained in a 40-pin DIP or 44pin LCC ceramic package. It is manufactured on a BiMOS II process that combines the advantages of CMOS logic and bipolar high accuracy linear circuits on the same chip.

The converter allows users to select their own resolution and dynamic performance with external components. This allows the users great flexibility in defining the converter that best suits their system requirements. The converter allows users to select the resolution to he 10, 12, 14 or 16 bits and to track resolver signals rotating at up to 1040 revs per second (62,400 rpm) when set to 10-bit resolution.

The AD2S80A converts resolver format input signals into a parallel natural binary digital word using a ratiometric tracking conversion method. This ensures high-noise immunity and tolerance of lead length when the converter is remote from the resolver.

The 10-, 12-, 14or 16-bit output word is in a three-state digital logic available in 2 bytes on the 16 output data lines. BYTE SELECT, ENABLE and INHIBIT pins ensure easy data transfer to 8- and 16-bit data buses, and outputs are provided to allow for cycle or pitch counting in external counters.

An analog signal proportional to velocity is also available and can be used to replace a tachogenerator.

The AD2S80A operates over 50 Hz to 20,000 Hz reference frequency.

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

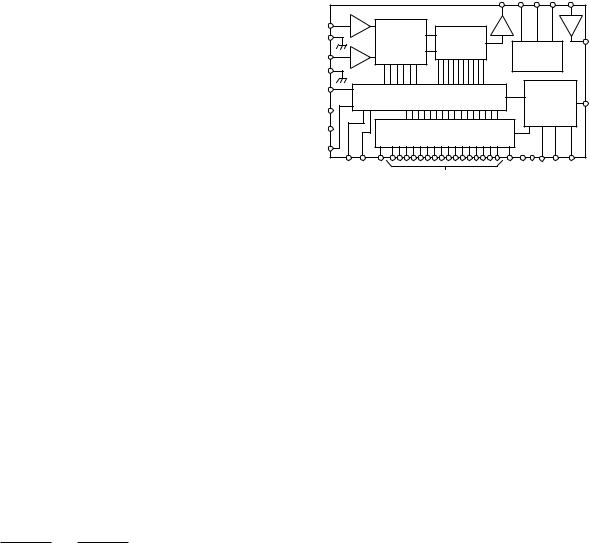

FUNCTIONAL BLOCK DIAGRAM

|

|

|

|

AC ERROR |

O/P |

DEMOD I/P |

DEMOD O/P |

INTEGRATOR |

I/P |

|

|

|

|

|

AD2S80A |

|

|

|

|

|

|

SIN I/P |

A1 |

|

|

A3 |

|

|

|

|

|

|

SIG GND |

|

|

|

|

|

|

|

INTEGRATOR |

||

|

SEGMENT |

R-2R |

|

|

|

|

|

|||

|

|

SWITCHING |

DAC |

|

|

PHASE |

|

O/P |

||

COS I/P |

A2 |

|

|

|

|

|

SENSITIVE |

|

|

|

ANALOG |

|

|

|

|

|

|

DETECTOR |

|

|

|

GND |

|

|

|

|

|

|

|

|

|

|

RIPPLE |

|

|

|

|

|

|

|

|

|

|

CLK |

|

16-BIT UP/DOWN COUNTER |

|

|

|

VCO DATA |

VCO I/P |

|||

|

|

|

|

|

TRANSFER |

|||||

+12V |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–12V |

|

|

OUTPUT DATA LATCH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

DATA |

|

|

|

|

|

|

|

|

|

|

LOAD |

|

|

|

|

|

|

|

|

|

|

SC1 |

SC2 |

ENABLE |

16 DATA BITS |

BYTE SELECT |

+5V |

DIG GND BUSY DIR |

INHIBIT |

|||

|

|

|||||||||

PRODUCT HIGHLIGHTS

Monolithic. A one chip solution reduces the package size required and increases the reliability.

Resolution Set by User. Two control pins are used to select the resolution of the AD2S80A to be 10, 12, 14 or 16 bits allowing the user to use the AD2S80A with the optimum resolution for each application.

Ratiometric Tracking Conversion. Conversion technique provides continuous output position data without conversion delay and is insensitive to absolute signal levels. It also provides good noise immunity and tolerance to harmonic distortion on the reference and input signals.

Dynamic Performance Set by the User. By selecting external resistor and capacitor values the user can determine bandwidth, maximum tracking rate and velocity scaling of the converter to match the system requirements. The external components required are all low cost preferred value resistors and capacitors, and the component values are easy to select using the simple instructions given.

Velocity Output. An analog signal proportional to velocity is available and is linear to typically one percent. This can be used in place of a velocity transducer in many applications to provide loop stabilization in servo controls and velocity feedback data.

Low Power Consumption. Typically only 300 mW.

Military Product. The AD2S80A is available processed in accordance with MIL-STD-883B, Class B.

MODELS AVAILABLE

Information on the models available is given in the section “Ordering Information.”

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD2S80A–SPECIFICATIONS (typical at +258C unless otherwise noted)

|

|

|

|

|

|

|

AD2S80A |

|

|

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

||||

|

|

|

|

|

|

|

|

|

|

SIGNAL INPUTS |

|

|

|

|

|

||||

|

Frequency |

|

50 |

|

20,000 |

Hz |

|||

|

Voltage Level |

|

1.8 |

2.0 |

2.2 |

V rms |

|||

|

Input Bias Current |

|

|

60 |

150 |

nA |

|||

|

Input Impedance |

|

1.0 |

|

|

MΩ |

|||

|

Maximum Voltage |

|

|

|

8 |

V pk |

|||

|

|

|

|

|

|

|

|

|

|

REFERENCE INPUT |

|

|

|

|

|

||||

|

Frequency |

|

50 |

|

20,000 |

Hz |

|||

|

Voltage Level |

|

1.0 |

|

8.0 |

V pk |

|||

|

Input Bias Current |

|

|

60 |

150 |

nA |

|||

|

Input Impedance |

|

1.0 |

|

|

MΩ |

|||

|

|

|

|

|

|

|

|

|

|

CONTROL DYNAMICS |

|

|

|

|

|

||||

|

Repeatability |

|

|

|

1 |

LSB |

|||

|

Allowable Phase Shift |

(Signals to Reference) |

–10 |

|

+10 |

Degrees |

|||

|

Tracking Rate |

10 Bits |

|

|

1040 |

rps |

|||

|

|

|

|

|

12 Bits |

|

|

260 |

rps |

|

|

|

|

|

14 Bits |

|

|

65 |

rps |

|

Bandwidth1 |

16 Bits |

|

|

16.25 |

rps |

|||

|

User Selectable |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

ACCURACY |

|

|

|

68 +1 LSB |

|

||||

|

Angular Accuracy |

A, J, S |

|

|

arc min |

||||

|

|

|

|

|

B, K, T |

|

|

64 +1 LSB |

arc min |

|

|

|

|

|

L, U |

|

|

62 +1 LSB |

arc min |

|

Monotonicity |

Guaranteed Monotonic |

|

|

4 |

|

|||

|

Missing Codes (16-Bit Resolution) |

A, B, J, K, S, T |

|

|

Codes |

||||

|

|

|

|

|

L, U |

|

|

1 |

Code |

|

|

|

|

|

|

|

|

|

|

VELOCITY SIGNAL |

|

|

± 1 |

63 |

|

||||

|

Linearity |

Over Full Range |

|

% FSD |

|||||

|

Reversion Error |

|

|

± 1 |

±2 |

% FSD |

|||

|

DC Zero Offset2 |

|

|

|

6 |

mV |

|||

|

DC Zero Offset Tempco |

|

|

–22 |

±10 |

μV/°C |

|||

|

Gain Scaling Accuracy |

|

±8 |

± 9 |

% FSD |

||||

|

Output Voltage |

1 mA Load |

±10.5 |

V |

|||||

|

Dynamic Ripple |

Mean Value |

|

|

1.5 |

% rms O/P |

|||

|

Output Load |

|

|

|

1.0 |

kΩ |

|||

|

|

|

|

|

|

|

|

|

|

INPUT/OUTPUT PROTECTION |

|

|

± 8 |

|

|

||||

|

Analog Inputs |

Overvoltage Protection |

±5.6 |

±10.4 |

V |

||||

|

Analog Outputs |

Short Circuit O/P Protection |

± 8 |

mA |

|||||

|

|

|

|

|

|

|

|

|

|

DIGITAL POSITION |

|

|

|

|

|

||||

|

Resolution |

10, 12, 14, and 16 |

|

|

|

|

|||

|

Output Format |

Bidirectional Natural Binary |

|

|

|

|

|||

|

Load |

|

|

|

|

|

|

3 |

LSTTL |

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

INHIBIT |

|

|

|

|

|

||||

|

Sense |

|

|

|

Logic LO to Inhibit |

|

|

|

|

|

Time to Stable Data |

|

|

|

600 |

ns |

|||

|

|

|

|

|

|

|

|

||

|

|

3 |

|

Logic LO Enables Position |

|

|

|

|

|

ENABLE |

|

|

|

|

|||||

|

|

|

|

|

Output. Logic HI Outputs in |

|

|

|

|

|

ENABLE |

Time |

High Impedance State |

35 |

|

110 |

ns |

||

|

|

|

|

|

|

|

|

||

BYTE SELECT3 |

|

|

|

|

|

||||

|

Sense |

|

|

|

MS Byte DB1–DB8, |

|

|

|

|

|

|

|

|

|

LS Byte DB9–DB16 |

|

|

|

|

|

LOGIC LO |

LS Byte DB1–DB8, |

|

|

|

|

|||

|

|

|

|

|

LS Byte DB9–DB16 |

|

|

|

|

|

Time to Data Available |

|

60 |

|

140 |

ns |

|||

|

|

|

|

|

|

||||

SHORT CYCLE INPUTS |

Internally Pulled High |

|

|

|

|

||||

|

SC1 |

SC2 |

(100 kΩ) to +VS |

|

|

|

|

||

|

|

|

|

|

|

||||

0 |

0 |

|

10 Bit |

|

|

|

|

||

0 |

1 |

|

12 Bit |

|

|

|

|

||

1 |

0 |

|

14 Bit |

|

|

|

|

||

1 |

1 |

|

16 Bit |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

–2– |

REV. A |

|

|

|

|

|

|

|

|

|

|

AD2S80A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD2S80A |

|

|

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|||||

|

|

|

|

|

|

|

|

|

|

|

DATA LOAD |

Internally Pulled High (100 kΩ) |

|

|

|

|

|||||

Sense |

|

150 |

300 |

ns |

||||||

|

to +VS. Logic LO Allows |

|

|

|

|

|||||

|

|

Data to be Loaded into the |

|

|

|

|

||||

|

|

Counters from the Data Lines |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

BUSY3 |

|

|

|

|

|

|

|

|

|

|

Sense |

Logic HI When Position O/P |

|

|

|

|

|||||

Width |

|

Changing |

200 |

|

600 |

ns |

||||

|

|

|

|

|

|

|

||||

Load |

Use Additional Pull-Up |

|

|

1 |

LSTTL |

|||||

|

|

|

|

|

|

|

|

|

|

|

DIRECTION3 |

|

|

|

|

|

|

|

|

|

|

Sense |

Logic HI Counting Up |

|

|

|

|

|||||

|

|

Logic LO Counting Down |

|

|

|

|

||||

Max Load |

|

|

|

|

|

|

|

|

3 |

LSTTL |

|

|

|

|

|

|

|

|

|

|

|

RIPPLE CLOCK3 |

|

|

|

|

|

|

|

|

|

|

Sense |

Logic HI |

|

|

|

|

|||||

|

|

All 1s to All 0s |

|

|

|

|

||||

|

|

All 0s to All 1s |

300 |

|

|

|

||||

Width |

Dependent on Input Velocity |

|

|

|

||||||

Reset |

Before Next Busy |

|

|

|

|

|||||

Load |

|

|

|

|

|

|

|

|

3 |

LSTTL |

|

|

|

|

|

|

|

|

|

|

|

DIGITAL INPUTS |

|

|

|

|

|

|

2.0 |

|

|

|

High Voltage, VIH |

|

INHIBIT |

, |

ENABLE |

|

|

|

|

V |

|

|

|

DB1–DB16, Byte Select |

|

|

|

|

||||

Low Voltage, VIL |

|

±VS = ±10.8 V, VL = 5.0 V |

|

|

0.8 |

|

||||

|

INHIBIT, |

ENABLE |

|

|

|

V |

||||

|

DB1–DB16, Byte Select |

|

|

|

|

|||||

|

|

±VS = ±13.2 V, VL = 5.0 V |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

DIGITAL INPUTS |

|

|

|

|

|

|

|

|

±100 |

μA |

High Current, IIH |

|

INHIBIT |

, |

ENABLE |

|

|

|

|||

|

DB1–DB16 |

|

|

|

|

|||||

Low Current, IIL |

±VS = ±13.2 V , VL = 5.5 V |

|

|

±100 |

μA |

|||||

|

INHIBIT, |

ENABLE |

|

|

|

|||||

|

DB1–DB16, Byte Select |

|

|

|

|

|||||

|

|

±VS = ±13.2 V, VL = 5.5 V |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

DIGITAL INPUTS |

|

|

|

|

|

|

|

|

1.0 |

|

Low Voltage, VIL |

|

ENABLE |

= HI |

|

|

V |

||||

|

|

SC1, SC2, Data Load |

|

|

|

|

||||

Low Current, IIL |

|

±VS = ±12.0 V, VL = 5.0 V |

|

|

–400 |

μA |

||||

|

ENABLE = HI |

|

|

|||||||

|

|

SC1, SC2, Data Load |

|

|

|

|

||||

|

|

±VS = ±12.0 V, VL = 5.0 V |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

DIGITAL OUTPUTS |

|

|

|

|

|

|

2.4 |

|

|

|

High Voltage, VOH |

|

DB1–DB16 |

|

|

V |

|||||

|

|

RIPPLE CLK, DIR |

|

|

|

|

||||

|

|

±VS = ±12.0 V, VL = 4.5 V |

|

|

|

|

||||

Low Voltage, VOL |

|

IOH = 100 μA |

|

|

0.4 |

|

||||

|

DB1–DB16 |

|

|

V |

||||||

|

|

RIPPLE CLK, DIR |

|

|

|

|

||||

|

|

±VS = ±12.0 V, VL = 5.5 V |

|

|

|

|

||||

|

|

IOL = 1.2 mA |

|

|

|

|

||||

THREE-STATE LEAKAGE |

|

DB1–DB16 Only |

|

|

|

|

||||

Current IL |

|

±VS = ±12.0 V, VL = 5.5 V |

|

|

±100 |

μA |

||||

|

VOL = 0 V |

|

|

±100 |

μA |

|||||

|

|

±VS = ±12.0 V, VL = 5.5 V |

|

|

||||||

|

|

VOH = 5.0 V |

|

|

|

|

||||

NOTES |

|

|

|

|

|

|

|

|

|

|

1Refer to small signal bandwidth. |

|

|

|

|

|

|

|

|

|

|

2Output offset dependent on value for R6. |

|

|

|

|

|

|

|

|

|

|

3Refer to timing diagram. |

|

|

|

|

|

|

|

|

|

|

Specifications subject to change without notice. |

|

|

|

|

|

|

|

|

|

|

All min and max specifications are guaranteed. Specifications in boldface are tested on all production units at final electrical test. |

|

|

||||||||

REV. A |

–3– |

AD2S80A–SPECIFICATIONS (typical at +258C unless otherwise noted)

|

|

|

AD2S80A |

|

|

Parameter |

Conditions |

Min |

Typ |

Max |

Units |

|

|

|

|

|

|

RATIO MULTIPLIER |

|

|

177.6 |

|

|

AC Error Output Scaling |

10 Bit |

|

|

mV/Bit |

|

|

12 Bit |

|

44.4 |

|

mV/Bit |

|

14 Bit |

|

11.1 |

|

mV/Bit |

|

16 Bit |

|

2.775 |

|

mV/Bit |

|

|

|

|

|

|

PHASE SENSITIVE DETECTOR |

|

|

|

12 |

|

Output Offset Voltage |

|

|

|

mV |

|

Gain |

|

|

|

|

|

In Phase |

w.r.t. REF |

–0.882 |

–0.9 |

–0.918 |

V rms/V dc |

In Quadrature |

w.r.t. REF |

|

|

±0.02 |

V rms/V dc |

Input Bias Current |

|

|

60 |

150 |

nA |

Input Impedance |

|

1 |

|

±8 |

MΩ |

Input Voltage |

|

|

|

V |

|

|

|

|

|

|

|

INTEGRATOR |

|

|

|

|

|

Open-Loop Gain |

At 10 kHz |

57 |

|

63 |

dB |

Dead Zone Current (Hysteresis) |

|

|

100 |

|

nA/LSB |

Input Offset Voltage |

|

|

1 |

5 |

mV |

Input Bias Current |

±VS = ±10.8 V dc |

±7 |

60 |

150 |

nA |

Output Voltage Range |

|

|

V |

||

|

|

|

|

|

|

VCO |

±VS = ±12 V dc |

|

|

1.1 |

MHz |

Maximum Rate |

|

|

|||

VCO Rate |

Positive Direction |

7.1 |

7.9 |

8.7 |

kHz/μA |

VCO Power Supply Sensitivity |

Negative Direction |

7.1 |

7.9 |

8.7 |

kHz/μA |

|

|

|

|

|

|

Increase |

+VS |

|

+0.5 |

|

%/V |

|

–VS |

|

–8.0 |

|

%/V |

Decrease |

+VS |

|

–8.0 |

|

%/V |

|

–VS |

|

+2.0 |

|

%/V |

Input Offset Voltage |

|

|

1 |

5 |

mV |

Input Bias Current |

|

|

70 |

380 |

nA |

Input Bias Current Tempco |

|

|

–1.22 |

±8 |

nA/°C |

Input Voltage Range |

|

|

|

V |

|

Linearity of Absolute Rate |

|

|

|

<2 |

|

Full Range |

|

|

|

% FSD |

|

Over 0% to 50% of Full Range |

|

|

|

<1 |

% FSD |

Reversion Error |

|

|

± 8 |

1.5 |

% FSD |

Sensitivity of Reversion Error |

|

|

|

%/V of |

|

to Symmetry of Power Supplies |

|

|

|

|

Asymmetry |

|

|

|

|

|

|

POWER SUPPLIES |

|

|

|

|

|

Voltage Levels |

|

+10.8 |

|

+13.2 |

|

+VS |

|

|

V |

||

–VS |

|

–10.8 |

|

–13.2 |

V |

+VL |

|

+5 |

|

+13.2 |

V |

Current |

|

|

|

|

|

±IS |

±VS @ ±12 V |

|

612 |

623 |

mA |

±IS |

±VS @ 13.2 V |

|

619 |

630 |

mA |

±IL |

+VL @ ±5.0 V |

|

60.5 |

61.5 |

mA |

|

|

|

|

|

|

Specification subject to change without notice.

All min and max specifications are guaranteed. Specifications in boldface are tested on all production units at final electrical test.

ESD SENSITIVITY

The AD2S80A features an input protection circuit consisting of large “distributed” diodes and polysilicon series resistors to dissipate both high energy discharges (Human Body Model) and fast, low energy pulses (Charges Device Model).

The AD2S80A is ESD protection Class II (2000 V min). Proper ESD precautions are strongly recommended to avoid functional damage or performance degradation. For further information on ESD precautions, refer to Analog Devices ESD Prevention Manual.

WARNING!

ESD SENSITIVE DEVICE

–4– |

REV. A |

RECOMMENDED OPERATING CONDITIONS

Power Supply Voltage (+VS, –VS) . . . . . . . . . |

±12 V dc ± 10% |

Power Supply Voltage VL . . . . . . . . . . . . . . . . |

. +5 V dc ± 10% |

Analog Input Voltage (SIN and COS) . . . . . . |

. 2 V rms ± 10% |

Analog Input Voltage (REF) . . . . . . . . . . . . . |

. 1 V to 8 V peak |

Signal and Reference Harmonic Distortion . . |

. . . . . 10% (max) |

Phase Shift Between Signal and Reference . . . ±10 Degrees (max) |

|

Ambient Operating Temperature Range |

0°C to +70°C |

Commercial (JD, KD, LD) . . . . . . . . . . . . |

|

Industrial (AD, BD) . . . . . . . . . . . . . . . . . . |

. –40°C to +85°C |

Extended (SD, SE, TD, TE, UD, UE) . . . |

–55°C to +125°C |

ABSOLUTE MAXIMUM RATINGSl (with respect to GND)

+VS2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . +14 V dc |

–VS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . –14 V dc |

+VL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . +VS |

Reference . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . +14 V to –VS |

SIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . +14 V to –VS |

COS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . +14 V to –VS |

Any Logical Input .. . . . . . . . . . . . . . . . . . . |

–0.4 V dc to +VL dc |

Demodulator Input . . . . . . . . . . . . . . . . . . |

. . . . . +14 V to –VS |

Integrator Input . . . . . . . . . . . . . . . . . . . . . |

. . . . . +14 V to –VS |

VCO Input . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . +14 V to –VS |

Power Dissipation . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . 860 mW |

Operating Temperature |

0°C to +70°C |

Commercial (JD, KD, LD) . . . . . . . . . . |

|

Industrial (AD, BD) . . . . . . . . . . . . . . . . |

. . . –40°C to +85°C |

Extended (SD, SE, TD, TE, UD, UE) . |

. . –55°C to +125°C |

θJC3 (40-Pin DIP 883 Parts Only) . . . . . . . |

. . . . . . . . . 11°C/W |

θJC3 (44-Pin LCC 883 Parts Only) . . . . . . . . |

. . . . . . . . 10°C/W |

Storage Temperature (All Grades) . . . . . . . . |

. –65°C to +150°C |

Lead Temperature (Soldering, 10 sec) . . . . . |

. . . . . . . . +300°C |

CAUTION:

1.Absolute Maximum Ratings are those values beyond which damage to the device may occur.

2.Correct polarity voltages must be maintained on the +VS and –VS pins.

3.With reference to Appendix C of MIL-M-38510.

Bit Weight Table

Binary |

Resolution |

Degrees |

Minutes |

Seconds |

Bits (N) |

(2N) |

/Bit |

/Bit |

/Bit |

|

|

|

|

|

0 |

1 |

360.0 |

21600.0 |

1296000.0 |

1 |

2 |

180.0 |

10800.0 |

648000.0 |

2 |

4 |

90.0 |

5400.0 |

324000.0 |

3 |

8 |

45.0 |

2700.0 |

162000.0 |

4 |

16 |

22.5 |

1350.0 |

81000.0 |

|

|

|

|

|

5 |

32 |

11.25 |

675.0 |

40500.0 |

6 |

64 |

5.625 |

337.5 |

20250.0 |

7 |

128 |

2.8125 |

168.75 |

10125.0 |

8 |

256 |

1.40625 |

84.375 |

5062.5 |

9 |

512 |

0.703125 |

42.1875 |

2531.25 |

|

|

|

|

|

10 |

1024 |

0.3515625 |

21.09375 |

1265.625 |

11 |

2048 |

0.1757813 |

10.546875 |

632.8125 |

12 |

4096 |

0.0878906 |

5.273438 |

316.40625 |

13 |

8192 |

0.0439453 |

2.636719 |

158.20313 |

14 |

16384 |

0.0219727 |

1.318359 |

79.10156 |

|

|

|

|

|

15 |

32768 |

0.0109836 |

0.659180 |

39.55078 |

16 |

65536 |

0.0054932 |

0.329590 |

19.77539 |

17 |

131072 |

0.0027466 |

0.164795 |

9.88770 |

18 |

262144 |

0.0013733 |

0.082397 |

4.94385 |

|

|

|

|

|

AD2S80A

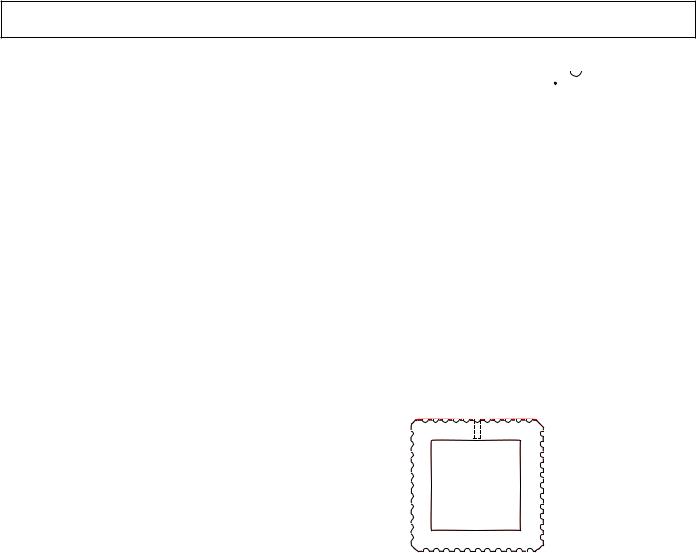

PIN CONFIGURATIONS

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REFERENCE I/P |

1 |

|

|

40 |

DEMOD O/P |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DEMOD I/P |

2 |

|

|

39 |

INTEGRATOR O/P |

||||

DIP (D) Package |

|

|

|

AC ERROR O/P |

|

|

|

|

INTEGRATOR I/P |

||||||||||||||

|

|

|

3 |

|

|

38 |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COS |

4 |

|

|

37 |

VCO I/P |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

–VS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ANALOG GND |

5 |

|

|

36 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGNAL GND |

6 |

|

|

35 |

RIPPLE CLK |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIN |

7 |

|

|

34 |

DIRECTION |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+VS |

|

|

|

|

BUSY |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

8 |

|

|

33 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MSB DB1 |

|

|

|

|

DATA LOAD |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

AD2S80A |

32 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SC2 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB2 |

10 |

|

TOP VIEW |

31 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB3 |

11 |

|

(Not to Scale) |

30 |

SC1 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB4 |

12 |

|

|

29 |

DIGITAL GND |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB5 |

13 |

|

|

28 |

INHIBIT |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB6 |

14 |

|

|

27 |

BYTE SELECT |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB7 |

15 |

|

|

26 |

ENABLE |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB8 |

16 |

|

|

25 |

VL |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB9 |

17 |

|

|

24 |

DB16 LSB |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB10 |

|

|

|

|

DB15 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

|

23 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB11 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

22 |

DB14 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB12 |

20 |

|

|

21 |

DB13 |

|||

|

|

|

SIGNAL GND |

ANALOG GND |

|

AC ERROR O/P |

DEMOD I/P |

REFERENCE I/P |

|

DEMOD O/P |

INTEGRATOR O/P |

INTEGRATOR I/P |

|

VCO I/P |

|

|

|

|

|||||

|

|

|

COS |

|

NC |

|

|

LCC (E) Package |

|||||||||||||||

|

|

6 |

5 |

|

4 |

3 |

2 |

1 |

44 |

43 |

42 |

41 |

40 |

|

|

|

|

|

|

||||

SIN |

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

–VS |

|

|

|

||

+VS |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

RIPPLE CLOCK |

|

|

|

||

|

NC |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

DIRECTION |

|

|

|

|

MSB DB1 10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

BUSY |

|

|

|

|||||

DB2 11 |

|

|

|

AD2S80A |

|

|

|

|

35 |

DATA LOAD |

|

|

|

||||||||||

DB3 12 |

|

|

|

|

|

|

|

34 |

NC |

|

|

|

|||||||||||

|

|

|

|

TOP VIEW |

|

|

|

|

|

|

|

|

|||||||||||

DB4 |

13 |

|

|

|

|

|

(Not to Scale) |

|

|

|

|

33 |

SC2 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

DB5 14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

SC1 |

|

|

|

|||||

DB6 15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

31 |

DIGITAL GND |

|

|

|

|||||

DB7 16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

INHIBIT |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

DB8 17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

29 |

NC |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

18 |

19 |

20 |

21 |

22 |

23 |

24 |

25 |

26 |

27 |

28 |

|

|

|

|

|

|

|||||

|

|

|

DB9 |

DB10 |

DB11 |

DB12 |

DB13 |

DB14 |

|

DB15 |

LSB DB16 |

L |

ENABLE |

|

BYTESELECT |

|

|

|

|

|

|

||

|

NC = NO CONNECT |

|

+V |

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

PIN DESIGNATIONS |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

MNEMONIC |

|

|

|

|

|

DESCRIPTION |

|

|

|

|

|

|

|||||||||

|

|

REFERENCE I/P |

|

|

|

|

REFERENCE SIGNAL INPUT |

|

|

|

|||||||||||||

|

|

DEMOD I/P |

|

|

|

|

|

DEMODULATOR INPUT |

|

|

|

||||||||||||

|

|

AC ERROR O/P |

|

|

|

|

RATIO MULTIPLIER OUTPUT |

|

|

|

|||||||||||||

|

|

COS |

|

|

|

|

|

|

|

COSINE INPUT |

|

|

|

|

|

|

|||||||

|

|

ANALOG GROUND |

|

|

|

POWER GROUND |

|

|

|

|

|||||||||||||

|

|

SIGNAL GROUND |

|

|

|

RESOLVER SIGNAL GROUND |

|

|

|

||||||||||||||

|

|

SIN |

|

|

|

|

|

|

|

SINE INPUT |

|

|

|

|

|

|

|||||||

|

|

+VS |

|

|

|

|

|

|

|

POSITIVE POWER SUPPLY |

|

|

|

||||||||||

|

|

DB1–DB16 |

|

|

|

|

|

|

|

PARALLEL OUTPUT DATA |

|

|

|

||||||||||

|

|

VL |

|

|

|

|

|

|

|

LOGIC POWER SUPPLY |

|

|

|

||||||||||

|

|

ENABLE |

|

|

|

|

|

|

|

|

LOGIC Hl-OUTPUT DATA IN HIGH IMPEDANCE |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

STATE, LOGIC LO PRESENTS DATA TO THE |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUT LATCHES |

|

|

|

|

|||||||

|

|

BYTE SELECT |

|

|

|

|

|

LOGIC Hl-MOST SIGNIFICANT BYTE TO DB1–DB8 |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC LO-LEAST SlGNlFlCANT BYTE TO DB1–DB8 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

LOGIC LO INHIBITS DATA TRANSFER TO |

|

|||||||||||

|

|

INHIBIT |

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUT LATCHES |

|

|

|

|

|||||||

|

|

DIGITAL GROUND |

|

|

|

DlGITAL GROUND |

|

|

|

|

|||||||||||||

|

|

SC1–SC2 |

|

|

|

|

|

|

|

SELECT CONVERTER RESOLUTION |

|

|

|

||||||||||

|

|

DATA LOAD |

|

|

|

|

|

LOGIC LO DB1–DB16 INPUTS LOGIC Hl DB1–D16 |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

OUTPUTS |

|

|

|

|

|

|

|

|

|||

|

|

BUSY |

|

|

|

|

|

|

|

CONVERTER BUSY, DATA NOT VALID WHILE |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

BUSY Hl |

|

|

|

|

|

|

|

|

|||

|

|

DIRECTION |

|

|

|

|

|

LOGIC STATE DEFINES DIRECTION |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

OF INPUT SIGNAL ROTATION |

|

|

|

||||||||

|

|

RIPPLE CLOCK |

|

|

|

|

POSITIVE PULSE WHEN CONVERTER OUTPUT |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

CHANGES FROM 1S TO ALL 0S OR VICE VERSA |

|

||||||||||

|

|

–VS |

|

|

|

|

|

|

|

NEGATIVE POWER SUPPLY |

|

|

|

||||||||||

|

|

VCO I/P |

|

|

|

|

|

|

|

VCO INPUT |

|

|

|

|

|

|

|||||||

|

|

INTEGRATOR I/P |

|

|

|

|

INTEGRATOR INPUT |

|

|

|

|

||||||||||||

|

|

INTEGRATOR O/P |

|

|

|

INTEGRATOR OUTPUT |

|

|

|

||||||||||||||

|

|

DEMOD O/P |

|

|

|

|

|

DEMODULATOR OUTPUT |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REV. A |

–5– |

Loading...

Loading...