Texas Instruments UC3854DW, UC3854QTR, UC3854Q, UC3854N, UC3854DWTR Datasheet

...

UC1854

UC2854

UC3854

High Power Factor Preregulator

FEATURES

∙Control Boost PWM to 0.99 Power Factor

∙Limit Line Current Distortion To <5%

∙World-Wide Operation Without Switches

∙Feed-Forward Line Regulation

∙Average Current-Mode Control

∙Low Noise Sensitivity

∙Low Start-Up Supply Current

∙Fixed-Frequency PWM Drive

∙Low-Offset Analog Multiplier/Divider

∙1A Totem-Pole Gate Driver

∙Precision Voltage Reference

BLOCK DIAGRAM

DESCRIPTION

The UC1854 provides active power factor correction for power systems that otherwise would draw non-sinusoidal current from sinusoidal power lines. This device implements all the control functions necessary to build a power supply capable of optimally using available power-line current while minimizing line-current distortion. To do this, the UC1854 contains a voltage amplifier, an analog multiplier/divider, a current amplifier, and a fixed-frequency PWM. In addition, the UC1854 contains a power MOSFET compatible gate driver, 7.5V reference, line anticipator, load-enable comparator, low-supply detector, and over-current comparator.

The UC1854 uses average current-mode control to accomplish fixedfrequency current control with stability and low distortion. Unlike peak current-mode, average current control accurately maintains sinusoidal line current without slope compensation and with minimal response to noise transients.

The UC1854’s high reference voltage and high oscillator amplitude minimize noise sensitivity while fast PWM elements permit chopping frequencies above 200kHz. The UC1854 can be used in single and three phase systems with line voltages that vary from 75 to 275 volts and line frequencies across the 50Hz to 400Hz range. To reduce the burden on the circuitry that supplies power to this device, the UC1854 features low starting supply current.

These devices are available packaged in 16-pin plastic and ceramic dual in-line packages, and a variety of surface-mount packages.

UDG-92055 |

6/98 |

ABSOLUTE MAXIMUM RATINGS

Supply Voltage VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35V

GT Drv Current, Continuous . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.5A

GT Drv Current, 50% Duty Cycle. . . . . . . . . . . . . . . . . . . . . . . . . 1.5A

Input Voltage, VSENSE, VRMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11V

Input Voltage, ISENSE, Mult Out . . . . . . . . . . . . . . . . . . . . . . . . . . . 11V

Input Voltage, PKLMT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5V

Input Current, RSET, IAC, PKLMT, ENA . . . . . . . . . . . . . . . . . . . 10mA

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1W

Storage Temperature . . . . . . . . . . . . . . . . . . . . –65oC to +150oC

Lead Temperature (Soldering, 10 Seconds) . . . . . . . . . . . . . . +300oC

UC1854

UC2854

UC3854

Note 1: All voltages with respect to Gnd (Pin 1).

Note 2: All currents are positive into the specified terminal.

Note 3: ENA input is internally clamped to approximately 14V.

Note 4: Consult Unitrode Integrated Circuits databook for information regarding thermal specifications and limita-

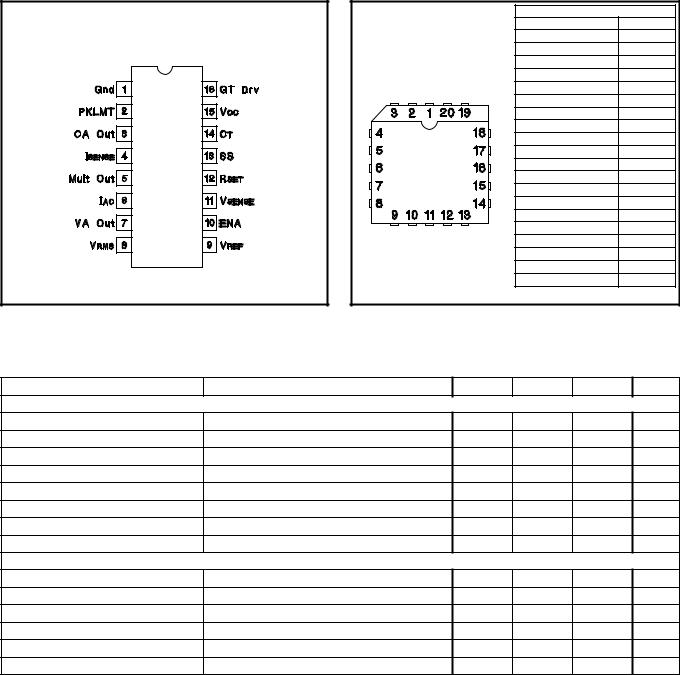

CONNECTION DIAGRAMS

DIL–16 & SOIC-16 |

|

|

PLCC-20 & LCC-20 |

PACKAGE PIN FUNCTION |

|||

(Top View) |

|

|

(Top View) |

|

FUNCTION |

PIN |

|

J, N & DW Packages |

|

|

Q & L Packages |

|

N/C |

|

1 |

|

|

|

Gnd |

|

2 |

||

|

|

|

|

|

|

||

|

|

|

|

|

PKLMT |

|

3 |

|

|

|

|

|

CA Out |

|

4 |

|

|

|

|

|

ISENSE |

|

5 |

|

|

|

|

|

N/C |

|

6 |

|

|

|

|

|

Mult Out |

|

7 |

|

|

|

|

|

IAC |

|

8 |

|

|

|

|

|

VA Out |

|

9 |

|

|

|

|

|

VRMS |

|

10 |

|

|

|

|

|

N/C |

|

11 |

|

|

|

|

|

VREF |

|

12 |

|

|

|

|

|

ENA |

|

13 |

|

|

|

|

|

VSENSE |

|

14 |

|

|

|

|

|

RSET |

|

15 |

|

|

|

|

|

N/C |

|

16 |

|

|

|

|

|

SS |

|

17 |

|

|

|

|

|

CT |

|

18 |

|

|

|

|

|

VCC |

|

19 |

|

|

|

|

|

GT Drv |

|

20 |

ELECTRICAL |

Unless otherwise stated, VCC=18V, RSET=15k to ground, CT=1.5nF to ground, PKLMT=1V, ENA=7.5V, |

||||||

CHARACTERISTICS VRMS=1.5V, IAC=100μA, ISENSE=0V, CA Out=3.5V, VA Out=5V, VSENSE=7.5V, no load on SS, CA Out, |

|||||||

|

VA Out, REF, GT Drv, –55oC<TA<125oC for the UC1854, –40oC<TA<85oC for the UC2854, and |

|

|||||

|

0oC<TA<70oC for the UC3854, and TA=TJ. |

|

|

|

|

||

PARAMETER |

|

|

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

OVERALL |

|

|

|

|

|

|

|

Supply Current, Off |

|

ENA=0V |

|

|

1.5 |

2.0 |

mA |

Supply Current, On |

|

|

|

|

10 |

16 |

mA |

VCC Turn-On Threshold |

|

|

|

14.5 |

16 |

17.5 |

V |

VCC Turn-Off Threshold |

|

|

|

9 |

10 |

11 |

V |

ENA Threshold, Rising |

|

|

|

2.4 |

2.55 |

2.7 |

V |

ENA Threshold Hysteresis |

|

|

0.2 |

0.25 |

0.3 |

V |

|

ENA Input Current |

|

ENA=0V |

|

–5.0 |

–0.2 |

5.0 |

μA |

VRMS Input Current |

|

VRMS=5V |

|

–1.0 |

–.01 |

1.0 |

μA |

VOLTAGE AMPLIFIER |

|

|

|

|

|

|

|

Voltage Amp Offset Voltage |

VA Out=5V |

|

–8 |

|

8 |

mV |

|

VSENSE Bias Current |

|

|

|

–500 |

–25 |

500 |

nA |

Voltage Amp Gain |

|

|

|

70 |

100 |

|

dB |

Voltage Amp Output Swing |

|

|

|

0.5 to 5.8 |

|

V |

|

Voltage Amp Short Circuit Current |

VA Out=0V |

|

–36 |

–20 |

–5 |

mA |

|

SS Current |

|

SS=2.5V |

|

–20 |

–14 |

–6 |

μA |

2

ELECTRICAL CHARACTERISTICS

UC1854

UC2854

UC3854

Unless otherwise stated, VCC=18V, RSET=15k to ground, CT=1.5nF to ground, PKLMT=1V, ENA=7.5V, VRMS=1.5V, IAC=100μA, ISENSE=0V, CA Out=3.5V, VA Out=5V, VSENSE=7.5V, no load on SS, CA Out, VA Out, REF, GT Drv, –55oC<TA<125oC for the UC1854, –40oC<TA<85oC for the UC2854, and 0oC<TA<70oC for the UC3854, and TA=TJ.

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

CURRENT AMPLIFIER |

|

|

|

|

|

Current Amp Offset Voltage |

|

–4 |

|

4 |

mV |

ISENSE Bias Current |

|

–500 |

–120 |

500 |

nA |

Input Range, ISENSE, Mult Out |

|

–0.3 to 2.5 |

|

|

V |

Current Amp Gain |

|

80 |

110 |

|

dB |

Current Amp Output Swing |

|

|

0.5 to 16 |

|

V |

|

|

|

|

|

|

Current Amp Short Circuit Current |

CA Out=0V |

–36 |

–20 |

–5 |

mA |

Current Amp Gain-BW Product |

TA=25oC (Note 6) |

400 |

800 |

|

kHz |

REFERENCE |

|

|

|

|

|

Reference Output Voltage |

IREF=0mA, TA=25oC |

7.4 |

7.5 |

7.6 |

V |

|

IREF=0mA, Over Temp. |

7.35 |

7.5 |

7.65 |

V |

|

|

|

|

|

|

VREF Load Regulation |

–10mA<IREF<0mA |

–15 |

5 |

15 |

mV |

VREF Line Regulation |

15V<VCC<35V |

–10 |

2 |

10 |

mV |

VREF Short Circuit Current |

REF=0V |

–50 |

–28 |

–12 |

mA |

MULTIPLIER |

|

|

|

|

|

Mult Out Current IAC Limited |

IAC=100μA, RSET=10k, VRMS=1.25V |

–220 |

–200 |

–180 |

μA |

Mult Out Current Zero |

IAC=0μA, RSET=15k |

–2.0 |

–0.2 |

2.0 |

μA |

Mult Out Current RSET Limited |

IAC=450μA, RSET=15k, VRMS=1V, VA Out = 6V |

–280 |

–255 |

–220 |

μA |

Mult Out Current |

IAC=50μA, VRMS=2V, VA=4V |

–50 |

–42 |

–33 |

μA |

|

IAC=100μA, VRMS=2V, VA=2V |

–38 |

–27 |

–12 |

μA |

|

IAC=200μA, VRMS=2V, VA=4V |

–165 |

–150 |

–105 |

μA |

|

IAC=300μA, VRMS=1V, VA=2V |

–250 |

–225 |

–150 |

μA |

|

IAC=100μA, VRMS=1V, VA=2V |

–95 |

–80 |

–60 |

μA |

Multiplier Gain Constant |

(Note 5) |

|

–1.0 |

|

V |

OSCILLATOR |

|

|

|

|

|

Oscillator Frequency |

RSET=15k |

46 |

55 |

62 |

kHz |

|

RSET=8.2k |

86 |

102 |

118 |

kHz |

CT Ramp Peak-to-Valley Amplitude |

|

4.9 |

5.4 |

5.9 |

V |

CT Ramp Valley Voltage |

|

0.8 |

1.1 |

1.3 |

V |

GATE DRIVER |

|

|

|

|

|

Maximum GT Drv Output Voltage |

0mA load on GT Drv, 18V<VCC<35V |

13 |

14.5 |

18 |

V |

GT Drv Output Voltage High |

–200mA load on GT Drv, VCC=15V |

12 |

12.8 |

|

V |

GT Drv Output Voltage Low, Off |

VCC=0V, 50mA load on GT Drv |

|

0.9 |

1.5 |

V |

GT Drv Output Voltage Low |

200mA load on GT Drv |

|

1.0 |

2.2 |

V |

|

10mA load on GT Drv |

|

0.1 |

0.4 |

V |

|

|

|

|

|

|

Peak GT Drv Current |

10nF from GT Drv to Gnd |

|

1.0 |

|

A |

GT Drv Rise/Fall Time |

1nF from GT Drv to Gnd |

|

35 |

|

ns |

GT Drv Maximum Duty Cycle |

VCA Out=7V |

|

95 |

|

% |

CURRENT LIMIT |

|

|

|

|

|

PKLMT Offset Voltage |

|

–10 |

|

10 |

mV |

|

|

|

|

|

|

PKLMT Input Current |

PKLMT=–0.1V |

–200 |

–100 |

|

μA |

PKLMT to GT Drv Delay |

PKLMT falling from 50mV to –50mV |

|

175 |

|

ns |

|

|

|

|

|

|

Note 5: Multiplier Gain Constant (k) is defined by: IMult Out

= k × IAC × (VA Out−1)

VRMS2

Note 6: Guaranteed by design. Not 100% tested in production.

3

Loading...

Loading...