Texas Instruments UC3823BN, UC3823BDWTR, UC3823BDW, UC3825BQTR, UC3825BQ Datasheet

...

UC1823A,B/1825A,B

UC2823A,B/2825A,B

UC3823A,B/3825A,B

High Speed PWM Controller

FEATURES

•Improved versions of the UC3823/UC3825 PWMs

•Compatible with Voltage or Current-Mode Topologies

•Practical Operation at Switching Frequencies to 1MHz

•50ns Propagation Delay to Output

•High Current Dual Totem Pole Outputs (2A Peak)

•Trimmed Oscillator Discharge Current

•Low 100μA Startup Current

•Pulse-by-Pulse Current Limiting Comparator

•Latched Overcurrent Comparator With Full Cycle Restart

DESCRIPTION

The UC3823A & B and the UC3825A & B family of PWM control ICs are improved versions of the standard UC3823 & UC3825 family. Performance enhancements have been made to several of the circuit blocks. Error amplifier gain bandwidth product is 12MHz while input offset voltage is 2mV. Current limit threshold is guaranteed to a tolerance of 5%. Oscillator discharge current is specified at 10mA for accurate dead time control. Frequency accuracy is improved to 6%. Startup supply current, typically 100μA, is ideal for off-line applications. The output drivers are redesigned to actively sink current during UVLO at no expense to the startup current specification. In addition each output is capable of 2A peak currents during transitions.

Functional improvements have also been implemented in this family. The UC3825 shutdown comparator is now a high-speed overcurrent comparator with a threshold of 1.2V. The overcurrent comparator sets a latch that ensures full discharge of the soft start capacitor before allowing a restart. While the fault latch is set, the outputs are in the low state. In the event of continuous faults, the soft start capacitor is fully charged before discharge to insure that the fault frequency does not exceed the designed soft start period. The UC3825 Clock pin has become CLK/LEB. This pin combines the functions of clock output and leading edge blanking adjustment and has been buffered for easier interfacing.

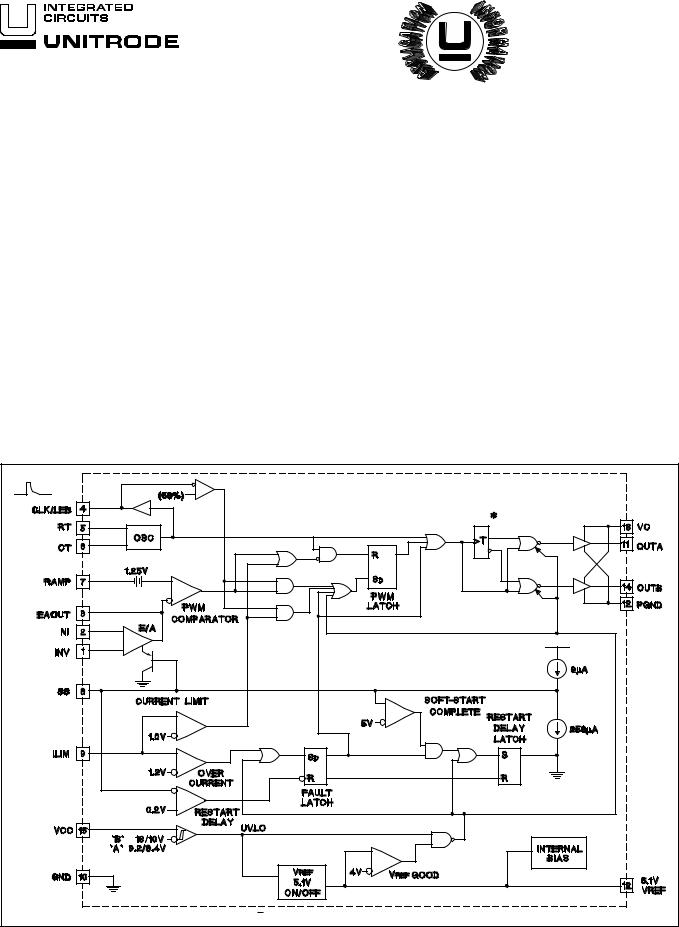

BLOCK DIAGRAM |

continued |

|

|

* Note: 1823A,B Version Toggles Q and Q are always low |

UDG-95101 |

9/95 |

|

DESCRIPTION (cont.)

The UC3825A,B has dual alternating outputs and the same pin configuration of the UC3825. The UC3823A,B outputs operate in phase with duty cycles from zero to less than 100%. The pin configuration of the UC3823A,B is the same as the UC3823 except pin 11 is now an output pin instead of the reference pin to the current limit comparator. “A” version parts have UVLO thresholds identical to the original UC3823/25. The “B” versions have UVLO thresholds of 16 and 10V, intended for ease of use in off-line applications.

Consult Application Note U-128 for detailed technical and applications information. Contact the factory for further packaging and availability information.

Device |

UVLO |

DMAX |

|

|

|

UC3823A |

9.2V/8.4V |

< 100% |

UC3823B |

16V/10V |

< 100% |

UC3825A |

9.2V/8.4V |

< 50% |

UC3825B |

16V/10V |

< 50% |

|

|

|

CONNECTION DIAGRAMS

DIL-16, SOIC-16, (Top View)

J or N Package; DW Package

UC1823A,B/1825A,B |

|

UC2823A,B/2825A,B |

|

UC3823A,B/3825A,B |

|

ABSOLUTE MAXIMUM RATINGS |

|

Supply Voltage (VC, VCC) .................................................... |

22V |

Output Current, Source or Sink (Pins OUTA, OUTB) |

|

DC .................................................................................. |

0.5A |

Pulse (0.5μs) ................................................................... |

2.2A |

Power Ground (PGND) ...................................................... |

±0.2V |

Analog Inputs |

−0.3V to 7V |

(INV, NI, RAMP)................................................... |

|

(ILIM, SS)............................................................. |

−0.3V to 6V |

Clock Output Current (CLK/LEB) ....................................... |

−5mA |

Error Amplifier Output Current (EAOUT).............................. |

5mA |

Soft Start Sink Current (SS) ............................................... |

20mA |

Oscillator Charging Current (RT)........................................ |

−5mA |

Power Dissipation at TA = 60°C.............................................. |

1W |

Storage Temperature Range............................ |

−65°C to +150°C |

Junction Temperature....................................... |

−55°C to +150°C |

Lead Temperature (Soldering, 10 sec.)............................. |

300°C |

All currents are positive into, negative out of the specified terminal. Consult Packaging Section of Databook for thermal limitations and considerations of packages.

PLCC-20, LCC-20, (Top View)

Q, L Packages

ELECTRICAL CHARACTERISTICS Unless otherwise stated, these specifications apply for TA = −55°C to +125°C for the UC1823A,B and UC1825A,B; −40°C to +85°C for the UC2823A,B and UC2825A,B; 0°C to +70°C for the UC3823A,B and UC3825A,B; RT = 3.65k, CT = 1nF, VCC = 12V, TA = TJ.

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

Reference Section |

|

|

|

|

|

Output Voltage |

TJ = 25°C, Io = 1mA |

5.05 |

5.1 |

5.15 |

V |

|

|

|

|

|

|

Line Regulation |

12 < VCC < 20V |

|

2 |

15 |

mV |

|

|

|

|

|

|

Load Regulation |

1mA < Io < 10mA |

|

5 |

20 |

mV |

|

|

|

|

|

|

Total Output Variation |

Line, Load, Temp |

5.03 |

|

5.17 |

V |

|

|

|

|

|

|

Temperature Stability |

TMIN < TA < TMAX (Note 1) |

|

0.2 |

0.4 |

mV/°C |

|

|

|

|

|

|

Output Noise Voltage |

10Hz < f < 10kHz (Note 1) |

|

50 |

|

μVRMS |

|

|

|

|

|

|

Long Term Stability |

TJ = 125°C, 1000 hours (Note 1) |

|

5 |

25 |

mV |

|

|

|

|

|

|

Short Circuit Current |

VREF = 0V |

30 |

60 |

90 |

mA |

|

|

|

|

|

|

2

UC1823A,B/1825A,B

UC2823A,B/2825A,B

UC3823A,B/3825A,B

ELECTRICAL CHARACTERISTICS (cont.) Unless otherwise stated, these specifications apply for TA = −55°C to +125°C for the UC1823A,B and UC1825A,B; −40°C to +85°C for the UC2823A,B and UC2825A,B; 0°C to +70°C for the UC3823A,B and UC3825A,B; RT = 3.65k, CT = 1nF, VCC = 12V, TA = TJ.

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

|

|

|

|

|

|

Oscillator Section |

|

|

|

|

|

|

|

|

|

|

|

Initial Accuracy |

TJ = 25°C (Note 1) |

375 |

400 |

425 |

kHz |

|

|

|

|

|

|

Total Variation |

Line, Temperature (Note 1) |

350 |

|

450 |

kHz |

|

|

|

|

|

|

Voltage Stability |

12V < VCC < 20V |

|

|

1 |

% |

|

|

|

|

|

|

Temperature Stability |

TMIN < TA < TMAX (Note 1) |

|

5 |

|

% |

|

|

|

|

|

|

Initial Accuracy |

RT = 6.6k, CT = 220pF TA = 25°C (Note 1) |

0.9 |

1 |

1.1 |

MHz |

|

|

|

|

|

|

Total Variation |

RT = 6.6k, CT = 220pF (Note 1) |

0.85 |

|

1.15 |

MHz |

|

|

|

|

|

|

Clock Out High |

|

3.7 |

4 |

|

V |

|

|

|

|

|

|

Clock Out Low |

|

|

0 |

0.2 |

V |

|

|

|

|

|

|

Ramp Peak |

|

2.6 |

2.8 |

3 |

V |

|

|

|

|

|

|

Ramp Valley |

|

0.7 |

1 |

1.25 |

V |

|

|

|

|

|

|

Ramp Valley to Peak |

|

1.6 |

1.8 |

2 |

V |

|

|

|

|

|

|

Oscillator Discharge Current |

RT = Open, VCT = 2V |

9 |

10 |

11 |

mA |

|

|

|

|

|

|

Error Amplifier Section |

|

|

|

|

|

|

|

|

|

|

|

Input Offset Voltage |

|

|

2 |

10 |

mV |

|

|

|

|

|

|

Input Bias Current |

|

|

0.6 |

3 |

μA |

|

|

|

|

|

|

Input Offset Current |

|

|

0.1 |

1 |

μA |

|

|

|

|

|

|

Open Loop Gain |

1V < Vo < 4V |

60 |

95 |

|

dB |

|

|

|

|

|

|

CMRR |

1.5V < VCM < 5.5V |

75 |

95 |

|

dB |

|

|

|

|

|

|

PSRR |

12V < VCC < 20V |

85 |

110 |

|

dB |

|

|

|

|

|

|

Output Sink Current |

VEAOUT = 1V |

1 |

2.5 |

|

mA |

|

|

|

|

|

|

Output Source Current |

VEAOUT = 4V |

−0.5 |

−1.3 |

|

mA |

|

|

|

|

|

|

Output High Voltage |

IEAOUT = −0.5mA |

4.5 |

4.7 |

5 |

V |

|

|

|

|

|

|

Output Low Voltage |

IEAOUT = 1mA |

0 |

0.5 |

1 |

V |

|

|

|

|

|

|

Gain Bandwidth Product |

F = 200kHz |

6 |

12 |

|

MHz |

|

|

|

|

|

|

Slew Rate |

(Note 1) |

6 |

9 |

|

V/μs |

|

|

|

|

|

|

PWM Comparator |

|

|

|

|

|

RAMP Bias current |

VRAMP = 0V |

|

−1 |

−8 |

μA |

|

|

|

|

|

|

Minimum Duty Cycle |

|

|

|

0 |

% |

|

|

|

|

|

|

Maximum Duty Cycle |

|

85 |

|

|

% |

|

|

|

|

|

|

Leading Edge Blanking |

R = 2k, C = 470pF |

300 |

375 |

450 |

ns |

LEB Resistor |

VCLK/LEB = 3V |

8.5 |

10 |

11.5 |

kohm |

|

|

|

|

|

|

EAOUT Zero D.C. Threshold |

VRAMP = 0V |

1.1 |

1.25 |

1.4 |

V |

|

|

|

|

|

|

Delay to Output |

VEAOUT = 2.1V, VRAMP = 0 to 2V Step (Note 1) |

|

50 |

80 |

ns |

Current Limit/Start Sequence/Fault Section |

|

|

|

|

|

Soft Start Charge Current |

VSS = 2.5V |

8 |

14 |

20 |

μA |

|

|

|

|

|

|

Full Soft Start Threshold |

|

4.3 |

5 |

|

V |

|

|

|

|

|

|

Restart Discharge Current |

VSS = 2.5V |

100 |

250 |

350 |

μA |

|

|

|

|

|

|

Restart Threshold |

|

|

0.3 |

0.5 |

V |

|

|

|

|

|

|

ILIM Bias Current |

0 < VILIM < 2V |

|

|

15 |

μA |

|

|

|

|

|

|

Current Limit Threshold |

|

0.95 |

1 |

1.05 |

V |

|

|

|

|

|

|

3

Loading...

Loading...