Texas Instruments UC3727N, UC3727DWPTR, UC3727DWP, UC2727N, UC2727J Datasheet

...

UC1727

UC2727

UC3727

Isolated High Side IGBT Driver

FEATURES

∙Receives Power and Signal from Single Isolation Transformer

∙Generates Split Rail for 4A Peak Bipolar Gate Drive

∙16V High Level Gate Drive

∙Low Level Gate Drive more Negative than -5V

∙Undervoltage Lockout

∙Desaturation Detection and Fault Processing

∙Separate Output Enable Input

∙Programmable Stepped Gate Drive for Soft Turn On

∙Programmable Stepped Gate Drive for Soft Fault

DESCRIPTION

The UC1727 and its companion chip, the UC1726, provide all the necessary features to drive an isolated IGBT transistor from a TTL input signal. A unique modulation scheme is used to transmit both power and signal across an isolation boundary with a minimum of external components.

Protection features include under voltage lockout and desaturation detection. High level gate drive signals are typically 16V. Intermediate high drive levels can be programmed for various periods of time to limit surge current at turn on and in the event of desaturation due to a short circuit.

The chip generates a bipolar supply so that the gate can be driven to a negative voltage insuring the IGBT remains off in the presence of high common mode slew rates.

Uses include isolated off-line full bridge and half bridge drives for motors, switches, and any other load requiring full electrical isolation.

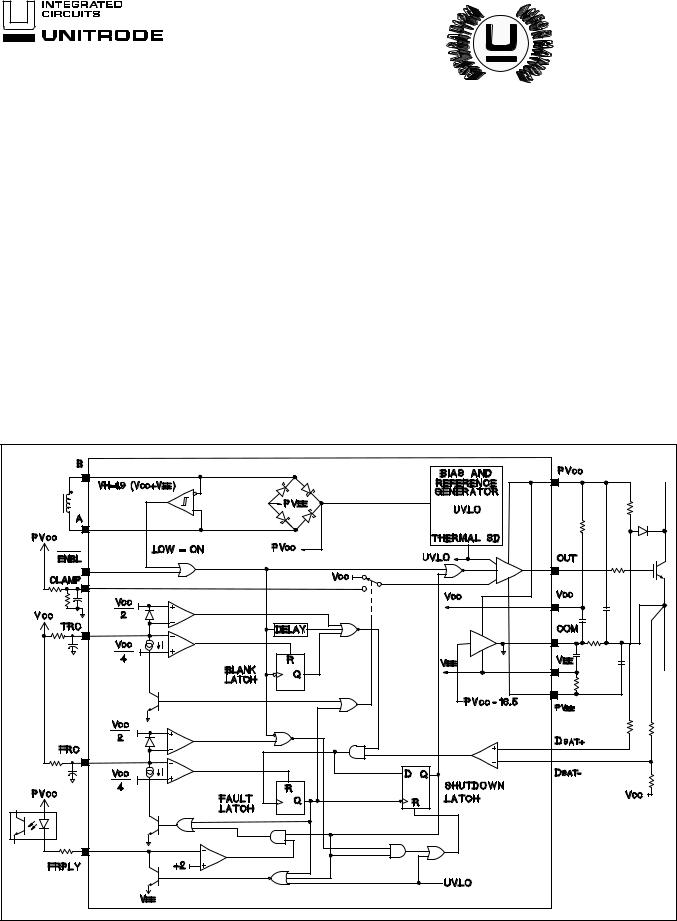

BLOCK DIAGRAM

UDG-94005-2 |

12/94 |

ABSOLUTE MAXIMUM RATINGS

Supply voltage (VCC - VEE). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40V Power Inputs (|A - B|) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45V Analog Input Voltage (ENBL, CLAMP). . . . . . . . . . . . . . . . . . -0.3 To Vcc+0.3 Analog Input Voltage (DSAT+, DSAT-) . . . . . . . . . . . . . . . . VEE-0.3 to VCC+0.3 Analog Input Current (DSAT+, DSAT-) . . . . . . . . . . . . . . . . . . . . . . -10 to 10mA Output Current, ½(OUT)½

DC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0.8A Pulse (0.5ms) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4A FRPLY Output Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30mA

Note: All voltages are with respect to COM. Currents are positive into the specified terminal.

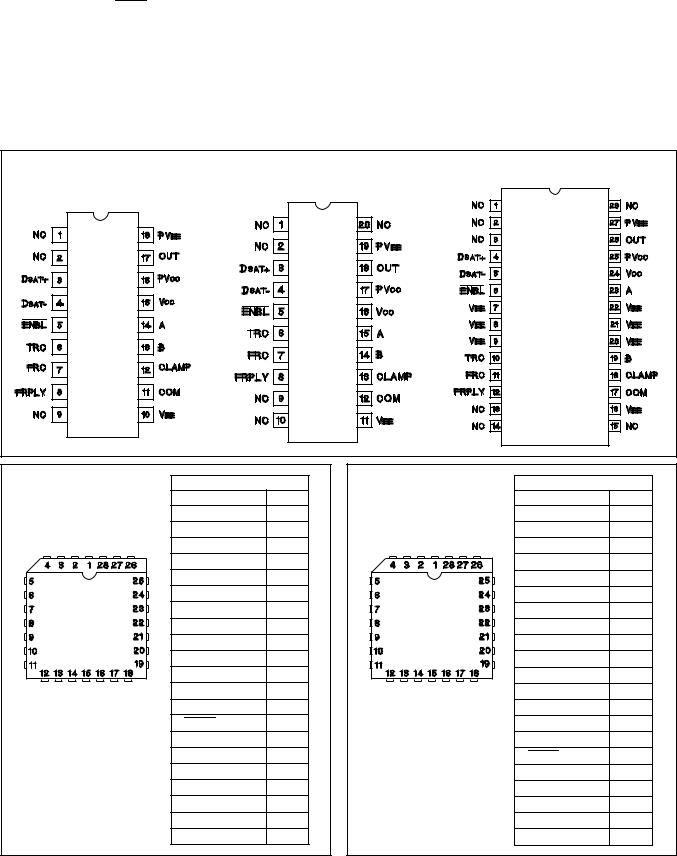

CONNECTION DIAGRAMS

UC1727

UC2727

UC3727

DIL-18 (Top View) |

DIL-20 (Top View) |

SOIC-28 (Top View) |

J Package |

N Package |

DWP Package |

PLCC-28 (Top View) |

PACKAGE PIN FUNCTION |

||

QP Package |

|||

FUNCTION |

PIN |

||

|

N/C |

1 |

|

|

VEE |

2 |

|

|

N/C |

3-4 |

|

|

COM |

5 |

|

|

CLAMP |

6 |

|

|

B |

7 |

|

|

A |

8 |

|

|

VCC |

9 |

|

|

PVCC |

10 |

|

|

OUT |

11 |

|

|

PVEE |

12-18 |

|

|

DSAT+ |

19 |

|

|

DSAT- |

20 |

|

|

ENBL |

21 |

|

|

NC |

22 |

|

|

TRC |

23 |

|

|

FRC |

24 |

|

|

FRPLY |

25 |

|

|

N/C |

26 |

|

|

N/C |

27 |

|

|

N/C |

28 |

|

LCC-28 (Top View) |

PACKAGE PIN FUNCTION |

||

LP Package |

|||

FUNCTION |

PIN |

||

|

|||

|

N/C |

1 |

|

|

VEE |

2 |

|

|

N/C |

3-4 |

|

|

COM |

5 |

|

|

CLAMP |

6 |

|

|

B |

7 |

|

|

A |

8 |

|

|

VCC |

9 |

|

|

PVCC |

10 |

|

|

OUT |

11 |

|

|

N/C |

12-13 |

|

|

PVEE |

14 |

|

|

N/C |

15-18 |

|

|

DSAT+ |

19 |

|

|

DSAT- |

20 |

|

|

ENBL |

21 |

|

|

NC |

22 |

|

|

TRC |

23 |

|

|

FRC |

24 |

|

|

FRPLY |

25 |

|

|

N/C |

26-28 |

|

2

UC1727

UC2727

UC3727

See Application Note U-143A "New Chip Pair Provides Isolated Drive for High Voltage IGBTs"

PIN DESCRIPTIONS

A, B: Signal and power input pins. Connect these pins to the secondary of the transformer driven by UC1726.

CLAMP: Analog programming pin for intermediate drive level to be used at turn on or in response to a desaturation event. Requires a bypass capacitor to COM.

COM: Self generated common for bipolar supply. This pin will be 16.5V below PVCC.

DSAT+, DSAT-: Inputs to the desaturation comparator. Desaturation is detected when DSAT+ is greater than DSAT-.

ENBL: Negative true enable input. Tie to VCC to disable the chip. Connect to COM to enable the chip. If the ENBL pin is used as the primary input to the chip, connect B to VCC and A to VEE.

FRC: Fault Resistor and Capacitor. Programs the duration that OUT will be held at CLAMP potential during a desaturation event before it is driven fully low. Also sets the period of time that OUT will be held low before allowing it to be driven high again.

FRPLY: Fault Reply pin. Open collector output. Normally connected to VEE. When desaturation is detected, the pin opens.

OUT: Gate drive output. Connect to gate of IGBT with a series damping resistor greater than 3 ohms.

TRC: Timing Resistor and Capacitor. Programs the duration that OUT will be held at CLAMP potential and the period of time the desaturation comparator will be ignored during the rising edge.

VCC: Positive supply voltage. Bypass to COM with a low ESL/ESR 1μF capacitor.

VEE: Negative supply voltage. Bypass to COM with a low ESL/ESR 1μF capacitor.

PVEE: Output driver negative supply. Connect to VEE with a 3.3 ohm resistor and bypass to COM with a low ESL/ESR 1μF capacitor.

PVCC: Output driver positive supply. Connect to VCC with a 3.3 ohm resistor and bypass to COM with a low ESL/ESR 1μF capacitor.

ELECTRICAL CHARACTERISTICS: Unless otherwise stated, these specifications apply for TA = -55°C to 125°C for the UC1727, TA = -40°C to 85°C for the UC2727, TA = 0°C to 70°C for the UC3727,

R(TRC) = 54.9k, C(TRC) = 180pF, R(FRC) = 309K, C(FRC) = 200pF, VCC - VEE = 25V, CLAMP = 9V, TA = TJ, and all voltages are measured with respect to COM.

PARAMETER |

|

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNITS |

Power Input Receivers |

|

|

|

|

|

|

Forward Diode Drop |

IF = 50mA |

|

0.5 |

0.65 |

V |

|

|

IF = 500mA |

|

1.2 |

2 |

V |

|

VCC Regulator |

|

|

|

|

|

|

VCC |

25 £ (VCC - VEE) £ 36V,½I(COM)½ £ 15mA |

15.5 |

16.5 |

17.5 |

V |

|

Hysteresis Comparator |

|

|

|

|

|

|

Input Open Circuit Voltage |

(Measured with respect to VEE) |

|

12 |

|

V |

|

Input Impedance |

|

|

|

100 |

|

kW |

Hysteresis |

|

|

44 |

47 |

50 |

V |

Enable Input |

|

|

|

|

|

|

High Level Input Voltage |

|

|

12 |

|

|

V |

Low Level Input Voltage |

|

|

|

|

5 |

V |

Input Bias Current |

|

|

|

-460 |

-900 |

mA |

ENBL = COM |

|

|||||

Output Driver |

|

|

|

|

|

|

Saturation to VCC |

I(OUT) = -20mA |

|

1.7 |

2.3 |

V |

|

Saturation to VCC |

I(OUT) = -500mA |

|

2 |

2.5 |

V |

|

Saturation to VEE |

I(OUT) = 20mA |

|

2 |

3 |

V |

|

Saturation to VEE |

I(OUT) = 500mA |

|

2.4 |

3.6 |

V |

|

|

|

|

|

|

|

|

3

Loading...

Loading...