Analog Devices AD28MSP01KST, AD28MSP01KR, AD28MSP01KN Datasheet

a PSTN Signal Port

AD28msp01

FEATURES

Complete Analog l/O Port for DSP-Based FAX/MODEM Applications

Linear-Coded 16-Bit Sigma-Delta ADC

Linear-Coded 16-Bit Sigma-Delta DAC On-Chip Anti-Alias and Anti-lmage Filters Digital Resampling/lnterpolation Filter

7.2 kHz, 8.0 kHz, and 9.6 kHz Sampling Rates 8/7 Mode for 8.23 kHz, 9.14 kHz, and 10.97 kHz

Sampling Rates

Synchronous and Asynchronous DAC/ADC Modes Bit and Baud Clock Generation

Transmit Digital Phase-Locked Loop for Terminal Synchronization

Independent Transmit and Receive Phase Adjustment Serial Interface to DSP Processors

+5 V Operation with Power-Down Mode 28-Pin Plastic DlP/44-Lead PLCC/28-Lead SOIC

APPLICATIONS

High Performance DSP-Based Modems

V.32ter, V.32bis, V.32, V.22bis, V.22, V.21,

Bell 212A, 103

Fax and Cellular-Compatible Modems

V.33, V.29, V.27ter, V.27bis, V.27, V.26bis

Integrated Fax, Modem, and Speech Processing

GENERAL DESCRIPTION

The AD28msp01 is a complete analog front end for high performance DSP-based modems. The device includes all data conversion, filtering, and clock generation circuitry needed to implement an echo-cancelling modem with a single host digital signal processor. Software-programmable sample rates and clocking modes support all established modem standards. The AD28msp01 simplifies overall system design by requiring only +5 volts.

The inclusion of on-chip anti-aliasing and anti-imaging filters and 16-bit sigma-delta ADC and DAC ensures a highly integrated and compact solution for FAX or data MODEM applications. Sigma-delta conversion technology eliminates the need for complex off-chip anti-aliasing filters and sample-and-hold circuitry.

The AD28msp01 utilizes advanced sigma-delta technology to move the entire echo-cancelling modem implementation into the digital domain. The device maintains a –72 dB SNR throughout all filtering and data conversion. Purely DSP-based echo cancellation algorithms can thereby maintain robust bit error rates under worst-case signal attenuation and echo amplitude conditions. The AD28msp01’s on-chip interpolation filter resamples the received signal after echo cancellation in the DSP, freeing the processor for other voice or data communications tasks.

REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

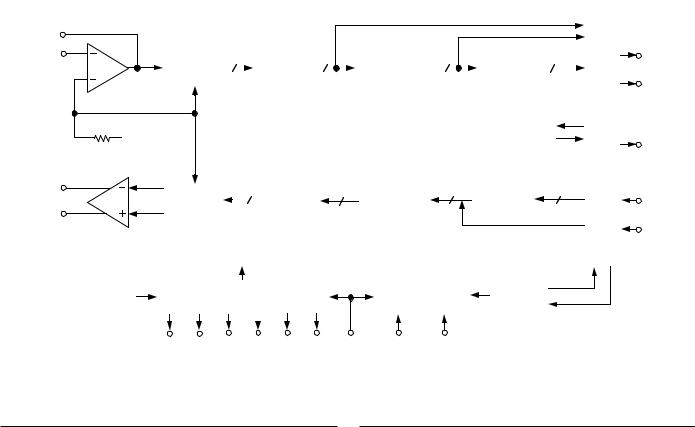

FUNCTIONAL BLOCK DIAGRAM

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-BIT |

|

|

|

|

|

|

|||

ANALOG |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

SIGMA-DELTA |

|

|

|

|

|

|

|||||||

INPUTS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

ADC |

|

|

|

|

|

DIGITAL |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DATA AND |

|

|

|

|

|

|

|

|

|

|

|

|

RESAMPLING |

|

|

|

CONTROL |

||||

|

|

|

|

VOLTAGE |

|

|

|

SERIAL |

||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

INTERPOLATION |

|

|

|

||||||||||||

|

|

|

REFERENCE |

|

|

|

PORT |

|

||||||||||||

|

|

|

|

FILTER |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

DIFFERENTIAL |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

16-BIT |

|

|

|

|

|

|

||||||

|

ANALOG |

|

|

|

|

|

|

|

SIGMA-DELTA |

|

|

|

|

|

|

|||||

|

OUTPUT |

|

|

|

|

|

|

|

|

|

DAC |

|

|

|

|

|

|

|||

CLOCK INPUTS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

CLOCK |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

CLOCK OUTPUTS |

|

|

|

|

|

|

|

GENERATION |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On-chip bit and baud clock generation circuitry provides for either synchronous or asynchronous operation of the transmit (DAC) and receive (ADC) paths. Each path features independent phase advance and retard adjustments via software control. The AD28msp01 can also synchronize modem operation to an external terminal bit clock.

The AD28msp01’s serial I/O port provides an easy interface to host DSP microprocessors such as the ADSP-2101, ADSP-2105, and ADSP-2111. Packaged in a 28-pin plastic DIP, 44-lead PLCC, 44-pin TQFP, or 28-lead SOIC, the AD28msp01 provides a compact solution for space-constrained environments. The device operates from a +5 V supply and offers a low power sleep mode for battery-powered systems.

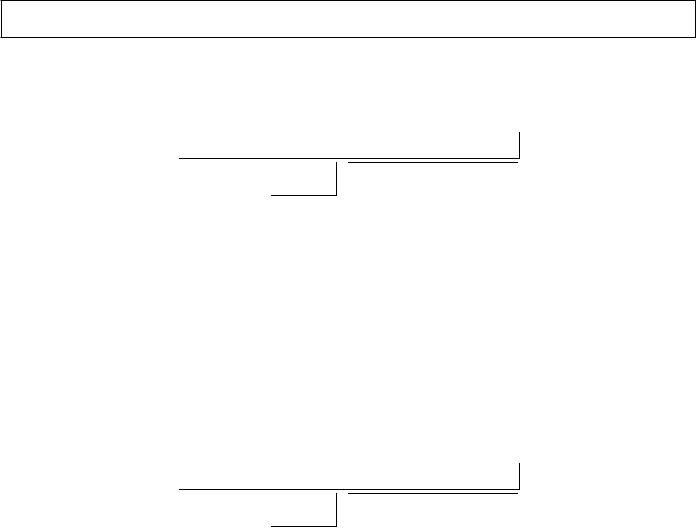

A detailed block diagram of the AD28msp01 is shown in Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

AD28msp01

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-BIT SIGMA-DELTA ADC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VFB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDOFS |

INPUT |

|

|

|

|

ANALOG |

|

1 |

|

|

DIGITAL |

|

16 |

|

|

|

|

DIGITAL |

|

16 |

|

|

|

DIGITAL |

|

|

16 |

|

|

|

|

|||||||

|

|

|

|

SIGMA-DELTA |

|

|

|

|

DECIMATION |

|

|

|

|

|

ANTI-ALIASING |

|

|

|

|

HIGH-PASS |

|

|

|

|

|

|

|

|

|||||||||

|

AMP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDO |

||||||||||||

|

|

|

|

MODULATOR |

|

|

|

|

FILTER |

|

|

|

|

|

LOW-PASS FILTER |

|

|

|

|

|

|

FILTER |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

1.728 MHz |

28.8/32.0/38.4 kHz |

|

|

7.2/8.0/9.6 kHz |

|

|

7.2/8.0/9.6 kHz |

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

500kΩ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESAMPLING |

|

|

|

|

||||||

|

VOLTAGE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTERPOLATION |

|

|

|

SCLK |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

REFERENCE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FILTER |

|

|

|

|

SERIAL |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PORT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-BIT SIGMA-DELTA DAC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VOUT+ |

|

|

|

|

|

|

|

ANALOG |

|

1 |

|

|

DIGITAL |

|

16 |

|

|

|

DIGITAL |

16 |

|

|

|

DIGITAL |

|

16 |

|

|

SDI |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ANTI-IMAGING |

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

SMOOTHING |

|

|

|

|

SIGMA-DELTA |

|

|

|

|

INTERPOLATION |

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOW-PASS |

|

|

|

|

|

|

|

|||||||||||

VOUT– |

|

|

|

|

|

|

|

|

FILTER |

|

|

|

|

MODULATOR |

|

|

|

|

|

FILTER |

|

|

|

|

|

|

FILTER |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

OUTPUT |

|

|

|

|

|

|

1.728 MHz |

|

|

1.728 MHz |

|

28.8/32.0/38.4 kHz |

|

|

7.2/8.0/9.6 kHz |

|

|

SDIFS |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

DIFF. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

AMP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

INTERNAL CLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONTROL CIRCUITRY |

|

|

|

|

CONTROL |

|

|

|

|

|

|

||||

|

|

TSYNC |

|

|

|

CLOCK GENERATION |

|

|

|

|

|

|

|

AND |

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

REGISTERS |

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SEQUENCER |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

tCONV |

tBAUD |

tBIT |

rCONV rBAUD |

rBIT |

MCLK |

|

RESET |

|

CS |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Figure 1. AD28msp01 Block Diagram

PIN DESCRIPTIONS

Name |

Type |

Description |

|

||

Analog Interface |

||

VIN |

I |

Analog input to the inverting terminal of the |

|

|

input amplifier. |

VFB |

O |

Feedback terminal of the input amplifier. |

VOUTP |

O |

Analog output from the noninverting terminal |

|

|

of the output differential amplifier. |

VOUTN |

O |

Analog output from inverting terminal of the |

|

|

output differential amplifier. |

Serial Interface |

|

|

SCLK |

O/Z |

Serial clock used for clocking data or control |

|

|

bits to/from the serial port (SPORT). The |

|

|

frequency of this clock is 1.7280 MHz. This |

|

|

pin is 3-stated when the CS is low. |

SDI |

I |

Serial data input of the SPORT. Both data |

|

|

and control information are input on this pin. |

|

|

This pin is ignored when CS is low. |

SDO |

O/Z |

Serial data output of the SPORT. Both data |

|

|

and control information are output on this |

|

|

pin. This pin is 3-stated when CS is low. |

SDIFS |

I |

Framing synchronization signal for serial data |

|

|

transfers to the AD28msp01 (via the SDI |

|

|

pin). This pin is ignored when CS is low. |

|

|

|

Name |

Type Description |

|

|

|

|

SDOFS |

O/Z |

Framing synchronization signal for serial data |

|

|

transfers from the AD28msp01 (via the SDO |

|

|

pin). This pin is 3-stated when CS is low. |

Clock Generation |

||

TSYNC |

I |

Transmit synchronization clock. This signal is |

|

|

used to synchronize the transmit clocks and |

|

|

the converter clocks to an external terminal/ |

|

|

bit-rate clock. It is used in the V.32 TSYNC |

|

|

and Asynchronous TSYNC modes and is |

|

|

ignored in other operating modes. The |

|

|

frequency of the external clock must be |

|

|

programmed in Control Register 0. This pin |

|

|

must be tied high or low if it is not being |

|

|

used. |

TBIT |

O |

Transmit bit rate clock. This is an output |

|

|

clock whose frequency is programmable via |

|

|

Control Register 3. It is synchronized with |

|

|

the TCONV clock. |

TBAUD |

O |

Transmit baud rate clock. This is an output |

|

|

clock whose frequency is programmable via |

|

|

Control Register 3. It is synchronized with |

|

|

the TCONV clock. |

|

|

|

–2– |

REV. A |

AD28msp01

PIN DESCRIPTIONS (Continued)

Name |

Type |

Description |

||||

|

|

|

|

|

|

|

TCONV |

O |

Transmit conversion clock. This clock indicates |

||||

|

|

|

when the ADC has finished a sampling cycle. |

|||

|

|

|

The frequency of TCONV is programmed by |

|||

|

|

|

setting the sample rate field in Control Register |

|||

|

|

|

0. The programmed TCONV rate can be scaled |

|||

|

|

|

by a factor of 8/7 by setting Bit 9 in Control |

|||

|

|

|

Register 1. The phase of TCONV can be |

|||

|

|

|

adjusted by writing the Transmit Phase Adjust |

|||

|

|

|

Register (Control Register 5). |

|||

RBIT |

O |

Receive bit rate clock. This is an output clock |

||||

|

|

|

whose frequency is programmable via Control |

|||

|

|

|

Register 2. It is synchronized with the RCONV |

|||

|

|

|

clock. |

|||

RBAUD |

O |

Receive baud rate clock. This is an output clock |

||||

|

|

|

whose frequency is programmable via Control |

|||

|

|

|

Register 2. It is synchronized with the RCONV |

|||

|

|

|

clock. |

|||

RCONV |

O |

Receive conversion clock. This clock indicates |

||||

|

|

|

when the DAC has finished a sampling cycle. |

|||

|

|

|

The frequency of RCONV is programmed by |

|||

|

|

|

setting the sample rate field in Control Register |

|||

|

|

|

0. The programmed RCONV rate can be scaled |

|||

|

|

|

by a factor of 8/7 by setting Bit 9 in Control |

|||

|

|

|

Register 1. The phase of RCONV can be |

|||

|

|

|

adjusted by writing the Receive Phase Adjust |

|||

|

|

|

Register (Control Register 4). |

|||

Miscellaneous |

|

|

|

|

||

MCLK |

I |

AD28msp01 master clock input. The frequency |

||||

|

|

|

of this clock must be 13.824 MHz to guarantee |

|||

|

|

|

listed specifications. |

|||

RESET |

|

I |

Active-low chip reset. This signal sets all |

|||

|

|

|

AD28msp01 control registers to their default |

|||

|

|

|

values and clears the device’s digital filters. |

|||

|

|

|

SPORT output pins are 3-stated when |

RESET |

|

|

|

|

|

is low. SPORT input pins are ignored when |

|||

|

|

|

RESET |

is low. |

||

CS |

I |

Active-high chip select. This signal 3-states all |

||||

|

|

|

SPORT output pins and forces the AD28msp01 |

|||

|

|

|

to ignore all SPORT input pins. If CS is |

|||

|

|

|

deasserted during a serial data transfer, the |

|||

|

|

|

16-bit word being transmitted is lost. |

|||

Power Supplies |

|

|

|

|

||

VCC |

|

Analog supply voltage (nominally +5 V) |

||||

GNDA |

|

Analog ground |

||||

VDD |

|

Digital supply voltage (nominally +5 V) |

||||

GNDD |

|

Digital ground |

||||

FUNCTIONAL DESCRIPTION A/D Conversion

The A/D conversion circuitry of the AD28msp01 consists of an analog input amplifier and a sigma-delta analog-to-digital converter (ADC). The analog input signal to the AD28msp01 must be ac coupled.

Analog Input Amplifier

The analog input amplifier is internally biased by an on-chip voltage reference in order to allow operation of the AD28msp01 with a +5 V power supply.

Input signal level to the sigma-delta modulator should not ex-

ceed VINMAX, which is specified under “Analog Interface Electrical Characteristics.” Refer to “Analog Input” in the “Design

Considerations” section of this data sheet for more information.

ADC

The ADC consists of a 3rd-order analog sigma-delta modulator, a decimation filter, an anti-aliasing low-pass filter, and a highpass filter. The analog input is applied to the input amplifier. The output of this amplifier is applied to an analog sigma-delta modulator which noise-shapes it and produces 1-bit samples at a 1.7280 MHz rate. This bit stream is fed to the decimation filter, which increases the resolution to 16-bits and decreases the sampling frequency. The parallel data stream is then processed by the anti-aliasing low-pass filter which further reduces the sampling rate. Finally, the high-pass filter removes input frequency components at the low end of the spectrum.

Either the high-pass filter alone or the high-pass/anti-aliasing low-pass filter combination can be bypassed by setting the appropriate bits in Control Register 1, thus producing samples at 7.2/8.0/9.6 kHz or 28.8/32.0/38.4 kHz, respectively. The gain and the frequency response of the AD28msp01 are altered when these filters are bypassed. The DSP processor that receives samples from the AD28msp01 may need to compensate for this change.

Decimation Filter

The decimation filter is a sinc4 digital filter that increases resolution to 16 bits and reduces the sample rate to 28.8, 32.0, or 38.4 kHz (depending on the input sample rate). The 16 bit, parallel data stream output of the decimation filter is then processed by the anti-aliasing low-pass filter.

Anti-Aliasing Low-Pass Filter

The anti-aliasing low-pass filter further reduces the sampling rate by a factor of four to 7.2 kHz, 8.0 kHz, or 9.6 kHz (depending on the output sample rate of the decimation filter). The output is fed to the high-pass filter. The low-pass/high-pass filter combination can be bypassed by setting the appropriate bits in Control Register 1. If the filters are bypassed, the signal must be scaled by the following multipliers to achieve normal levels: 2.046 for 9.6 kHz, 0.987 for 8.0 kHz, and 0.647 for 7.2 kHz.

When the filters are bypassed, the host DSP must be able to receive data at the 28.8/32.0/38.4 kHz rates. In this case, resampling interpolation should be disabled because of insufficient bandwidth to transmit both ADC and resampled data to the SPORT.

High-Pass Filter

The digital high-pass filter removes frequency components at the low end of the spectrum. The high pass filter can be bypassed by setting the appropriate bits in Control Register 1.

REV. A |

–3– |

AD28msp01

The output of the ADC is transferred to the AD28msp01’s serial port (SPORT) for transmission to the host DSP processor.

D/A CONVERSION

The D/A conversion circuitry of the AD28msp01 consists of a sigma-delta digital-to-analog converter (DAC) and a differential output amplifier.

DAC

The DAC consists of an anti-imaging low-pass filter, an interpolation filter, a digital sigma-delta modulator, and an analog smoothing filter. These filters have the same characteristics as the ADC’s anti-aliasing filter and decimation filter.

The DAC receives 16-bit samples from the host DSP processor via AD28msp01’s SPORT. If the host processor fails to write a new value to the serial port, the existing (previous) data is read again. The data stream is filtered first by the DAC’s antiimaging low-pass filter and then by the interpolation filter. The output of the interpolation filter is fed to the DAC’s digital sigma-delta modulator, which converts the 16-bit data to 1-bit samples. The output of the sigma-delta modulator is fed to the AD28msp01’s analog smoothing filter where it is converted into a low-pass filtered, analog voltage.

Anti-lmaging Low-Pass Filter

The anti-imaging low-pass filter filters the 7.2 kHz, 8.0 kHz, or 9.6 kHz data stream form the SPORTs, and raises the sampling rate to 28.8 kHz, 32.0 kHz, or 38.4 kHz.

The anti-imaging low-pass filter can be bypassed by setting the appropriate bit in Control Register 1. This results in a gain change. If the filter is bypassed, the signal must be scaled by the following multipliers to achieve normal levels: 2.046 for 9.6 kHz, 0.987 for 8.0 kHz, and 0.647 for 7.2 kHz.

When the filter is bypassed, the host DSP must be able to transmit data at the 28.8/32.0/38.4 kHz rates. In this case, resampling interpolation should be disabled because of insufficient bandwidth to transmit both ADC and resampled data to the SPORT.

Interpolation Filter

The interpolation filter contains is a sinc4 digital filter which raises the sampling rate to 1.7280 MHz by interpolating between the samples. These 16-bit samples are then processed by the digital sigma-delta modulator which noise-shapes the data stream and reduces the sample width to a single bit stream.

Analog Smoothing Filter

The AD28msp01’s analog smoothing filter consists of a 2ndorder Sallen-Key continuous-time filter and a 3rd-order switched capacitor filter. The Sallen-Key filter has a 3 dB point at approximately 80 kHz.

The analog smoothing filter converts the 1.7280 MHz bit stream output of the sigma-delta modulator into a low-pass filtered, differential analog signal.

Differential Output Amplifier

The differential output amplifier produces the AD28msp01’s

analog output (VOUTP, VOUTN). It can drive loads of 2 kΩ or greater and has a maximum differential output voltage swing of

6.312 V peak-to-peak. The output signal is dc biased to the AD28msp01’s on-chip voltage reference (2.5 V nominal) and can be ac coupled directly to a load or dc coupled to an external

amplifier. Refer to “Analog Output” in the “Design Considerations” section of this data sheet for more information.

The VOUTP and VOUTN outputs must be used as differential outputs; do not use either as a single-ended output.

SERIAL PORT

The AD28msp01 includes a full-duplex synchronous serial port (SPORT) used to communicate with a host processor. The SPORT is used to read and write all data and control registers in the AD28msp01. The SPORT transfers 16-bit words, MSB first, at a serial clock rate of 1.7280 MHz.

When the AD28msp01 exits reset, both the analog circuitry and the digital circuitry are powered down. The serial port will not transmit data to the host until the host sets the digital powerdown bit (PWDD) to 1 in Control Register 1. All control registers should be initialized before this bit is set.

The SPORT is configured for an externally generated receive frame sync (SDIFS), an internally generated serial clock (SCLK), and an internally generated transmit frame sync (SDOFS). The host processor should be configured for an external serial clock and receive frame sync and an internal transmit frame sync.

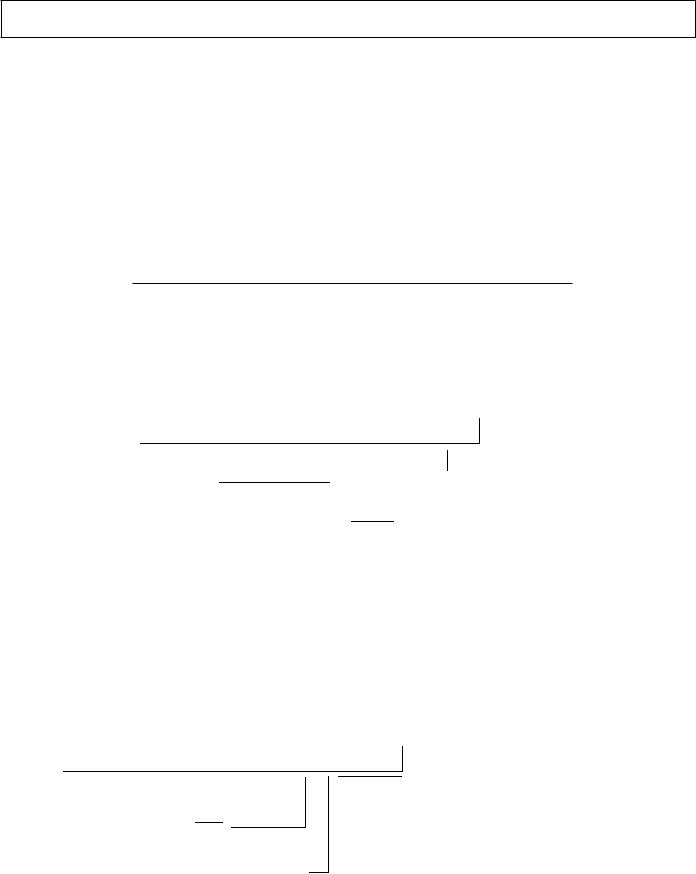

DSP Processor Interface

The AD28msp01-to-host processor interface is shown in Figure 2.

AD28msp01 |

|

DSP PROCESSOR |

SDO |

|

SERIAL DATA RECEIVE |

SDOFS |

|

RECEIVE FRAME SYNC |

SCLK |

|

SERIAL CLOCK |

CS |

|

FLAG |

SDI |

|

SERIAL DATA TRANSMIT |

SDIFS |

|

TRANSMIT FRAME SYNC |

|

|

|

Figure 2. AD28msp01-to-DSP Processor Interface

The AD28msp01’s chip select (CS) must be held high to enable SPORT operation. CS can be used to 3-state the SPORT pins and disable communication with the host processor.

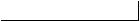

To use the ADSP-2101 or ADSP-2111 as host DSP processor for the AD28msp01, refer to Figure 3.

Note that the ADSP-2101’s SPORT0 communicates with the AD28msp01’s SPORT while the ADSP-2101’s Flag Output (FO) is used to signal the AD28msp01’s CS input. SPORT1 on the ADSP-2101 must be configured for flags and interrupts in this system.

AD28msp01 |

ADSP-2101 |

SDO  DR0

DR0

SDOFS  RFS0

RFS0

SCLK  SCLK0

SCLK0

CS  FO

FO

SDI  DT0

DT0

SDIFS  TFS0

TFS0

Figure 3. AD28msp01-to-ADSP-2101 Interface

Figure 4 shows an ADSP-2101 assembly language program that initializes the AD28msp01 and implements a digital loopback through the processor.

–4– |

REV. A |

AD28msp01

{This ADSP-2101 program initializes the AD28msp01} {and executes a loopback, or talk-through, routine.}

. MODULE/RAM/BOOT = 0 MSP01;

. VAR/DM/CIRC rec[2];

. VAR/DM/CIRC trans[2];

rset: |

JUMP start; |

|

RTI; RTI; RTI; |

irq2v: |

RTI; RTI; RTI; RTI; |

sprt0t: |

AX0 = 0x25; DM(0x3ff3) = AX0; |

|

RTI; RTI; |

sprt0r: |

JUMP receive; |

|

RTI; RTI; RTI; |

sprt1t: |

RTI; RTI; RTI; RTI; |

sprt1r: |

RTI; RTI; RTI; RTI; |

timerv: |

RTI; RTI; RTI; RTI; |

start: |

|

|

I2 = ^re c ; |

|

L2 = %rec; |

|

I3 = ^trans; |

|

L3 = %trans; |

|

M0 = 0; |

|

M1 = 1; |

|

S1 = 0; |

|

DM(0x3000) = SI; |

init dsp: |

|

|

AX0 = 0x2a0f; |

|

DM(0x3ff6) = AX0; |

|

AX0 = 0x101f; |

|

DM(0x3fff) = AX0; |

init msp01: |

|

|

IMASK = 0x10; |

|

AR = 0; |

|

CNTR = 6; |

|

DO initi UNTIL CE; |

|

TX0 = AR; |

|

IDLE; |

|

TX0 = SI; |

|

IDLE; |

|

AY0 = AR; |

initi: |

AR = AY0 +1; |

|

AX1 = 1; |

|

AR = 0x18; |

|

TX0 = AX1; |

|

IDLE; |

|

TX0 = AR; |

|

AR = B#0025; |

|

DM(0x3ff3) = AR; |

|

IMASK = 0x18; |

wait: |

JUMP wait; |

receive: |

|

|

DM(0x3ff3) = SI; |

|

AX1= DM(I2, M1); |

{Receive word buffer} {Transmit word buffer} {lnterrupt Vectors}

{Disable TX autobuffer}

{Initialize DAGs}

{Reset the AD28msp01}

{Initialize the ADSP-2101}

{Ext RFS, Int TfS, Ext SCLK, SLEN = 15} {SPORT0 control register}

{Enable SPORT0} {System control register}

{Initialize AD28msp01 control register} {Note: This section could be autobuffered.} {Enable SPORT0 TX interrupt}

{Transmit address}

{Transmit control word}

{Increment address}

{Power up AD28msp01}

{Enable RX autobuffering with I2, M1} {Autobuffer control register}

{Enable RX and TX interrupt} {Wait for receive interrupt}

{Receive Interrupt Routine}

{Disable autobuffering}

{Read first receive word from buffer}

REV. A |

–5– |

AD28msp01

AX0 = DM(I2, M1); |

{Read data word} |

AY0 = 8; |

{Verify AD28msp01 address = 8} |

AR = AX1 – AY0; |

|

IF EQ JUMP goodstuff; |

|

RTI; |

|

goodstuff; |

|

MODIFY (I3, M1); |

{Point to second word of TX buffer} |

DM(I3, M0) = AX0; |

|

MX1 = 6; |

{Load address word into MX1} |

AR = 0x06a7; |

{Enable TX and RX autobuffer} |

DM(0x3ff3) = AR; |

{Write to SPORT control Register} |

TX0 = MX1; |

{Autobuffer start} |

RTI; |

|

.ENDMOD; |

|

|

|

Figure 4. AD28msp01 Initialization and ADSP-2101 Loopback Routine

Serial Data Output

When the digital power-down bit (PWDD) of Control Register 1 is set to 1, the AD28msp01’s SPORT begins transmitting data to the host processor. All transfers between the host processor and the AD28msp01 consist of a serial data output frame sync (SDOFS) followed by a 16-bit address word, then a second frame sync followed by a 16-bit data word. Address/data word pairs are transmitted whenever they become available. The ADC takes precedence over the Interpolator output data. If a new word becomes available while a serial transfer is in progress, the current serial transfer is completed before the new word starts transmission.

Serial Data Input

The host processor must initiate data transfers to the AD28msp01 by asserting the serial data input frame sync (SDIFS) high. Each of the 16-bit address word and 16-bit data word transfers begins one serial clock cycle after SDIFS is asserted. The address word always precedes the data word. The second serial data input frame sync for the data word can be asserted as early as the last bit of the address word is transmitted, or any time after.

The host processor must assert SDIFS shortly after the rising edge of SCLK and must maintain SDIFS high for one cycle because SDIFS is clocked by the SCLK falling edge. Data is then driven from the host processor shortly after the rising edge of the next SCLK and is clocked into the AD28msp01 on the falling edge of SCLK in that cycle. Each bit of a 16-bit address and 16-bit data word is thus clocked into the AD28msp01 on the falling edge of SCLK (MSB first).

and receive timing as well as an additional clock signal for serial port timing.

The receive clocks are the RCONV, RBIT and RBAUD signals. The individual clock rates are programmable and are all synchronized with RCONV.

The transmit clocks are the TCONV, TBIT and TBAUD signals. The individual clock rates are programmable and are all synchronized with TCONV.

Depending on the operating mode, the converter clocks can be synchronized to an external clock signal (TSYNC) or can be generated internally. The clocks can be adjusted in phase by setting the appropriate phase adjust register. All the AD28msp01 Bit/Baud clocks have a 50% duty cycle except the 1600 Hz baud rate. This baud rate has a 33%–66% duty cycle.

Resampling Interpolation Filter

The resampling interpolation filter interpolates the data from the TCONV rate to 1.7280 MHz. The data is then resampled (decimated) in phase with the RCONV clock. The frequency response characteristics of the resampling interpolation filter are identical to the frequency response characteristics of the antiimaging, low-pass filter/interpolation filter combination.

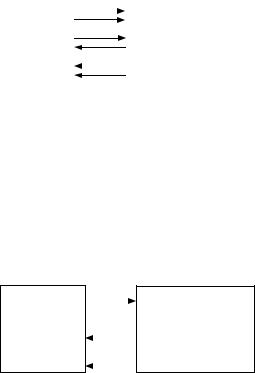

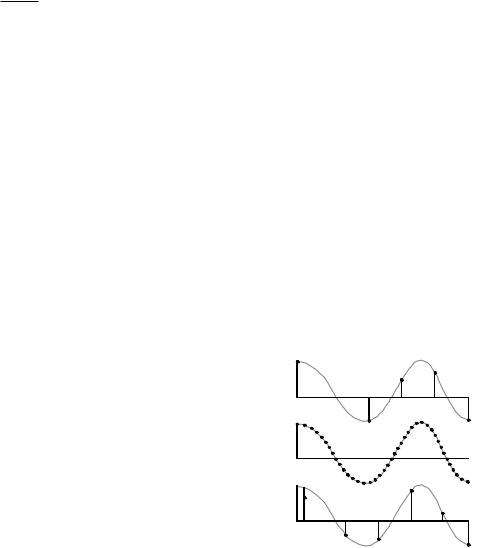

Figure 5 illustrates the effects of a resampling interpolation filter.

ANALOG SIGNAL

SAMPLED AT 9600 Hz

If SDIFS is asserted high again before the end of the present data word transfer, it is not recognized until the falling edge of SCLK in the last (LSB) cycle.

When the serial port receives an interpolator or DAC input word, it writes the value to an internal register which is read by the AD28msp01 when it is needed. This allows the host to send data words at any time during the sample period.

NOTE: Exact SPORT timing requirements are defined in the “Specifications” section of this data sheet.

Clock Generation

The AD28msp01 generates all transmit and receive clocks necessary to implement standard voice-grade modems. The AD28msp01 can generate six different clock signals for transmit

OUTPUT OF

INTERPOLATION

FILTER

OUTPUT OF

RESAMPLING

FILTER

Figure 5. Effects of Interpolation Filter

–6– |

REV. A |

AD28msp01

Since the resample phase is locked to RCONV, it can be advanced or slipped by writing a signed-magnitude value to the Receive Phase Adjust Register (Control Register 2). The phase advance or slip is equal to the master clock period (13.824 MHz) multiplied by the signed-magnitude 9-bit value in Control Register 4.

The change in phase requires a maximum of two RCONV cycles to complete. If the value written to Control Register 4 is less than the oversampling ratio, then the change will complete in one RCONV cycle.

Control Registers

The AD28msp01’s six control registers configure the device for various operating modes including filter bypass and powerdown. The AD28msp01’s host processor can read and write to

the control register through the AD28msp01’s serial port (SPORT).

The control registers should be set up for the desired mode of operation before bringing the AD28msp01 out of power-down (by writing ones to the PWDA and PWDD bits in Control Register 1).

The control registers are cleared (set to 0x0000) when the AD28msp01 is reset.

The sampling rate should be set before writing ones to the power-down bits. Changing the sampling rate at any other time will force a soft reset. For more information about soft resets, refer to the end of this section of the data sheet.

NOTE: Reserved bits should always be cleared to 0.

Control Register 0 |

address = 0x00 |

This register is used to:

•Enable/disable the resampling interpolation filter

•Set the external TSYNC clock rate

•Select the sampling rate

•Select the operating mode

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INTEN

Interpolation filter enable |

|

|

|

|

|

|

OP2-0 |

|

|

1 = enabled; 0 = disabled |

TS3-0 |

|

|

|

|

|

Operating Modes |

||

|

TSYNC Rate (Hz) |

|

|

|

000 |

= |

Asynchronous fallback mode |

||

|

0000 |

= |

9600 |

|

|

|

001 |

= |

Reserved |

|

0001 |

= |

8000 |

SR1-0 |

|

010 |

= |

Reserved |

|

|

0010 |

= |

7200 |

|

011 |

= |

Reserved |

||

|

Sampling Rate (kHz) |

||||||||

|

0011 |

= |

4800 |

100 |

= |

V.32 TSYNC |

|||

|

00 |

= |

9.6 |

||||||

|

0100 |

= |

2400 |

101 |

= |

V.32 Internal Sync |

|||

|

01 |

= |

8.0 |

||||||

|

0101 |

= |

1200 |

110 |

= |

V.32 Loopback |

|||

|

10 |

= |

7.2 |

||||||

|

0110 |

= |

600 |

111 |

= |

Async. fallback mode TSYNC |

|||

|

11 |

= |

Reserved |

||||||

|

0111 |

= |

19200 |

|

|

|

|||

|

|

|

|

|

|

|

|||

|

1000 |

= |

14400 |

|

|

|

|

|

|

|

1001 |

= |

12000 |

|

|

|

|

|

|

Control Register 1 address = 0x01

This register is used to:

•Increase the sampling rate to 8/7 the rate selected in Control Register 0

•Power down the device

•Bypass the digital filters

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

FB2 |

FB1 |

FB0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SA87

When set to a 1, this bit increases the

sampling rate to 8/7 of the programmed |

|

|

rate: |

PWDA |

|

(8/7) 9.6 kHz = 10.97 kHz, |

Power Down Analog |

|

(8/7) 8.0 kHz = 9.14 kHz, |

1 |

= Standard Operation |

(8/7) 7.2 kHz = 8.23 kHz |

0 |

= Low Power |

PWDD

Power Down Digital

1 = Standard Operation

0 = Low Power

FB2-0

FB2-0

Filter Bypass

Configuration |

|

|

||

FB2 |

FB1 |

FB0 |

|

|

0 |

0 |

0 |

= |

No filter bypass (default) |

0 |

0 |

1 |

= |

Reserved |

0 |

1 |

0 |

= |

ADC Hi pass filter bypassed |

0 |

1 |

1 |

= |

ADC Hi and Lo pass filter bypassed |

1 |

0 |

0 |

= |

DAC filter bypassed |

1 |

0 |

1 |

= |

Reserved |

1 |

1 |

0 |

= |

DAC and ADC Hi pass filters bypassed |

1 |

1 |

1 |

= |

DAC, ADC Hi and ADC Lo pass filtersbypassed |

REV. A |

–7– |

AD28msp01

If any low-pass filter is bypassed, the resampling interpolation filter should be disabled (in Control Register 0.)

Control Register 2 |

address = 0x02 |

This register is used to:

•Select the frequency of the Receive baud clock (RBAUD)

•Select the frequency of the Receive bit clock (RBIT)

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BA2-0 |

|

BI3-0 |

|

|

|

|

Receive baud rate clock selection |

Receive bit rate clock selection |

|||||

000 |

= |

2400 (default) |

0000 |

= |

9600 |

(default) |

001 |

= |

1600 |

0001 |

= |

8000 |

|

010 |

= |

1200 |

0010 |

= |

7200 |

|

011 |

= |

600 |

0011 |

= |

4800 |

|

100 |

= |

Reserved |

0100 |

= |

2400 |

|

101 |

= |

Reserved |

0101 |

= |

1200 |

|

110 |

= |

Reserved |

0110 |

= |

600 |

|

111 |

= |

Reserved |

0111 |

= |

19200 |

|

|

|

|

1000 |

= |

14400 |

|

|

|

|

1001 |

= |

12000 |

|

|

|

|

1010 |

= |

19200 with SA87 in |

|

|

|

|

|

|

control register 1 set |

|

|

|

|

|

|

(not scaled by 8/7) |

|

Control Register 3 |

address = 0x03 |

This register is used to:

•Select the frequency of the Transmit baud clock (TBAUD)

•Select the frequency of the Transmit bit clock (TBIT)

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BA2-0 |

|

BI3-0 |

|

|

|

|

Transmit baud rate clock |

Transmit bit rate clock selection |

|||||

selection |

|

0000 |

= |

9600 |

(default) |

|

000 |

= |

2400 (default) |

0001 |

= |

8000 |

|

001 |

= |

1600 |

0010 |

= |

7200 |

|

010 |

= |

1200 |

0011 |

= |

4800 |

|

011 |

= |

600 |

0100 |

= |

2400 |

|

100 |

= |

Reserved |

0101 |

= |

1200 |

|

101 |

= |

Reserved |

0110 |

= |

600 |

|

110 |

= |

Reserved |

0111 |

= |

19200 |

|

111 |

= |

Reserved |

1000 |

= |

14400 |

|

|

|

|

1001 |

= |

12000 |

|

|

|

|

1010 |

= |

19200 with SA87 in |

|

|

|

|

|

|

control register 1 set |

|

|

|

|

|

|

(not scaled by 8/7) |

|

–8– |

REV. A |

AD28msp01

Control Register 4 |

address = 0x04 |

This register is the Receive Phase Adjust Register and it is used to:

• Change the phase of the receive clocks (RBAUD, RBIT, RCONV)

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 – Phase advance

1 – Phase retard

P7-0

Phase Shift Magnitude

The amount of time slipped or advanced is defined as this number represented by P7-P0 times the master clock period.

Once you have written a value to the register, subsequent writes are ignored until the register is finished incrementing/decrementing to zero.

The phase advance or slip is equal to the master clock period (13.824 MHz) multiplied by the signed-magnitude 9-bit value in Control Register 4. The AD28msp01 decrements Control Register 4 as it adjusts the phase of RCONV. Control Register 4 will equal zero when the phase shift is complete.

Control Register 5 |

address = 0x05 |

This register is the Transmit Phase Adjust Register and it is used to:

• Change the phase of the Transmit clocks (TBAUD, TBIT, TCONV)

15 |

14 |

13 |

12 |

|

11 |

10 |

9 |

8 |

7 |

6 |

5 |

|

4 |

3 |

2 |

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

– Phase advance |

|

|

|

|

|

|

P7-0 |

|

|

|

|

|

|

||||

1 |

– Phase retard |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

Phase Shift Magnitude |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

The amount of time slipped or advanced is defined as this number represented by P7-P0 times the master clock period.

This register must be equal to zero before its value can be changed. Once you have written a value to the register, subsequent writes are ignored until the register is finished incrementing/ decrementing to zero.

The phase advance or slip is equal to the master clock period (13.824 MHz) multiplied by the signed-magnitude 9-bit value in Control Register 5. The AD28msp01 decrements Control Register 5 as it adjusts the phase of TCONV. Control Register 5 will equal zero when the phase shift is complete.

Soft Resets

Certain conditions cause the AD28msp01 to perform a soft reset; the DSP is reset but the control register values do not change.

Table I shows when a soft reset is caused by changing the values of certain control register bits while the device is operating. When these bits are modified, the AD28msp01 will perform a soft reset and start up again in the new configuration. Reserved bits in the control registers should always be set to zero.

Table I. Soft Reset

Bits |

Configures |

|

|

Control Register 0, SR1–SR0 |

Sampling rate |

Control Register 0, OP2–OP0 |

Clock generation operating modes |

|

(async-to-V.32 or V.32-to-async) |

Control Register 0, TS3–TS0 |

TSYNC rate |

Control Register 1, FB2–FB0 |

Filter bypass configuration |

Control Register 1, SA87 |

Sampling rate scaling by 8/7 |

|

|

Data Registers

The AD28msp01 contains four data registers.

Data Register 0 address = 0x06

DAC Input Register (write-only): The 16-bit twos complement values written to this register are input to the AD28msp01’s digital-to-analog converter.

REV. A |

–9– |

Loading...

Loading...