Texas Instruments TCM129C18N, TCM29C19N, TCM29C18N, TCM29C19DW, TCM29C18DW Datasheet

TCM29C18, TCM29C19, TCM129C18, TCM129C19

ANALOG INTERFACE FOR DSP

SCTS021D ±AUGUST 1987 ±REVISED OCTOBER 1996

D Reliable Silicon-Gate CMOS Technology |

|

DW OR N PACKAGE |

|||||||||

D |

Low Power Consumption |

|

|

|

(TOP VIEW) |

|

|

||||

|

± Operating Mode . . . 80 mW |

|

|

VBB |

|

1 |

16 |

|

VCC |

||

|

|

|

|

|

|||||||

|

± Power-Down Mode . . . 5 mW |

|

|

|

|

||||||

|

|

PWRO + |

|

2 |

15 |

|

GSX |

||||

|

|

|

|

||||||||

D |

μ-Law Coding |

|

|

|

|||||||

|

PWRO ± |

|

3 |

14 |

|

ANLG IN |

|||||

|

|

|

|||||||||

D Excellent Power-Supply Rejection Ratio |

|

PDN |

|

|

4 |

13 |

|

ANLG GND |

|||

|

|

|

|

||||||||

DCLKR |

|

5 |

12 |

|

|

|

|||||

|

Over Frequency Range of 0 Hz to 50 kHz |

|

|

TSX/DCLKX |

|||||||

|

PCM IN |

|

6 |

11 |

|

PCM OUT |

|||||

D No External Components Needed for |

|

|

|

||||||||

|

FSR/TSRE |

|

7 |

10 |

|

FSX/TSXE |

|||||

|

|

|

|||||||||

|

Sample, Hold, and Autozero Functions |

|

DGTL GND |

|

8 |

9 |

|

CLK |

|||

|

|

|

|

||||||||

D Precision Internal Voltage Reference |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

D Single Chip Contains A/D, D/A, and |

|

|

|

|

|

|

|

|

|

|

|

|

Associated Filters |

|

|

FEATURES TABLE |

|||||||

description |

|

Number of Pins: |

|

|

|

|

|

||||

|

16 |

|

|

|

|

|

|

|

|

||

|

The TCM29C18, TCM29C19, TCM129C18, and |

Coding Law: |

|

|

|

|

|

||||

|

μ-Law |

|

|

|

|

|

|||||

|

TCM129C19 are low-cost single-chip |

PCM |

|

|

|

|

|

||||

|

Variable Mode: |

|

|

|

|

|

|||||

|

codecs (pulse-code-modulated encoders |

and |

|

|

|

|

|

||||

|

64 kHz to 2.048 MHz |

|

|

||||||||

|

decoders) and PCM line filters. These devices |

|

|

||||||||

|

Fixed Mode: |

|

|

|

|

|

|||||

|

incorporate both the A/D and D/A functions, an |

|

|

|

|

|

|||||

|

2.048 MHz (TCM29C18, TCM129C18), |

||||||||||

|

antialiasing filter (A/D), and a smoothing filter |

1.536 MHz (TCM29C19, TCM129C19) |

|||||||||

|

(D/A). They are ideal for use with the TMS320 |

8-Bit Resolution |

|

|

|

|

|||||

|

DSP family members, particularly those featuring |

12-Bit Dynamic Range |

|

|

|||||||

|

a serial port such as the TMS32020, TMS32011, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

and TMS320C25. |

|

|

|

|

|

|

|

|

|

|

Primary applications include:

•Digital encryption systems

•Digital voice-band data storage systems

•Digital signal processing

These devices are designed to perform encoding of analog input signals (A/D conversion) and decoding of digital PCM signals (D/A conversion). They are useful for implementation in the analog interface of a digital signal processing system. Both devices also provide band-pass filtering of the analog signals prior to encoding, and smoothing after decoding.

The TCM29C18 and TCM29C19 are characterized for operation over the temperature range of 0°C to 70°C. The TCM129C18 and TCM129C19 are characterized for operation over the temperature range of ±40°C to 85°C.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1996, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TCM29C18, TCM29C19, TCM129C18, TCM129C19

ANALOG INTERFACE FOR DSP

SCTS021D ±AUGUST 1987 ±REVISED OCTOBER 1996

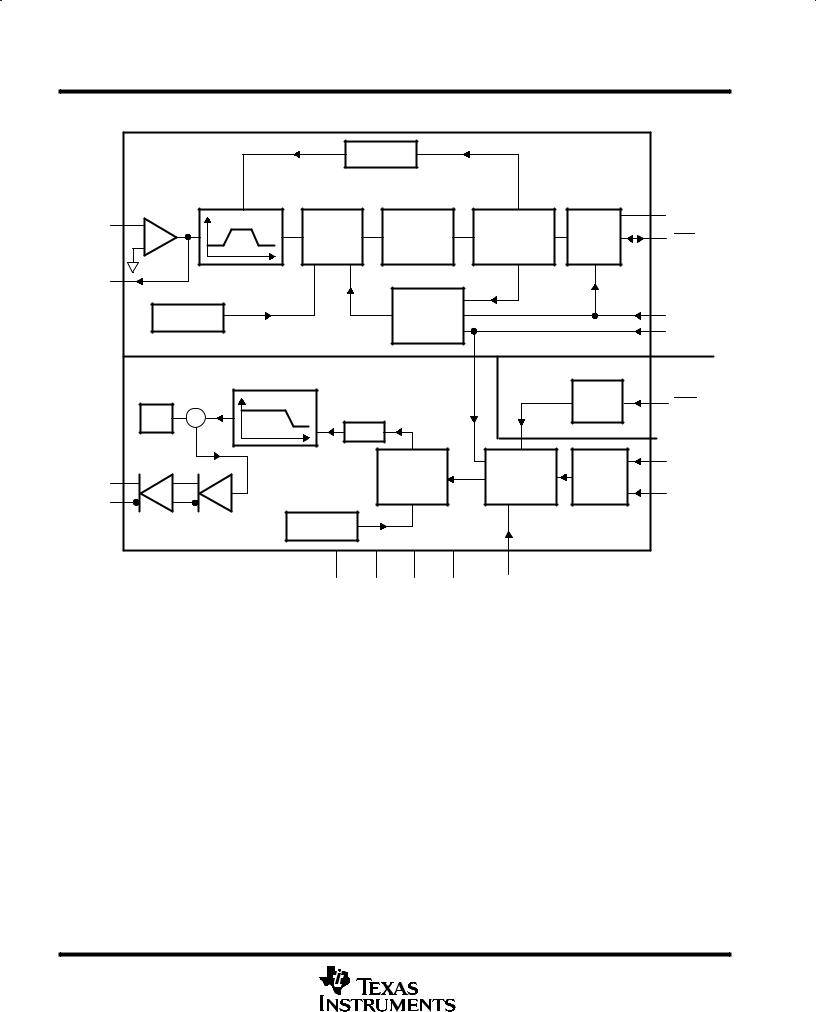

functional block diagram

|

|

Transmit Section |

Autozero |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

11 |

|

14 |

|

|

|

|

|

|

|

|

11 |

ANLG IN |

|

Filter |

Sample |

|

|

|

|

|

PCM OUT |

|

|

|

|

|

|

Successive |

Output |

|

|||

|

|

|

|

|

|

12 |

||||

|

|

|

|

and Hold |

Comparator |

|||||

|

|

|

|

Approximation |

Register |

TSX/ |

||||

|

|

|

|

and DAC |

|

|

|

|||

|

|

|

|

|

|

|

|

|

DCLKX |

|

GSX15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Analog- |

|

|

|

|

|

|

Reference |

|

|

to-Digital |

|

|

10 FSX/TSXE |

||

|

|

|

|

|

|

Control |

|

|

9 CLK |

|

|

|

|

|

|

|

Logic |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Receive Section |

|

|

|

|

Control Section |

|

||

|

|

|

|

Filter |

|

|

|

|

Control |

4 |

|

|

Gain |

|

|

|

|

|

Logic |

PDN |

|

|

|

Σ |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

Set |

|

|

|

|

|

|

|

|

|

|

|

Buffer |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Sample |

|

Digital- |

|

6 |

|

|

|

|

|

|

|

to-Analog |

Input |

PCM IN |

|

PWRO+ |

2 |

|

|

|

|

and Hold |

|

|

||

+ |

|

|

|

|

Control |

Register |

5 |

|||

|

|

|

|

and DAC |

|

|||||

PWRO± |

3 |

± |

|

|

|

|

Logic |

|

DCLKR |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Reference |

|

|

|

|

|

|

|

|

|

|

16 |

1 |

8 |

13 |

7 |

|

|

|

|

|

|

VCC |

VBB |

DGTL |

ANLG |

FSR/TSRE |

|

|

|

|

|

|

|

|

GND |

GND |

|

|

|

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

|

|

|

|

|

|

TCM29C18, TCM29C19, TCM129C18, TCM129C19 |

|

|

|

|

|

|

|

ANALOG INTERFACE FOR DSP |

|

|

|

|

|

|

|

SCTS021D ±AUGUST 1987 ±REVISED OCTOBER 1996 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Terminal Functions |

|

|

|

|

|

|

|

|

|

|

TERMINAL |

I/O |

DESCRIPTION |

|

|||

|

NAME |

NO. |

|

||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

ANLG IN |

14 |

I |

Inverting analog input to uncommitted transmit operational amplifier. |

|

||

|

|

|

|

|

|

|

|

|

ANLG GND |

13 |

|

Analog ground return for all voice circuits. ANLG GND is internally connected to DGTL GND. |

|

||

|

|

|

|

|

|

|

|

|

CLK |

9 |

I |

Master clock and data clock input for the fixed-data-rate mode. Master (filter) clock only for variable-data-rate |

|

||

|

|

|

|

|

|

mode. CLK is used for both the transmit and receive sections. |

|

|

|

|

|

|

|

|

|

|

DCLKR |

5 |

I |

Fixed-data-rate mode Ð variable-data-rate mode select. When DCLKR is connected to V BB, the device operates |

|

||

|

|

|

|

|

|

in the fixed-data-rate mode. When DCLKR is not connected to VBB, the device operates in the variable-data-rate |

|

|

|

|

|

|

|

mode and DCLKR becomes the receive data clock, which operates at frequencies from 64 kHz to 2.048 MHz. |

|

|

|

|

|

|

|

|

|

|

DGTL GND |

8 |

|

Digital ground for all internal logic circuits. DGTL GND is internally connected to ANLG GND. |

|

||

|

|

|

|

|

|

|

|

|

FSR/TSRE |

7 |

I |

Frame-synchronization clock input /time-slot enable for the receive channel. In the variable-data-rate mode, this |

|

||

|

|

|

|

|

|

signal must remain high for the duration of the time slot. The receive channel enters the standby state when FSR |

|

|

|

|

|

|

|

is TTL low for 30 ms. |

|

|

|

|

|

|

|

|

|

|

FSX/TSXE |

10 |

I |

Frame-synchronization clock input /time-slot enable for transmit channel. FSX/TSXE operates independently of, |

|

||

|

|

|

|

|

|

but in an analogous manner to FSR/TSRE. The transmit channel enters the standby state when FSX is low for 300 |

|

|

|

|

|

|

|

ms. |

|

|

|

|

|

|

|

|

|

|

GSX |

15 |

O |

Output terminal of internal uncommitted operational amplifier. Internally, this is the voice signal input to the transmit |

|

||

|

|

|

|

|

|

filter. |

|

|

|

|

|

|

|

|

|

|

PCM IN |

6 |

I |

Receive PCM input. PCM data is clocked in on eight consecutive negative transitions of the receive data clock, |

|

||

|

|

|

|

|

|

which is CLKR in fixed-data-rate timing and DCLKR in variable-data-rate timing. |

|

|

|

|

|

|

|

|

|

|

PCM OUT |

11 |

O |

Transmit PCM output. PCM data is clocked out of pcm out on eight consecutive positive transition of the transmit |

|

||

|

|

|

|

|

|

data clock, which is CLKX in fixed-data-rate timing and DCLKX in variable-data-rate timing. |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

I |

Power-down select. On the TCM29C18 and the TCM129C18, the device is inactive with a TTL low-level input and |

|

|

PDN |

|

|

||||

|

|

|

|

|

|

active with a TTL high-level input to the terminal. On the TCM29C19 and the TCM129C19, this terminal must be |

|

|

|

|

|

|

|

connected to a TTL high level. |

|

|

|

|

|

|

|

|

|

|

PWRO + |

2 |

O |

Noninverting output of power amplifier. PWRO+ can drive transformer hybrids or high-impedance loads directly |

|

||

|

|

|

|

|

|

in either a differential or single-ended configuration. |

|

|

|

|

|

|

|

|

|

|

PWRO ± |

3 |

O |

Inverting output of power amplifier. PWRO± is functionally identical to PWRO +. |

|

||

|

|

|

|

|

|

||

|

|

|

|

12 |

I/O |

Transmit channel time-slot strobe (output) or data clock (input). In the fixed-data-rate mode, this is an open-drain |

|

|

TSX/DCLKX |

|

|||||

|

|

|

|

|

|

output to be used as an enable signal for a 3-state buffer. In the variable-data-rate mode, DCLKX becomes the |

|

|

|

|

|

|

|

transmit data clock, which operates at TTL levels from 64 kHz to 2.048 MHz. |

|

|

|

|

|

|

|

||

|

VBB |

1 |

|

Negative supply voltage. Input is ± 5 V ± 5%. |

|

||

|

VCC |

16 |

|

Positive supply voltage. Input is 5 V ± 5%. |

|

||

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

TCM29C18, TCM29C19, TCM129C18, TCM129C19

ANALOG INTERFACE FOR DSP

SCTS021D ±AUGUST 1987 ±REVISED OCTOBER 1996

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage range, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. ±0.3 V to 15 V |

Output voltage range, VO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. ±0.3 V to 15 V |

Input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. ±0.3 V to 15 V |

Digital ground voltage range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±0.3 V to 15 V |

Operating free-air temperature range, TA: TCM29C18, TCM29C19 . . . . . . . . . . . . . . . . . . . . . |

. . 0°C to 70°C |

TCM129C18, TCM129C19 . . . . . . . . . . . . . . . . . . |

±40°C to 85°C |

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

± 65°C to 150°C |

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: DW or N package . . . . . . . . |

. . . . . . . 260°C |

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Voltage values for maximum ratings are with respect to VBB.

recommended operating conditions (see Note 2)

|

|

|

MIN |

NOM |

MAX |

UNIT |

|

|

|

|

|

|

|

VCC |

Supply voltage (see Note 3) |

4.75 |

5 |

5.25 |

V |

|

VBB |

Supply voltage |

± 4.75 |

± 5 |

± 5.25 |

V |

|

|

DGTL GND voltage with respect to ANLG GND |

|

0 |

|

V |

|

|

|

|

|

|

|

|

VIH |

High-level input voltage, all inputs except ANLG IN |

2.2 |

|

|

V |

|

VIL |

Low-level input voltage, all inputs except ANLG IN |

|

|

0.8 |

V |

|

VI(PP) |

Peak-to-peak analog input voltage (see Note 4) |

|

|

4.2 |

V |

|

RL |

Load resistance |

GSX |

10 |

|

|

kΩ |

|

|

|

|

|

||

PWRO + and/or PWRO ± |

300 |

|

|

Ω |

||

|

|

|

|

|||

|

|

|

|

|

|

|

CL |

Load capacitance |

GSX |

|

|

50 |

pF |

|

|

|

|

|||

PWRO + and/or PWRO ± |

|

|

100 |

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

TA |

Operating free-air temperature |

TCM29C18 or TCM29C19 |

0 |

|

70 |

°C |

|

|

|

|

|||

TCM129C18 or TCM129C19 |

± 40 |

|

85 |

|||

|

|

|

|

|||

NOTES: 2. To avoid possible damage to these CMOS devices and resulting reliability problems, the power-up procedure described in the device power-up sequence paragraphs later in this document should be followed.

3.Voltages at analog inputs and outputs and VCC and VBB terminals are with respect to ANLG GND. All other voltages are referenced to DGTL GND unless otherwise noted.

4.Analog inputs signals that exceed 4.2 V peak to peak may contribute to clipping and preclude correct A/D conversion. The digital code representing values higher than 4.2 V is 10 000000. For values more negative than 4.2 V, the code is 0000000.

electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

supply current, fDCLK = 2.048 MHz, outputs not loaded

|

PARAMETER |

|

|

|

TEST CONDITIONS |

TCM29Cxx |

TCM129Cxx |

UNIT |

|

|

|

|

|

|

|

|

|

|

|||

|

|

MIN |

MAX |

MIN MAX |

||||||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Operating |

|

|

|

|

10 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC |

Supply current from VCC |

Standby |

|

FSX or FSR at VIL after 300 ms |

|

1.2 |

1.5 |

mA |

|

|

|

|

Power down |

|

|

|

1 |

1.2 |

|

|

|

|

|

|

PDN |

at VIL after 10 μs |

|

|

|

|||

|

|

Operating |

|

|

|

|

± 10 |

± 14 |

|

|

IBB |

Supply current from VBB |

|

|

|

|

|

|

mA |

|

|

Standby |

|

FSX or FSR at VIL after 300 ms |

|

± 1.2 |

± 1.5 |

|

||||

|

|

Power down |

|

|

|

± 1 |

± 1.2 |

|

|

|

|

|

|

PDN |

at VIL after 10 μs |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TCM29C18, TCM29C19, TCM129C18, TCM129C19

ANALOG INTERFACE FOR DSP

SCTS021D ±AUGUST 1987 ±REVISED OCTOBER 1996

ground terminals

PARAMETER |

TEST CONDITIONS |

MIN TYP |

MAX |

UNIT |

|

|

|

|

|

DC resistance between ANLG GND and DGTL GND |

|

34 |

|

Ω |

|

|

|

|

|

digital interface

|

PARAMETER |

TEST CONDITIONS |

MIN TYP² |

MAX |

UNIT |

||

VOH |

High-level output voltage at PCM OUT |

IOH = ± 9.6 mA |

2.4 |

|

V |

||

IOH = ± 0.1 mA |

3.5 |

|

|||||

|

|

|

|

|

|

||

VOL |

Low-level output voltage at |

|

|

IOL = 3.2 mA |

|

0.5 |

V |

TSX |

|

|

|||||

IIH |

High-level input current, any digital input |

VI = 2.2 V to VCC |

|

12 |

μA |

||

IIL |

Low-level input current, any digital input |

VI = 0 to 0.8 V |

|

12 |

μA |

||

Ci |

Input capacitance |

|

5 |

10 |

pF |

||

Co |

Output capacitance |

|

5 |

|

pF |

||

² All typical values are at VBB = ± 5 V, VCC = 5 V, and TA = 25°C.

transmit side (A/D) characteristics

PARAMETER |

|

|

|

TEST CONDITIONS |

MIN TYP² |

MAX |

UNIT |

|||

Input offset voltage at ANLG IN |

VI = ± 2.17 V to 2.17 V |

|

|

|

± 25 |

mV |

||||

Input offset current at ANLG IN |

VI = ± 2.17 V to 2.17 V |

|

|

1 |

|

pA |

||||

Input bias current |

|

|

VI = ± 2.17 V to 2.17 V |

|

|

|

± 100 |

nA |

||

Open-loop voltage amplification at GSX |

|

|

|

|

|

5000 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Unity-gain bandwidth at GSX |

|

|

|

|

|

|

1 |

|

MHz |

|

|

|

|

|

|

|

|

|

|

|

|

Input resistance at ANLG IN |

|

|

|

|

|

|

10 |

|

MΩ |

|

|

|

|

|

|

|

|

|

|||

Gain-tracking error with sinusoidal input |

± 3 ≥ |

dBm0 input level ≥ |

± 40 dBm0, |

Ref level = ± 10 dBm0 |

|

± 0.5 |

dB |

|||

(see Notes 5, 6, and 7) |

|

|

± 40 > dBm0 input level ≥ ± 50 dBm0, |

Ref level = ± 10 dBm0 |

|

± 25 |

||||

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||

Transmit gain tolerance |

|

|

VI = 1.06 V, |

|

f = 1.02 kHz |

0.95 |

1.19 |

Vrms |

||

Noise |

|

|

Ref max output level: 200 Hz to 3 kHz |

|

|

± 70 |

dB |

|||

|

|

|

|

|

||||||

Supply-voltage rejection ratio, |

f = 0 Hz to 30-kHz (measured at PCM OUT) idle channel, |

± 20 |

|

dB |

||||||

VCC to VBB |

|

|

Supply signal = 200 mV peak to peak |

|

|

|||||

|

|

|

|

|

|

|||||

Crosstalk attenuation, transmit to |

ANLG IN = 0 dBm, |

|

f = 1-kHz, unity gain, |

62 |

|

dB |

||||

receive (single ended) |

|

|

PCM IN = lowest decode level, |

Measured at PWRO + |

|

|||||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|||

Signal-to-distortion ratio, sinusoidal |

0 dBm0 ≥ ANLG IN ≥ ± 30 dBm0 |

|

33 |

|

|

|||||

|

|

|

|

|

|

|

|

|||

± 30 dBm0 > ANLG IN ≥ |

± 40 dBm0 |

|

27 |

|

dB |

|||||

input (see Note 8) |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

± 40 dBm0 > ANLG IN ≥ |

± 45 dBm0 |

|

22 |

|

|

|||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

Absolute delay time to PCM OUT |

Fixed-data rate, |

|

fCLKX = 2.048 MHz, |

245 |

|

μs |

||||

Input to ANLG IN = 1 kHz at 0 dB |

|

|

||||||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

² All typical values are at V |

BB |

= ± 5 V, V |

|

= 5 V, and T = 25°C. |

|

|

|

|

|

|

|

CC |

|

A |

|

|

|

|

|

||

NOTES: 5. Unless otherwise noted, the analog input is a 0-dBm0, 1020-Hz sine wave, where 0 dBm0 is defined as the zero-reference point of the channel under test. This corresponds to an analog signal input of 1.064 Vrms or an output of 1.503 Vrms.

6.The input amplifier is set for unity gain. The digital input is a PCM bit stream generated by passing a 0-dBm0, 1020-Hz sine wave through an ideal encoder.

7.The TCM29C18, TCM29C19, TCM129C18, and TCM129C19 are internally connected to set PWRO + and PWRO ± to 0 dBM. All output levels are (sin x)/x corrected.

8.CCITT G.712 ± Method 2

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

5 |

TCM29C18, TCM29C19, TCM129C18, TCM129C19

ANALOG INTERFACE FOR DSP

SCTS021D ±AUGUST 1987 ±REVISED OCTOBER 1996

receive side (D/A) characteristics (see Note 9)

PARAMETER |

|

|

|

TEST CONDITIONS |

MIN TYP² |

MAX |

UNIT |

|||

Output offset voltage PWRO + and |

|

Relative to ANLG GND |

|

|

|

± 200 |

mV |

|||

PWRO ± (single ended) |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Output resistance at PWRO + and |

|

|

|

|

|

1 |

2 |

Ω |

||

PWRO ± |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Gain-tracking error with sinusoidal |

|

± 3 dBm0 ≥ |

input level ≥ |

± 40 dBm0, |

Ref level = ± 10 dBm0 |

|

± 0.5 |

dB |

||

input (see Notes 5, 6, and 7) |

|

|

± 40 dBm0 > input level ≥ ± 50 dBm0, |

Ref level = ± 10 dBm0 |

|

± 25 |

||||

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

Receive gain tolerance |

|

|

|

VI = 1.06 V, |

|

|

f = 1.02 kHz |

1.34 |

1.69 |

Vrms |

Noise |

|

|

|

Ref max output level: 200 Hz to 3 kHz |

|

|

± 70 |

dB |

||

|

|

|

|

|

|

|

|

|

|

|

Supply voltage rejection ratio, |

|

f = 0 Hz to 30-kHz, |

|

Idle channel, |

|

|

|

|||

|

Supply signal = 200 mV peak to peak, |

Narrow band, |

±20 |

|

dB |

|||||

VCC to VBB (single-ended) |

|

|

|

|||||||

|

|

Frequency at PWRO + |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

Crosstalk attenuation, receive to |

|

PCM IN = 0 dB, |

|

|

60 |

|

dB |

|||

transmit (single ended) |

|

|

|

Frequency = 1 kHz at PCM OUT |

|

|

||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

Signal-to-distortion ratio, sinusoidal |

|

0 dBm0 ≥ ANLG IN ≥ ± 30 dBm0 |

|

33 |

|

|

||||

|

|

|

|

|

|

|

|

|||

|

± 30 dBm0 > ANLG IN ≥ |

± 40 dBm0 |

|

27 |

|

dB |

||||

input (see Note 8) |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

± 40 dBm0 > ANLG IN ≥ |

± 45 dBm0 |

|

22 |

|

|

||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|||

Absolute delay time to PWRO + |

|

Fixed data rate, |

|

fCLKX = 2.048 MHz |

190 |

|

μs |

|||

² All typical values are at V |

BB |

= ± 5 V, V = 5 V, and T = 25°C. |

|

|

|

|

|

|||

|

|

CC |

A |

|

|

|

|

|

||

NOTES: 5. Unless otherwise noted, the analog input is a 0-dBm0, 1020-Hz sine wave, where 0 dBm0 is defined as the zero-reference point of the channel under test. This corresponds to an analog signal input of 1.064 Vrms or an output of 1.503 Vrms.

6.The input amplifier is set for unity gain. The digital input is a PCM bit stream generated by passing a 0-dBm0, 1020-Hz sine wave through an ideal encoder.

7.The TCM29C18, TCM29C19, TCM129C18, and TCM129C19 are internally connected to set PWRO + and PWRO ± to 0 dBM. All output levels are (sin x)/x corrected.

8.CCITT G.712 ± Method 2

9.The receive side (D/A) characteristics are referenced to a 600-Ω termination.

timing requirements

clock timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figures 3 and 4)

|

|

MIN |

NOM |

MAX |

UNIT |

|

|

|

|

|

|

tc(CLK) |

Clock period for CLK (2.048-MHz systems) |

488 |

|

|

ns |

tr, tf |

Rise and fall times for CLK |

5 |

|

30 |

ns |

tw(CLK) |

Pulse duration for CLK |

220 |

|

|

ns |

tw(DCLK) |

Pulse duration, DCLK (fDCLK = 64 kHz to 2.048 MHz) |

220 |

|

|

ns |

|

Clock duty cycle, [tw(CLK)/tc(CLK)] for CLK |

45% |

50% |

55% |

|

transmit timing requirements over recommended ranges of supply voltage and operating free-air temperature, fixed-data-rate mode (see Figure 3)

|

|

MIN |

MAX |

UNIT |

|

|

|

|

|

td(FSX) |

Frame-sync delay time |

100 |

tc(CLK) ± 100 |

ns |

receive timing requirements over recommended ranges of supply voltages and operating free-air temperature, fixed-data-rate mode (see Figure 4)

|

|

MIN |

MAX |

UNIT |

|

|

|

|

|

|

|

td(FSR) |

Frame-sync delay time |

100 |

tc(CLK)±100 |

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...