White Electronic Designs WMS512K8L-55DJI, WMS512K8L-55DJCA, WMS512K8L-55DJC, WMS512K8L-55DEMA, WMS512K8L-55DEM Datasheet

...

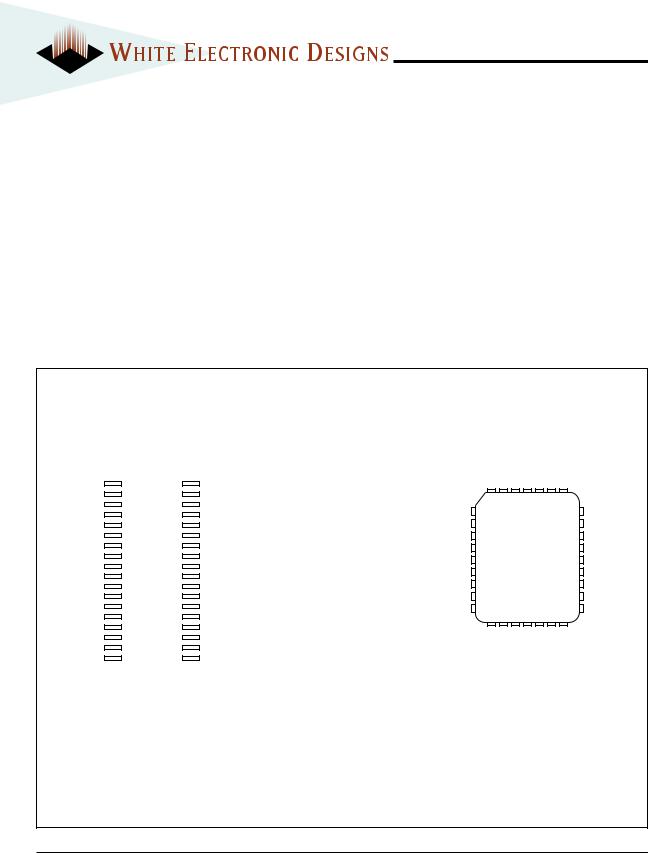

WMS512K8-XXX

HI-RELIABILITY PRODUCT

512Kx8 MONOLITHIC SRAM, SMD 5962-95613

FEATURES

■Access Times 15, 17, 20, 25, 35, 45, 55ns

■MIL-STD-883 Compliant Devices Available

■Revolutionary, Center Power/Ground Pinout JEDEC Approved

•36 lead Ceramic SOJ (Package 100)

•36 lead Ceramic Flat Pack (Package 226)

■Evolutionary, Corner Power/Ground Pinout JEDEC Approved

•32 pin Ceramic DIP (Package 300)

•32 lead Ceramic SOJ (Package 101)

•32 lead Ceramic Flat Pack (Package 220)

•32 lead Ceramic Flat Pack (Package 142)

■32 pin, Rectangular Ceramic Leadless Chip Carrier (Package 601)

■Commercial, Industrial and Military Temperature Range

■5 Volt Power Supply

■Low Power CMOS

■Low Power Data Retention for Battery Back-up Operation

■TTL Compatible Inputs and Outputs

REVOLUTIONARY PINOUT |

EVOLUTIONARY PINOUT |

|

|||||||||||||||||||

|

|

|

|

36 FLAT PACK |

|

|

|

|

|

|

32 DIP |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

32 CSOJ (DE) |

|

||||||||||

|

|

|

|

36 CSOJ |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

32 FLAT PACK (FE)* |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

32 FLAT PACK (FD) |

|

|||||||

|

|

|

|

TOP VIEW |

|

|

|

|

|

|

TOP VIEW |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 |

1 |

36 |

|

NC |

A18 |

|

|

1 |

|

32 |

|

VCC |

|

||||||

|

|

A1 |

2 |

35 |

|

A18 |

A16 |

|

|

2 |

|

31 |

|

A15 |

|

||||||

|

|

|

|

|

|

|

|

||||||||||||||

|

|

A2 |

3 |

34 |

|

A17 |

A14 |

|

|

3 |

|

30 |

|

A17 |

A7 |

||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

A3 |

4 |

33 |

|

A16 |

A12 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

4 |

|

29 |

|

WE |

A6 |

|||||||||||

|

|

A4 |

5 |

32 |

|

A15 |

A7 |

|

|

5 |

|

28 |

|

A13 |

|||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

6 |

31 |

|

|

|

|

|

|

|

|

|

|||||||

|

|

CS |

|

|

OE |

|

|

A6 |

|

|

6 |

|

27 |

|

A8 |

A5 |

|||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

I/O0 |

7 |

30 |

|

I/O7 |

A5 |

|

|

7 |

|

26 |

|

A9 |

A4 |

||||||||

I/O1 |

8 |

29 |

|

I/O6 |

A4 |

|

|

8 |

|

25 |

|

A11 |

A3 |

||||||||

VCC |

9 |

28 |

|

GND |

A3 |

|

|

|

|

|

|

|

|

|

|

|

|||||

GND |

10 |

27 |

|

VCC |

|

|

9 |

|

24 |

|

OE |

A2 |

|||||||||

|

|

|

|

|

|||||||||||||||||

I/O2 |

11 |

26 |

|

I/O5 |

A2 |

|

|

10 |

|

23 |

|

A10 |

A1 |

||||||||

|

A1 |

|

|

|

|

|

|

|

|

|

|

||||||||||

I/O3 |

12 |

25 |

|

I/O4 |

|

|

11 |

|

22 |

|

CS |

A0 |

|||||||||

|

A0 |

|

|

12 |

|

21 |

|

I/O7 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

WE |

13 |

24 |

|

A14 |

I/O0 |

||||||||||||||||

|

I/O0 |

|

|

13 |

|

20 |

|

I/O6 |

|||||||||||||

|

|

A5 |

14 |

23 |

|

A13 |

|

|

|

|

|

||||||||||

|

|

|

I/O1 |

|

|

14 |

|

19 |

|

I/O5 |

|

||||||||||

|

|

A6 |

15 |

22 |

|

A12 |

|

|

|

|

|

||||||||||

|

|

|

I/O2 |

|

15 |

|

18 |

|

I/O4 |

|

|||||||||||

|

|

A7 |

16 |

21 |

|

A11 |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|||||||||||||||

|

|

A8 |

17 |

20 |

|

A10 |

GND |

|

16 |

|

17 |

|

I/O3 |

|

|||||||

|

|

A9 |

18 |

19 |

|

NC |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

PIN DESCRIPTION |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0-18 |

|

|

Address Inputs |

|

|||||||

|

|

|

|

|

|

|

|

|

|

I/O0-7 |

|

|

Data Input/Output |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

Chip Select |

|

||||||

|

|

|

|

|

|

|

|

|

|

OE |

|

|

|

Output Enable |

|

||||||

|

|

|

|

|

|

|

|

|

|

WE |

|

|

|

Write Enable |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

+5.0V Power |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|

Ground |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

*Package not recommended for new designs, "FD" recommended for new designs.

32 CLCC

TOP VIEW

A12 |

A14 |

A16 |

A18 |

VCC A15 |

A17 |

|

|

|

|

|

4 |

3 |

2 |

1 |

32 31 30 |

|

|

|

|

|

|

5 |

|

|

|

|

29 |

|

|

|

|

|

|

|

|

|

WE |

||||||

6 |

|

|

|

|

28 |

A13 |

||||

7 |

|

|

|

|

27 |

A8 |

||||

8 |

|

|

|

|

26 |

A9 |

||||

9 |

|

|

|

|

25 |

A11 |

||||

10 |

|

|

|

|

24 |

|

||||

|

|

|

|

|

OE |

|

||||

11 |

|

|

|

|

23 |

A10 |

||||

12 |

|

|

|

|

22 |

|

|

|||

|

|

|

|

|

CS |

|

|

|||

13 |

|

|

|

|

21 |

I/O7 |

||||

14 15 16 17 18 19 20 |

|

|

|

|

|

|||||

I/O1 |

I/O2 |

VSS |

I/O3 |

I/O4 I/O5 |

I/O6 |

|

|

|

|

|

October 2000 Rev. 4 |

1 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

|

|

WMS512K8-XXX

ABSOLUTE MAXIMUM RATINGS |

TRUTH TABLE |

Parameter |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

Operating Temperature |

TA |

-55 |

+125 |

°C |

|

|

|

|

|

Storage Temperature |

TSTG |

-65 |

+150 |

°C |

|

|

|

|

|

Signal Voltage Relative to GND |

VG |

-0.5 |

Vcc+0.5 |

V |

|

|

|

|

|

Junction Temperature |

TJ |

|

150 |

°C |

Supply Voltage |

VCC |

-0.5 |

7.0 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

OE |

|

WE |

|

Mode |

Data I/O |

Power |

|||||

|

H |

|

X |

|

|

X |

|

Standby |

High Z |

Standby |

||

|

|

|

|

|

|

|

|

|

|

|

||

|

L |

|

L |

|

|

H |

|

Read |

Data Out |

Active |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

X |

|

|

L |

|

Write |

Data In |

Active |

||

|

L |

|

H |

|

|

H |

|

Out Disable |

High Z |

Active |

||

RECOMMENDED OPERATING CONDITIONS

Parameter |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

Supply Voltage |

VCC |

4.5 |

5.5 |

V |

|

|

|

|

|

Input High Voltage |

VIH |

2.2 |

VCC + 0.3 |

V |

|

|

|

|

|

Input Low Voltage |

VIL |

-0.3 |

+0.8 |

V |

|

|

|

|

|

Operating Temp. (Mil.) |

TA |

-55 |

+125 |

°C |

|

|

|

|

|

CAPACITANCE

(TA = +25°C)

Parameter |

Symbol |

Condition |

Package |

Speed (ns) |

Max |

Unit |

|

|

|

|

|

|

|

Input capacitance |

CIN |

VIN = 0V, f = 1.0MHz |

32 Pin CSOJ, DIP, |

15 to 55 |

20 |

pF |

|

|

|

Flat Pack Evolutionary |

|

|

|

|

|

|

32 Pin CLCC |

15 to 55 |

15 |

pF |

|

|

|

36 Pin CSOJ & Flat Pack |

15 to 35 |

12 |

pF |

|

|

|

Revolutionary |

|

|

|

|

|

|

45 to 55 |

20 |

pF |

|

|

|

|

|

|||

Output capicitance |

COUT |

VOUT = 0V, f = 1.0MHz |

32 Pin CSOJ, DIP, |

15 to 55 |

20 |

pF |

|

|

|

Flat Pack Evolutionary |

|

|

|

|

|

|

36 Pin CSOJ & Flat Pack |

15 to 35 |

12 |

pF |

|

|

|

Revolutionary |

45 to 55 |

20 |

pF |

|

|

|

|

|

|

|

This parameter is guaranteed by design but not tested.

DC CHARACTERISTICS

(VCC = 5.0V, GND = 0V, TA = -55°C to +125°C)

Parameter |

Sym |

|

|

|

|

Conditions |

Min |

Max |

Units |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Input Leakage Current |

ILI |

|

VCC = 5.5, VIN = GND to VCC |

|

10 |

A |

|||||||||

Output Leakage Current |

ILO |

|

|

|

|

= VIH, |

|

|

|

|

= VIH, VOUT = GND to VCC |

|

10 |

A |

|

|

CS |

OE |

|

||||||||||||

Operating Supply Current* |

ICC |

|

|

|

= VIL, |

|

|

|

= VIH, f = 5MHz, Vcc = 5.5 |

|

160 |

mA |

|||

|

CS |

OE |

|

||||||||||||

Standby Current |

ISB |

|

|

= VIH, |

|

= VIH, f = 5MHz, Vcc = 5.5 |

|

15 |

mA |

||||||

|

CS |

OE |

|

||||||||||||

Output Low Voltage |

VOL |

|

IOL = 8mA for 17 - 35ns, |

|

0.4 |

V |

|||||||||

|

|

|

IOL = 2.1mA for 45 - 55ns, VCC = 4.5 |

|

|

|

|||||||||

Output High Voltage |

VOH |

|

IOH = -4.0mA for 17 - 35ns, |

2.4 |

|

V |

|||||||||

|

|

|

IOH = -1.0mA for 45 - 55ns, VCC = 4.5 |

|

|

|

|||||||||

NOTE: DC test conditions: VIH = VCC -0.3V, VIL = 0.3V * Not 100% duty cycle

DATA RETENTION CHARACTERISTICS FOR LOW POWER “L” VERSION

Parameter |

Symbol |

|

Conditions |

|

|

Units |

|

|

|

|

|

|

Min |

Max |

|

Data Retention Supply Voltage |

VDR |

|

CS |

≥ VCC -0.2V |

2.0 |

5.5 |

V |

Low Power Data Retention |

ICCDR1 |

|

|

VCC = 3V |

|

7 |

mA |

Low Power Data Retention |

ICCDR2 |

|

|

VCC = 2V |

|

2 |

mA |

|

|

|

|

|

|

|

|

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

2 |

|

|

|

|||

WMS512K8-XXX

AC CHARACTERISTICS

(VCC = 5.0V, GND = 0V, TA = -55°C to +125°C)

Parameter |

Symbol |

|

-15 |

-17 |

|

-20 |

-25 |

|

-35 |

|

-45 |

-55 |

|

Units |

|||||||

Read Cycle |

|

Min |

|

Max |

Min |

Max |

Min Max |

Min Max |

Min |

|

Max |

Min |

|

Max |

Min |

Max |

|

||||

Read Cycle Time |

tRC |

15 |

|

|

17 |

|

|

20 |

|

25 |

|

35 |

|

|

45 |

|

|

55 |

|

|

ns |

Address Access Time |

tAA |

|

|

15 |

|

|

17 |

|

20 |

|

25 |

|

|

35 |

|

|

45 |

|

|

55 |

ns |

Output Hold from Address Change |

tOH |

0 |

|

|

0 |

|

|

0 |

|

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

ns |

Chip Select Access Time |

tACS |

|

|

15 |

|

|

17 |

|

20 |

|

25 |

|

|

35 |

|

|

45 |

|

|

55 |

ns |

Output Enable to Output Valid |

tOE |

|

|

8 |

|

|

9 |

|

10 |

|

12 |

|

|

25 |

|

|

25 |

|

|

25 |

ns |

Chip Select to Output in Low Z |

tCLZ1 |

2 |

|

|

2 |

|

|

2 |

|

2 |

|

4 |

|

|

4 |

|

|

4 |

|

|

ns |

Output Enable to Output in Low Z |

tOLZ1 |

0 |

|

|

0 |

|

|

0 |

|

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

ns |

Chip Disable to Output in High Z |

tCHZ1 |

|

|

8 |

|

|

9 |

|

10 |

|

12 |

|

|

15 |

|

|

20 |

|

|

20 |

ns |

Output Disable to Output in High Z |

tOHZ1 |

|

|

8 |

|

|

9 |

|

10 |

|

12 |

|

|

15 |

|

|

20 |

|

|

20 |

ns |

1. This parameter is guaranteed by design but not tested.

AC CHARACTERISTICS

(VCC = 5.0V, GND = 0V, TA = -55°C to +125°C)

Parameter |

Symbol |

-15 |

-17 |

-20 |

|

-25 |

|

-35 |

-45 |

|

-55 |

|

Units |

|||||||

Write Cycle |

|

Min Max |

Min Max |

Min Max |

Min |

|

Max |

Min |

|

Max |

Min |

Max |

Min |

Max |

|

|||||

Write Cycle Time |

tWC |

15 |

|

17 |

|

20 |

|

25 |

|

|

35 |

|

|

45 |

|

|

55 |

|

|

ns |

Chip Select to End of Write |

tCW |

13 |

|

14 |

|

14 |

|

15 |

|

|

25 |

|

|

35 |

|

|

50 |

|

|

ns |

Address Valid to End of Write |

tAW |

13 |

|

14 |

|

14 |

|

15 |

|

|

25 |

|

|

35 |

|

|

50 |

|

|

ns |

Data Valid to End of Write |

tDW |

8 |

|

9 |

|

10 |

|

10 |

|

|

20 |

|

|

25 |

|

|

25 |

|

|

ns |

Write Pulse Width |

tWP |

13 |

|

14 |

|

14 |

|

15 |

|

|

25 |

|

|

35 |

|

|

40 |

|

|

ns |

Address Setup Time |

tAS |

2 |

|

2 |

|

2 |

|

2 |

|

|

2 |

|

|

2 |

|

|

2 |

|

|

ns |

Address Hold Time |

tAH |

0 |

|

0 |

|

0 |

|

0 |

|

|

0 |

|

|

5 |

|

|

5 |

|

|

ns |

Output Active from End of Write |

tOW1 |

2 |

|

2 |

|

3 |

|

4 |

|

|

4 |

|

|

5 |

|

|

5 |

|

|

ns |

Write Enable to Output in High Z |

tWHZ1 |

|

8 |

|

9 |

|

9 |

|

|

10 |

|

|

15 |

|

|

20 |

|

|

25 |

ns |

Data Hold Time |

tDH |

0 |

|

0 |

|

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

|

ns |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1. This parameter is guaranteed by design but not tested.

AC TEST CIRCUIT

|

I OL |

|

Current Source |

D.U.T. |

VZ ≈1.5V |

Ceff = 50 pf |

(Bipolar Supply) |

|

IOH

Current Source

AC TEST CONDITIONS

Parameter |

Typ |

Unit |

Input Pulse Levels |

VIL = 0, VIH = 3.0 |

V |

|

|

|

Input Rise and Fall |

5 |

ns |

Input and Output Reference Level |

1.5 |

V |

|

|

|

Output Timing Reference Level |

1.5 |

V |

|

|

|

NOTES:

VZ is programmable from -2V to +7V. IOL & IOH programmable from 0 to 16mA. Tester Impedance Z0 = 75 Ω.

VZ is typically the midpoint of VOH and VOL.

IOL & IOH are adjusted to simulate a typical resistive load circuit. ATE tester includes jig capacitance.

3 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

Loading...

Loading...