White Electronic Designs WF8M32-150G4DM5, WF8M32-150G4DI5, WF8M32-150G4DC5, WF8M32-120G4DM5, WF8M32-120G4DI5 Datasheet

...

8Mx32 5V FLASH MODULE ADVANCED*

FEATURES

■Access Time of 100, 120, 150ns

■Packaging:

•68 Lead, 40 mm (1.560") square hermetic CQFP, 5.2 mm (0.205") high (Package 503)

■Sector Architecture

•32 equal size sectors of 64KBytes per each 2Mx8 chip

•Any combination of sectors can be erased. Also supports full chip erase.

■100,000 Write/Erase Cycles Minimum

■Organized as 8Mx32

■Commercial, Industrial, and Military Temperature Ranges

■5 Volt Read and Write. 5V ± 10% Supply.

■Low Power CMOS

WF8M32-XG4DX5

HI-RELIABILITY PRODUCT

■Data Polling and Toggle Bit feature for detection of program or erase cycle completion.

■Supports reading or programming data to a sector not being erased.

■RESET pin resets internal state machine to the read mode. (Not available in HIP package for WF2M32-XHX5)

■Built-in Decoupling Caps and Multiple Ground Pins for Low Noise Operation, Seperate Power and Ground Planes to improve noise immunity.

■Built in Buffering.

*This data sheet describes a product that may or may not be under development, and is subject to change or cancellation without notice.

Note: For programming information refer to Flash Programming 16M5 Application Note.

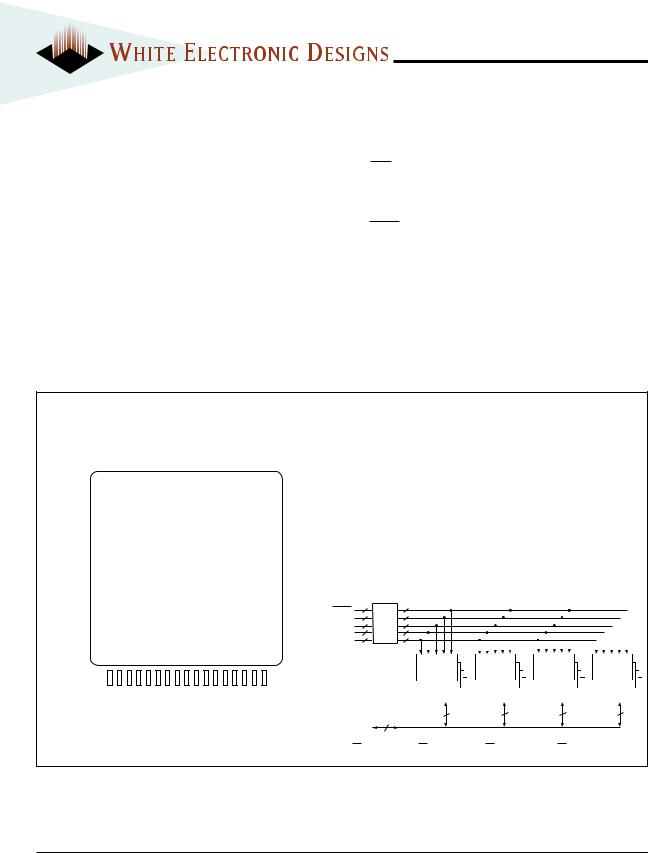

FIG. 1 PIN CONFIGURATION FOR WF8M32-XG4DX5

TOP VIEW |

PIN DESCRIPTION |

|

|

|

NC |

A0 |

A1 |

|

A2 |

|

A3 |

|

A4 |

|

A5 |

|

CS1 |

|

GND |

|

CS3 |

|

WE A6 A7 A8 A9 A10 |

VCC |

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

8 |

|

7 |

|

6 |

|

5 |

|

4 |

|

3 |

|

2 |

|

1 |

68 67 66 65 64 63 62 61 |

|

|

|

|

|

|

|

||||||||||||||||||||||||

I/O0 |

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

|

I/O16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O1 |

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

|

I/O17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O2 |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

|

I/O18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O3 |

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

|

I/O19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O4 |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

|

I/O20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O5 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

|

I/O21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O6 |

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

|

I/O22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O7 |

|

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

53 |

|

I/O23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

GND |

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O8 |

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

|

I/O24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O9 |

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

|

I/O25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

I/O10 |

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

|

I/O26 |

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

I/O11 |

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

I/O27 |

RESET |

4 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O12 |

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

I/O28 |

CS 1-4 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

I/O13 |

|

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

I/O29 |

|

|

WE |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

I/O14 |

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

I/O30 |

|

A0-22 |

23 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

I/O15 |

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

I/O31 |

|

|

|

|

|

|

|

|

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 |

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O0-31 |

|

Data Inputs/Outputs |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0-22 |

|

|

Address Inputs |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WE |

|

|

|

|

Write Enable |

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Selects |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

1-4 |

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Enable |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|

|

|

Power Supply |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reset |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

Ground |

|

|

|

|

|||||||||||

BLOCK DIAGRAM |

|

|

|

|

|

|

|

|

NC |

|

|

Not Connected |

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Interface |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

1 |

|

|

|

CS |

2 |

|

|

|

|

CS |

3 |

|

|

|

CS |

4 |

|||||||||||||||||

VCC |

A11 |

A12 |

A13 |

A14 |

A15 |

A16 |

|

CS2 |

OE |

|

CS4 |

A17 |

A18 |

A19 |

A20 |

A21 |

RESET |

A22 |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2M x 8 |

|

|

|

|

|

|

2M x 8 |

|

|

|

|

|

2M x 8 |

|

|

|

|

|

2M x 8 |

|

|

|||

|

|

|

2M x 8 |

|

|

|

|

|

2M x 8 |

|

|

|

|

|

|

2M x 8 |

|

|

|

|

2M x 8 |

|

|||||

|

|

|

2M x 8 |

|

|

|

|

2M x 8 |

|

|

|

|

2M x 8 |

|

|

|

|

2M x 8 |

|

||||||||

|

|

|

2M x 8 |

|

|

|

2M x 8 |

|

|

|

2M x 8 |

|

|

|

2M x 8 |

||||||||||||

|

|

|

I/O 0 - 7 |

I/O 8 - 1 5 |

I/O 1 6 - 2 3 |

I/O 2 4 - 3 1 |

|||||||||||||||||||||

|

|

|

8 |

|

|

|

|

|

|

8 |

|

|

|

|

|

|

8 |

|

|

|

|

|

|

8 |

|

|

|

32

I/O0-31

CS1 selects I/O0-7, CS2 selects I/O8-15, CS3 selects I/O16-23, CS4 selects I/O24-31

October 1999 Rev. 3 |

1 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

WF8M32-XG4DX5

ABSOLUTE MAXIMUM RATINGS

Parameter |

Symbol |

Ratings |

Unit |

Voltage on Any Pin Relative to VSS |

VT |

-2.0 to +7.0 |

V |

Power Dissipation |

PT |

8 |

W |

Storage Temperature |

Tstg |

-65 to +125 |

°C |

Short Circuit Output Current |

IOS |

100 |

mA |

Endurance - Write/Erase Cycles |

|

100,000 min |

cycles |

(Mil Temp) |

|

|

|

Data Retention (Mil Temp) |

|

20 |

years |

|

|

|

|

RECOMMENDED DC OPERATING CONDITIONS

Parameter |

Symbol |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

Supply Voltage |

VCC |

4.5 |

5.0 |

5.5 |

V |

Ground |

VSS |

0 |

0 |

0 |

V |

Input High Voltage |

VIH |

2.0 |

- |

VCC + 0.5 |

V |

Input Low Voltage |

VIL |

-0.5 |

- |

+0.8 |

V |

Operating Temperature (Mil.) |

TA |

-55 |

- |

+125 |

°C |

Operating Temperature (Ind.) |

TA |

-40 |

- |

+85 |

°C |

CAPACITANCE

(TA = +25°C)

|

|

Parameter |

Symbol |

Conditions |

Max |

Unit |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

capacitance |

COE |

VIN = 0 V, f = 1.0 MHz |

20 |

pF |

|

|

|

OE |

|

|||||||

|

|

|

|

|

CWE |

VIN = 0 V, f = 1.0 MHz |

20 |

pF |

||

|

|

WE |

capacitance |

|||||||

|

|

|

CCS |

VIN = 0 V, f = 1.0 MHz |

20 |

pF |

||||

|

|

CS |

1-4 capacitance |

|||||||

|

|

Data I/O capacitance |

CI/O |

VI/O = 0 V, f = 1.0 MHz |

60 |

pF |

||||

|

|

Address input capacitance |

CAD |

VIN = 0 V, f = 1.0 MHz |

20 |

pF |

||||

|

|

|

|

VIN = O V, f = 1.0 MHz |

20 |

pF |

||||

|

RESET capacitance |

CRST |

||||||||

|

|

|

|

|

|

|

|

|

|

|

This parameter is guaranteed by design but not tested.

DC CHARACTERISTICS - CMOS COMPATIBLE

(VCC = 5.0V, VSS = 0V, TA = -55°C to +125°C)

Parameter |

Symbol |

|

|

|

|

|

|

|

|

|

|

Conditions |

Min |

Max |

Unit |

||

Input Leakage Current |

ILI |

VCC = 5.5, VIN = GND to VCC |

|

10 |

A |

||||||||||||

Output Leakage Current |

ILOx32 |

VCC = 5.5, VIN = GND to VCC |

|

10 |

A |

||||||||||||

VCC Active Current for Read (1) |

ICC1 |

|

|

|

|

|

= VIH, f = 5MHz |

|

640 |

mA |

|||||||

|

CS |

= VIL, |

OE |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

VCC Active Current for Program or Erase (2) |

ICC2 |

|

|

CS |

|

= VIL, OE = VIH |

|

960 |

mA |

||||||||

|

|

|

|

|

|

= Vcc ± 0.3V |

|

|

|

||||||||

VCC Standby Current |

ICC3 |

VCC = 5.5, |

CS |

= VIH, f = 5MHz, |

RESET |

|

160 |

mA |

|||||||||

Output Low Voltage |

VOL |

IOL = 12.0 mA, VCC = 4.5 |

|

0.45 |

V |

||||||||||||

Output High Voltage |

VOH |

IOH = -2.5 mA, VCC = 4.5 |

0.85 x |

|

V |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vcc |

|

|

Low VCC Lock-Out Voltage |

VLKO |

|

|

|

|

|

|

|

|

|

|

|

|

|

3.2 |

4.2 |

V |

NOTES:

1.The Icc current listed includes both the DC operating current and the frequency dependent component (@ 5MHz). The frequency component typically is less than 2mA/MHz, with OE at VIH.

2.Icc active while Embedded Algorithm (program or erase) is in progress.

3.DC test conditions VIL = 0.3V, VIH = VCC - 0.3V

White Electronic Designs Corporation • Phoenix, AZ • (602) 437-1520 |

2 |

WF8M32-XG4DX5

AC CHARACTERISTICS – WRITE/ERASE/PROGRAM OPERATIONS - WE CONTROLLED

(VCC = 5.0V, TA = -55°C to +125°C)

Parameter |

Symbol |

-100 |

|

|

-120 |

|

-150 |

Unit |

||||||

|

|

|

|

|

Min |

Max |

Min |

|

Max |

Min |

|

Max |

|

|

Write Cycle Time |

tAVAV |

tWC |

100 |

|

|

120 |

|

|

150 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Select Setup Time |

tELWL |

tCS |

0 |

|

|

0 |

|

|

0 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Enable Pulse Width |

tWLWH |

tWP |

50 |

|

|

50 |

|

|

50 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Setup Time |

tAVWL |

tAS |

0 |

|

|

0 |

|

|

0 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Setup Time |

tDVWH |

tDS |

50 |

|

|

50 |

|

|

50 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Hold Time |

tWHDX |

tDH |

0 |

|

|

0 |

|

|

0 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Hold Time |

tWLAX |

tAH |

50 |

|

|

50 |

|

|

50 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Enable Pulse Width High |

tWHWL |

tWPH |

20 |

|

|

20 |

|

|

20 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Duration of Byte Programming Operation (1) |

tWHWH1 |

|

|

|

300 |

|

|

300 |

|

|

300 |

s |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sector Erase (2) |

tWHWH2 |

|

|

|

15 |

|

|

15 |

|

|

15 |

sec |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read Recovery Time before Write |

tGHWL |

|

0 |

|

|

0 |

|

|

0 |

|

|

s |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC Setup Time |

tVCS |

|

50 |

|

|

50 |

|

|

50 |

|

|

s |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Programming Time |

|

|

|

|

44 |

|

|

44 |

|

|

44 |

sec |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Erase Time (3) |

|

|

|

|

256 |

|

|

256 |

|

|

256 |

sec |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Enable Hold Time (4) |

|

tOEH |

10 |

|

|

10 |

|

|

10 |

|

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pulse Width |

|

tRP |

500 |

|

|

500 |

|

|

500 |

|

|

ns |

RESET |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES:

1.Typical value for tWHWH1 is 7 s.

2.Typical value for tWHWH2 is 1sec.

3.Typical value for Chip Erase Time is 32sec.

4.For Toggle and Data Polling.

AC CHARACTERISTICS – READ-ONLY OPERATIONS

(VCC = 5.0V, TA = -55°C to +125°C)

Parameter |

Symbol |

|

-100 |

|

-120 |

|

-150 |

Unit |

||||||||

|

|

|

|

|

|

|

Min |

|

Max |

Min |

|

Max |

Min |

|

Max |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read Cycle Time |

tAVAV |

tRC |

100 |

|

|

120 |

|

|

150 |

|

|

ns |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Access Time |

tAVQV |

tACC |

|

|

100 |

|

|

120 |

|

|

150 |

ns |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Select Access Time |

tELQV |

tCE |

|

|

100 |

|

|

120 |

|

|

150 |

ns |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Enable to Output Valid |

tGLQV |

tOE |

|

|

50 |

|

|

50 |

|

|

55 |

ns |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Select High to Output High Z (1) |

tEHQZ |

tDF |

|

|

30 |

|

|

30 |

|

|

35 |

ns |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Enable High to Output High Z (1) |

tGHQZ |

tDF |

|

|

30 |

|

|

30 |

|

|

35 |

ns |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Hold from Addresses, |

|

or |

|

Change, |

tAXQX |

tOH |

0 |

|

|

0 |

|

|

0 |

|

|

ns |

CS |

OE |

|

|

|

|

|

|

|||||||||

whichever is First |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RST Low to Read Mode (1) |

|

tReady |

|

|

20 |

|

|

20 |

|

|

20 |

s |

||||

1. Guaranteed by design, not tested.

3 |

White Electronic Designs Corporation • Phoenix, AZ • (602) 437-1520 |

Loading...

Loading...