White Electronic Designs WMF128K8-90FFQ5A, WMF128K8-90FFQ5, WMF128K8-90FFM5A, WMF128K8-90FFM5, WMF128K8-70FEI5A Datasheet

...

WMF128K8-XXX5

HI-RELIABILITY PRODUCT

128Kx8 MONOLITHIC FLASH, SMD 5962-96690

FEATURES

■Access Times of 50*, 60, 70, 90, 120, 150ns

■Packaging

•32 lead, Hermetic Ceramic, 0.400" SOJ (Package 101)

•32 pin, Hermetic Ceramic, 0.600" DIP (Package 300)

•32 lead, Flatpack (Package 220)

•32 lead, Formed Flatpack (Package 221)

•32 pin, Rectangular Ceramic Leadless Chip Carrier (Package 601)

■100,000 Erase/Program Cycles Minimum

■Sector Erase Architecture

•8 equal size sectors of 16KBytes each

•Any combination of sectors can be concurrently erased. Also supports full chip erase

■Organized as 128Kx8

■Commercial, Industrial and Military Temperature Ranges

■5 Volt Programming. 5V ± 10% Supply.

■Low Power CMOS

■Embedded Erase and Program Algorithms

■TTL Compatible Inputs and CMOS Outputs

■Page Program Operation and Internal Program Control Time.

Note: For programming information refer to Flash Programming 1M5 Application Note.

*The access time of 50ns is available in Industrial and Commercial temperature ranges only.

PIN CONFIGURATION FOR WMF128K8-XXX5 |

PIN CONFIGURATION FOR WMF128K8-XCLX5 |

32 DIP

32 CSOJ

32 FLATPACK

TOP VIEW

NC |

|

|

1 |

32 |

|

VCC |

||||

|

|

|

||||||||

A16 |

|

|

2 |

31 |

|

|

|

|

|

|

|

|

|

WE |

|

||||||

A15 |

|

|

3 |

30 |

|

NC |

||||

|

|

|

||||||||

A12 |

|

|

4 |

29 |

|

A14 |

||||

|

|

|

||||||||

A7 |

|

|

5 |

28 |

|

A13 |

||||

|

|

|

||||||||

A6 |

|

|

6 |

27 |

|

A8 |

||||

|

|

|

||||||||

A5 |

|

|

7 |

26 |

|

A9 |

||||

|

|

|

||||||||

A4 |

|

|

8 |

25 |

|

A11 |

||||

|

|

|

||||||||

A3 |

|

|

9 |

24 |

|

|

|

|

|

|

|

|

|

OE |

|||||||

A2 |

|

|

10 |

23 |

|

A10 |

||||

|

|

|

||||||||

A1 |

|

|

11 |

22 |

|

|

|

|

||

|

|

|

CS |

|||||||

|

|

|

||||||||

A0 |

|

|

12 |

21 |

|

I/O7 |

||||

|

|

|

||||||||

I/O0 |

|

|

13 |

20 |

|

I/O6 |

||||

|

|

|

||||||||

I/O1 |

|

|

14 |

19 |

|

I/O5 |

||||

|

|

|

||||||||

I/O2 |

|

15 |

18 |

|

I/O4 |

|||||

|

|

|||||||||

VSS |

|

16 |

17 |

|

I/O3 |

|||||

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

32 CLCC

TOP VIEW

|

A12 |

A15 |

A16 |

NC |

VCC |

|

WE |

NC |

|

|

|

|

|

|

|

|

|

|

|||||||

|

4 |

3 |

2 |

1 |

32 31 30 |

|

|

|

|

|||

A7 |

5 |

|

|

|

|

|

|

29 |

A14 |

|||

A6 |

6 |

|

|

|

|

|

|

28 |

A13 |

|||

A5 |

7 |

|

|

|

|

|

|

27 |

A8 |

|||

A4 |

8 |

|

|

|

|

|

|

26 |

A9 |

|||

A3 |

9 |

|

|

|

|

|

|

25 |

A11 |

|||

A2 |

10 |

|

|

|

|

|

|

24 |

|

|||

|

|

|

|

|

|

OE |

|

|||||

A1 |

11 |

|

|

|

|

|

|

23 |

A10 |

|||

A0 |

12 |

|

|

|

|

|

|

22 |

|

|

||

|

|

|

|

|

|

|

CS |

|

|

|||

I/O0 |

13 |

|

|

|

|

|

|

21 |

I/O7 |

|||

|

14 15 16 17 18 19 20 |

|

|

|

|

|||||||

|

I/O1 |

I/O2 |

VSS |

I/O3 |

I/O4 |

|

I/O5 |

I/O6 |

|

|

|

|

|

|

|

|

|

|

|

|

PIN DESCRIPTION |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

A0-16 |

|

Address Inputs |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O0-7 |

|

Data Input/Output |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Select |

|

|

|||

|

|

CS |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

Output Enable |

|

|

|

OE |

|

|

|

|||||||

|

|

|

|

|

|

|

Write Enable |

|

|

||

|

|

WE |

|

|

|

||||||

|

VCC |

|

+5.0V Power |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

Ground |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

April 2001 Rev. 5 |

1 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

|

||||||||

WMF128K8-XXX5

ABSOLUTE MAXIMUM RATINGS (1)

Parameter |

|

Unit |

|

|

|

Operating Temperature |

-55 to +125 |

°C |

Supply Voltage Range (VCC) |

-2.0 to +7.0 |

V |

Signal voltage range (any pin except A9) (2) |

-2.0 to +7.0 |

V |

Storage Temperature Range |

-65 to +150 |

°C |

Lead Temperature (soldering, 10 seconds) |

+300 |

°C |

Data Retention Mil Temp |

10 |

years |

Endurance (write/erase cycles) Mil Temp |

10,000 min. |

cycles |

A9 Voltage for sector protect (VID) (3) |

-2.0 to +14.0 |

V |

|

|

|

NOTES:

1.Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

2.Minimum DC voltage on input or I/O pins is -0.5V. During voltage transitions, inputs may overshoot VSS to -2.0 V for periods of up to 20ns. Maximum DC voltage on output and I/O pins is VCC + 0.5V. During voltage transitions, outputs may overshoot to Vcc + 2.0 V for periods of up to 20ns.

3.Minimum DC input voltage on A9 pin is -0.5V. During voltage transitions, A9 may overshoot Vss to -2V for periods of up to 20ns. Maximum DC input voltage on A9 is +13.5V which may overshoot to 14.0 V for periods up to 20ns.

RECOMMENDED OPERATING CONDITIONS

Parameter |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

Supply Voltage |

VCC |

4.5 |

5.5 |

V |

|

|

|

|

|

Input High Voltage |

VIH |

2.0 |

VCC + 0.3 |

V |

|

|

|

|

|

Input Low Voltage |

VIL |

-0.5 |

+0.8 |

V |

|

|

|

|

|

Operating Temp. (Mil.) |

TA |

-55 |

+125 |

°C |

Operating Temp. (Ind.) |

TA |

-40 |

+85 |

°C |

A9 Voltage for Sector Protect |

VID |

11.5 |

12.5 |

V |

|

|

|

|

|

CAPACITANCE

(TA = +25°C)

Parameter |

Symbol |

Conditions |

Max |

Unit |

Address Input capacitance |

CAD |

VI/O = 0 V, f = 1.0 MHz |

15 |

pF |

Output Enable capacitance |

COE |

VIN = 0 V, f = 1.0 MHz |

15 |

pF |

Write Enable capacitance |

CWE |

VIN = 0 V, f = 1.0 MHz |

15 |

pF |

Chip Select capacitance |

CCS |

VIN = 0 V, f = 1.0 MHz |

15 |

pF |

Data I/O capacitance |

CI/O |

VI/O = 0 V, f = 1.0 MHz |

15 |

pF |

|

|

|

|

|

This parameter is guaranteed by design but not tested.

DC CHARACTERISTICS - CMOS COMPATIBLE

(VCC = 5.0V, VSS = 0V, TA = -55°C to +125°C)

Parameter |

Symbol |

|

|

|

|

|

|

|

|

|

|

Conditions |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Leakage Current |

ILI |

VCC = 5.5, VIN = GND to VCC |

|

10 |

µA |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Output Leakage Current |

ILO |

VCC = 5.5, VIN = GND to VCC |

|

10 |

µA |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC Active Current for Read (1) |

ICC1 |

|

|

|

|

= VIL, |

|

|

|

= VIH |

|

35 |

mA |

||

CS |

OE |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

VCC Active Current for Program |

ICC2 |

|

|

|

= VIH |

|

50 |

mA |

|||||||

|

CS |

= VIL, |

OE |

|

|||||||||||

or Erase (2) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

VCC Standby Current |

ICC3 |

VCC = 5.5, |

|

= VIH, f = 5MHz |

|

1.6 |

mA |

||||||||

CS |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Output Low Voltage |

VOL |

IOL = 8.0 mA, VCC = 4.5 |

|

0.45 |

V |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Output High Voltage |

VOH1 |

IOH = -2.5 mA, VCC = 4.5 |

0.85 x VCC |

|

V |

||||||||||

Output High Voltage |

VOH2 |

IOH = -100 µA, VCC = 4.5 |

VCC - 0.4 |

|

V |

||||||||||

Low VCC Lock Out Voltage |

VLKO |

|

|

|

|

|

|

|

|

|

|

|

3.2 |

|

V |

NOTES:

1.The ICC current listed includes both the DC operating current and the frequency dependent component (at 5 MHz). The frequency component typically is less than 2 mA/MHz, with OE at VIH.

2.ICC active while Embedded Algorithm (program or erase) is in progress.

3.DC test conditions: VIL = 0.3V, VIH = VCC - 0.3V

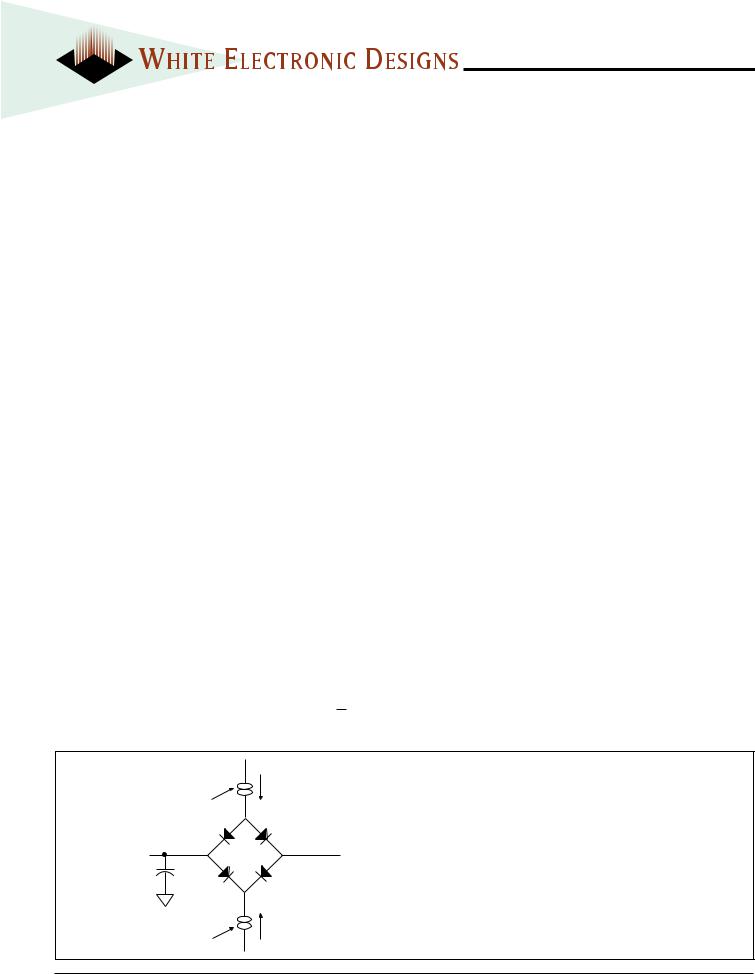

AC TEST CIRCUIT

|

I OL |

|

Current Source |

D.U.T. |

VZ ≈1.5V |

Ceff = 50 pf |

(Bipolar Supply) |

|

IOH

Current Source

AC TEST CONDITIONS

Parameter |

Typ |

Unit |

Input Pulse Levels |

VIL = 0, VIH = 3.0 |

V |

Input Rise and Fall |

5 |

ns |

|

|

|

Input and Output Reference Level |

1.5 |

V |

Output Timing Reference Level |

1.5 |

V |

|

|

|

NOTES:

VZ is programmable from -2V to +7V. IOL & IOH programmable from 0 to 16mA. Tester Impedance Z0 = 75 Ω.

VZ is typically the midpoint of VOH and VOL.

IOL & IOH are adjusted to simulate a typical resistive load circuit. ATE tester includes jig capacitance.

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

2 |

WMF128K8-XXX5

AC CHARACTERISTICS – WRITE/ERASE/PROGRAM OPERATIONS, WE CONTROLLED

(VCC = 5.0V, VSS = 0V, TA = -55°C to +125°C)

Parameter |

Symbol |

-50 |

|

|

-60 |

-70 |

|

-90 |

|

-120 |

-150 |

Unit |

|||||||||

|

|

|

|

|

Min |

Max |

Min |

|

Max |

Min |

Max |

Min |

Max |

Min |

Max |

Min |

Max |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Cycle Time |

tAVAV |

tWC |

50 |

|

|

60 |

|

|

70 |

|

|

90 |

|

|

120 |

|

150 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Select Setup Time |

tELWL |

tCS |

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Enable Pulse Width |

tWLWH |

tWP |

25 |

|

|

30 |

|

|

35 |

|

|

45 |

|

|

50 |

|

50 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Setup Time |

tAVWL |

tAS |

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Setup Time |

tDVWH |

tDS |

25 |

|

|

30 |

|

|

30 |

|

|

45 |

|

|

50 |

|

50 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Hold Time |

tWHDX |

tDH |

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Hold Time |

tWLAX |

tAH |

40 |

|

|

45 |

|

|

45 |

|

|

45 |

|

|

50 |

|

50 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Select Hold Time |

tWHEH |

tCH |

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Write Enable Pulse Width High |

tWHWL |

tWPH |

20 |

|

|

20 |

|

|

20 |

|

|

20 |

|

|

20 |

|

20 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Duration of Byte Programming Operation (min) |

tWHWH1 |

|

14 |

|

|

14 |

|

|

14 |

|

|

14 |

|

|

14 |

|

14 |

|

s |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Sector Erase Time |

tWHWH2 |

|

2.2 |

|

60 |

2.2 |

|

60 |

2.2 |

|

60 |

2.2 |

|

60 |

2.2 |

60 |

2.2 |

60 |

sec |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read Recovery Time Before Write |

tGHWL |

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC Setup Time |

|

tVCS |

50 |

|

|

50 |

|

|

50 |

|

|

50 |

|

|

50 |

|

50 |

|

s |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Programming Time |

|

|

|

|

12.5 |

|

|

12.5 |

|

|

12.5 |

|

|

12.5 |

|

12.5 |

|

12.5 |

sec |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Enable Setup Time |

|

tOES |

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Enable Hold Time (1) |

|

tOEH |

10 |

|

|

10 |

|

|

10 |

|

|

10 |

|

|

10 |

|

10 |

|

ns |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1. For Toggle and Data Polling.

AC CHARACTERISTICS – READ ONLY OPERATIONS

(VCC = 5.0V, VSS = 0V, TA = -55°C to +125°C)

|

Parameter |

Symbol |

-50 |

|

-60 |

-70 |

-90 |

-120 |

-150 |

Unit |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

Min |

Max |

Min Max |

Min Max |

Min Max |

Min Max |

Min Max |

|

||||||

|

Read Cycle Time |

tAVAV |

tRC |

50 |

|

|

60 |

|

70 |

|

90 |

|

120 |

|

150 |

|

ns |

||||||

|

Address Access Time |

tAVQV |

tACC |

|

|

50 |

|

60 |

|

70 |

|

90 |

|

120 |

|

150 |

ns |

||||||

|

Chip Select Access Time |

tELQV |

tCE |

|

|

50 |

|

60 |

|

70 |

|

90 |

|

120 |

|

150 |

ns |

||||||

|

|

to Output Valid |

tGLQV |

tOE |

|

|

25 |

|

30 |

|

35 |

|

40 |

|

50 |

|

55 |

ns |

|||||

|

OE |

|

|

||||||||||||||||||||

|

Chip Select to Output High Z (1) |

tEHQZ |

tDF |

|

|

20 |

|

20 |

|

20 |

|

25 |

|

30 |

|

35 |

ns |

||||||

|

|

|

High to Output High Z (1) |

tGHQZ |

tDF |

|

|

20 |

|

20 |

|

20 |

|

25 |

|

30 |

|

35 |

ns |

||||

|

OE |

|

|

||||||||||||||||||||

|

Output Hold from Address, |

|

or |

|

Change, |

tAXQX |

tOH |

0 |

|

|

0 |

|

0 |

|

0 |

|

0 |

|

0 |

|

ns |

||

|

CS |

OE |

|

||||||||||||||||||||

|

whichever is first |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1. Guaranteed by design, not tested.

3 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

WMF128K8-XXX5

AC CHARACTERISTICS – WRITE/ERASE/PROGRAM OPERATIONS, CS CONTROLLED

(VCC = 5.0V, VSS = 0V, TA = -55°C to +125°C)

Parameter |

Symbol |

-50 |

-60 |

|

-70 |

|

|

-90 |

-120 |

-150 |

Unit |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Min |

Max |

Min |

Max |

Min |

Max |

Min |

|

Max |

Min |

Max |

Min |

Max |

|

||

|

|

Write Cycle Time |

tAVAV |

tWC |

50 |

|

60 |

|

|

70 |

|

|

90 |

|

|

120 |

|

150 |

|

ns |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tWLEL |

tWS |

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

|

|

|

WE |

Setup Time |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pulse Width |

tELEH |

tCP |

25 |

|

30 |

|

|

35 |

|

|

45 |

|

|

50 |

|

50 |

|

ns |

|||

|

|

CS |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Setup Time |

tAVEL |

tAS |

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Setup Time |

tDVEH |

tDS |

25 |

|

30 |

|

|

30 |

|

|

45 |

|

|

50 |

|

50 |

|

ns |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Data Hold Time |

tEHDX |

tDH |

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Address Hold Time |

tELAX |

tAH |

40 |

|

45 |

|

|

45 |

|

|

45 |

|

|

50 |

|

50 |

|

ns |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

High |

tEHWH |

tWH |

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

|||

|

|

WE |

Hold from |

WE |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tEHEL |

tCPH |

20 |

|

20 |

|

|

20 |

|

|

20 |

|

|

20 |

|

20 |

|

ns |

||||||

|

|

CS |

Pulse Width High |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Duration of Programming Operation |

tWHWH1 |

|

14 |

|

14 |

|

|

14 |

|

|

14 |

|

|

14 |

|

14 |

|

s |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Duration of Erase Operation |

tWHWH2 |

|

2.2 |

60 |

2.2 |

|

60 |

2.2 |

|

60 |

2.2 |

|

60 |

2.2 |

60 |

2.2 |

60 |

sec |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Read Recovery before Write |

tGHEL |

|

0 |

|

0 |

|

|

0 |

|

|

0 |

|

|

0 |

|

0 |

|

ns |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Chip Programming Time |

|

|

|

12.5 |

|

|

12.5 |

|

|

12.5 |

|

|

12.5 |

|

12.5 |

|

12.5 |

sec |

||||||

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

4 |

WMF128K8-XXX5

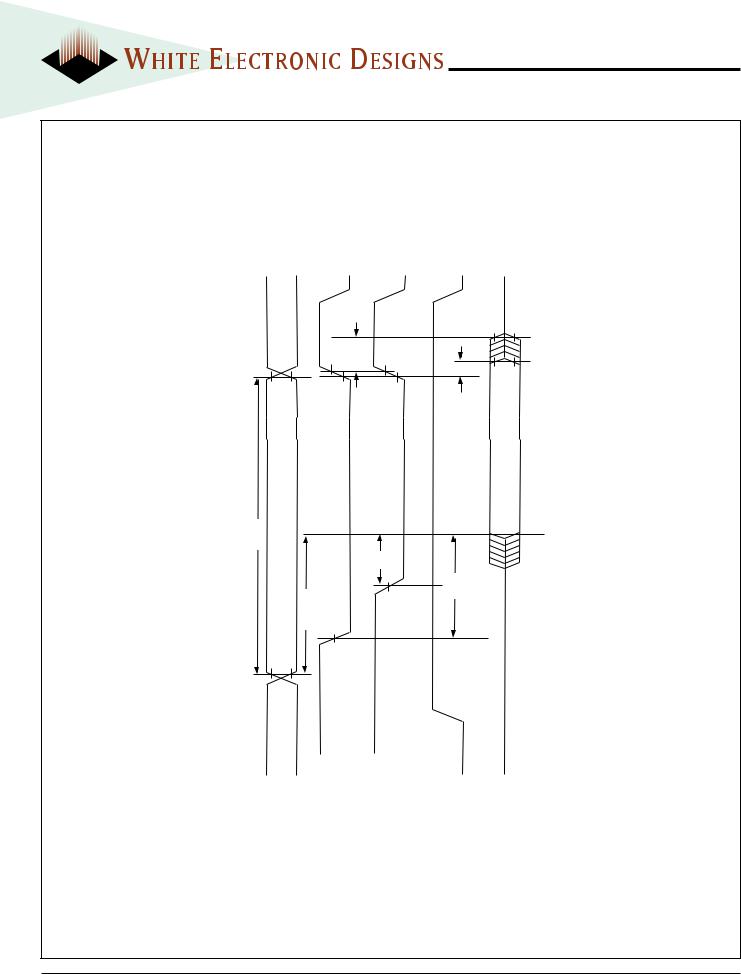

AC WAVEFORMS FOR READ OPERATIONS

High Z

tDF

tOH

Output Valid

tRC |

Addresses Stable |

tOE |

|

|

tCE |

|

|

tACC |

High Z

Addresses |

|

CS |

|

OE |

|

WE |

Outputs |

|

|

|

|||||

|

|

||||||

|

|

|

|

|

|

5 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

Loading...

Loading...