White Electronic Designs WED9LC6416V2012BI, WED9LC6416V2012BC, WED9LC6416V2010BI, WED9LC6416V2010BC, WED9LC6416V1612BI Datasheet

...

WED9LC6416V

128Kx32 SSRAM/4Mx32 SDRAM Advanced*

External Memory Solution for Texas Instruments TMS320C6000 DSP

FEATURES

■Clock speeds:

•SSRAM: 200, 166,150, and 133 MHz

•SDRAMs: 125 and 100 MHz

■DSP Memory Solution

•Texas Instruments TMS320C6201

•Texas Instruments TMS320C6701

■Packaging:

•153 pin BGA, JEDEC MO-163

■3.3V Operating supply voltage

■Direct control interface to both the SSRAM and SDRAM ports on the “C6x”

■Common address and databus

■65% space savings vs. monolithic solution

■Reduced system inductance and capacitance

DESCRIPTION

The WED9LC6416VxxBC is a 3.3V, 128K x 32 Synchronous Pipeline SRAM and a 4Mx32 Synchronous DRAM array constructed with one 128K x 32 SBSRAM and two 4Mx16 SDRAM die mounted on a multilayer laminate substrate. The device is packaged in a 153 lead, 14mm by 22mm, BGA.

The WED9LC6416VxxBC provides a total memory solution for the Texas Instruments TMS320C6201 and the TMS320C6701 DSPs

The Synchronous Pipeline SRAM is available with clock speeds of 200, 166,150, and 133 MHz, allowing the user to develop a fast external memory for the SSRAM interface port .

The SDRAM is available in clock speeds of 125 and 100 MHz, allowing the user to develop a fast external memory for the SDRAM interface port .

The WED9LC6416V is available in both commercial and industrial temperature ranges.

*This data sheet describes a product that may or may not be under development and is subject to change or cancellation without notice.

FIG. 1 PIN CONFIGURATION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

TOP VIEW |

|

|

|

|

|

|

|

|

|

PIN DESCRIPTION |

|||||||||||||||||||||||

|

1 |

2 |

3 |

4 |

|

|

|

|

|

5 |

|

|

|

|

|

|

6 |

7 |

8 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

A0-16 |

Address Bus |

|

||||||||||||||||||||||||||||||||

A |

DQ19 |

DQ23 |

VCC |

|

|

|

VSS |

|

|

|

|

VSS |

VSS |

VCC |

DQ24 |

DQ28 |

A |

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

DQ0-31 |

Data Bus |

|

|||||||||||||||||||||||||||||||||||

B |

DQ18 |

DQ22 |

VCC |

|

|

|

VSS |

|

|

|

|

|

|

|

|

|

|

|

VSS |

VCC |

DQ25 |

DQ29 |

B |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

SDCE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

SSCLK |

SSRAM Clock |

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

C |

VCCQ |

VCCQ |

VCC |

|

|

|

SDWE |

|

|

SDA10 |

NC |

VCC |

VCCQ |

VCCQ |

C |

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSADC |

SSRAM Address Status Control |

|

|||||||

D |

DQ17 |

DQ21 |

VCC |

|

|

|

VSS |

|

|

|

|

VSS |

VSS |

VCC |

DQ26 |

DQ30 |

D |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSWE |

SSRAM Write Enable |

|

||||||

E |

DQ16 |

DQ20 |

VCC |

|

|

|

VSS |

|

SDCLK |

VSS |

VCC |

DQ27 |

DQ31 |

E |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

F |

VCCQ |

VCCQ |

VCC |

|

|

|

VSS |

|

|

|

|

VSS |

VSS |

VCC |

VCCQ |

VCCQ |

F |

|

|

|

SSOE |

SSRAM Output Enable |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

SDCLK |

SDRAM Clock |

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

G |

NC |

NC |

NC |

SDRAS |

SDCAS |

VSS |

A2 |

A4 |

A5 |

G |

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

H |

NC |

NC |

A8 |

|

|

|

VSS |

|

|

|

|

VSS |

NC |

A1 |

A3 |

A10 |

H |

|

|

SDRAS |

SDRAM Row Address Strobe |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

A6 |

A7 |

A9 |

|

|

|

VSS |

|

|

|

|

VSS |

NC |

A0 |

A11 |

A12 |

J |

|

|

SDCAS |

SDRAM Column Address Strobe |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

K |

NC / A17 |

NC / A18 |

NC / A19 |

|

|

|

VSS |

|

|

|

|

VSS |

NC |

NC |

A13 |

A14 |

K |

|

|

|

SDWE |

SDRAM Write Enable |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L |

NC |

NC |

NC |

|

|

|

|

2 |

|

|

|

3 |

NC |

NC |

A15 |

A16 |

L |

|

|

|

SDA10 |

SDRAM Address 10/auto precharge |

|

|||||||||||||||||

|

|

|

BWE |

|

|

BWE |

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

M |

VCCQ |

VCCQ |

VCC |

|

|

|

|

|

|

|

|

|

NC |

VCC |

VCCQ |

VCCQ |

M |

|

|

|

|

|

|

|

|

|

|

SSRAM Byte Write Enables |

|

|||||||||||

|

|

|

BWE |

0 |

|

|

BWE |

1 |

|

|

BWE0-3 |

|

||||||||||||||||||||||||||||

N |

DQ12 |

DQ11 |

VCC |

|

|

|

VSS |

|

|

|

|

VSS |

VSS |

VCC |

DQ4 |

DQ0 |

N |

|

|

|

|

|

|

|

|

|

|

SDRAM SDQM 0 - 3 |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

P |

DQ13 |

DQ10 |

VCC |

|

|

|

VSS |

|

SSCLK |

VSS |

VCC |

DQ5 |

DQ1 |

P |

|

|

|

|

SSCE |

Chip Enable SSRAM Device |

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||

R |

VCCQ |

VCCQ |

VCC |

|

|

|

VSS |

|

|

|

|

VSS |

VSS |

VCC |

VCCQ |

VCCQ |

R |

|

|

|

SDCE |

Chip Enable SDRAM Device |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

Power Supply pins, 3.3V |

|

|||||

T |

DQ14 |

DQ9 |

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

VCC |

DQ6 |

DQ2 |

T |

|

|

|

|

|

|||||||||||

SSADC |

|

|

SSWE |

|

|

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCCQ |

Data Bus Power Supply pins, |

|

|||||

U |

DQ15 |

DQ8 |

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

VCC |

DQ7 |

DQ3 |

U |

|

|

|

|

|

|||||||||||||

|

SSOE |

|

|

SSCE |

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3.3V (2.5V future) |

|

|

1 |

2 |

3 |

4 |

|

|

|

|

|

5 |

|

|

|

|

|

|

6 |

7 |

8 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

VSS |

Ground |

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

No Connect |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

January 20001 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

||||||||||||

WED9LC6416V

FIG. 2 BLOCK DIAGRAM

A0-16 |

A0 |

A0 |

|

|

A1 |

|

|

|

A1 |

|

|

|

|

|

|

|

|

A2 |

|

|

|

A3 |

|

|

|

A4 |

DQ0-7 |

|

|

A5 |

|

|

|

A6 |

DQ1-8 |

|

|

DQ8-15 |

|

|

|

A7 |

|

|

|

A8 |

DQ9-16 |

|

|

DQ16-23 |

|

|

|

A9 |

|

|

|

DQ17-24 |

|

|

|

A10 |

|

|

|

DQ24-31 |

|

|

|

A11 |

|

|

|

DQ25-32 |

|

|

|

A12 |

|

|

|

|

|

|

|

A13 |

|

|

|

A14 |

|

|

|

A15 |

|

|

|

A16 |

|

SSWE |

|

BWE |

|

BWE0 |

|

BW1 |

|

BWE1 |

|

BW2 |

|

BWE2 |

|

BW3 |

|

BWE3 |

|

BW4 |

|

SSCE |

|

CE2 |

|

SSOE |

|

OE |

|

SSADC |

|

ADSC |

|

SSCLK |

|

CLK |

|

|

|

A0 |

DQ0-31 |

|

|

|

|

|

|

A1 |

|

|

|

A2 |

|

|

|

A3 |

|

|

|

A4 |

|

|

|

A5 |

|

|

|

A6 |

|

|

|

A7 |

DQ0-7 |

|

|

A8 |

|

|

|

DQ0-7 |

|

|

|

A9 |

DQ8-15 |

|

|

A11 |

|

SDA10 |

|

A10/AP |

DQ8-15 |

A12 |

|

||

BA0 |

|

||

|

A13 |

|

|

|

BA1 |

|

|

|

|

|

|

|

|

LDQM |

|

SDCE |

|

UDQM |

|

|

CS |

|

|

SDRAS |

|

RAS |

|

SDCAS |

|

CAS |

|

SDWE |

|

WE |

|

SDCLK |

|

CLK |

|

|

|

A0 |

|

|

|

A1 |

|

|

|

A2 |

|

|

|

A3 |

|

|

|

A4 |

|

|

|

A5 |

|

|

|

A6 |

|

|

|

A7 |

DQ16-23 |

|

|

A8 |

|

|

|

DQ0-7 |

|

|

|

A9 |

DQ24-31 |

|

|

A11 |

|

|

|

DQ8-15 |

|

|

A12 |

A10/AP |

|

|

BA0 |

|

|

|

A13 |

|

|

|

BA1 |

|

|

|

|

|

|

|

|

LDQM |

|

|

|

UDQM |

|

|

|

CS |

|

|

|

RAS |

|

|

|

CAS |

|

|

|

WE |

|

|

|

CLK |

|

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

2 |

January 2001 |

WED9LC6416V

OUTPUT FUNCTIONAL DESCRIPTIONS

|

Symbol |

Type |

Signal |

Polarity |

|

|

Function |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSCLK |

Input |

Pulse |

Positive Edge |

The system clock input. All of the SSRAM inputs are sampled on the rising edge of the clock. |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

SSADS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

When sampled at the positive rising edge of the clock, SSADS, SSOE, and SSWE define the operation |

|||||||||||||||

|

|

|

SSOE |

Input |

Pulse |

Active Low |

|||||||||||||||

|

|

|

to be executed by the SSRAM. |

||||||||||||||||||

|

|

SSWE |

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

Input |

Pulse |

Active Low |

|

|

disable or enable SSRAM device operation. |

||||||||||

|

|

|

SSCE |

SSCE |

|||||||||||||||||

|

|

SDCLK |

Input |

Pulse |

Positive Edge |

The system clock input. All of the SDRAM inputs are sampled on the rising edge of the clock. |

|||||||||||||||

|

|

|

SDCE |

Input |

Pulse |

Active Low |

SDCE disable or enable device operation by masking or enabling all inputs except SDCLK and BWE0-3. |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDRAS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

When sampled at the positive rising edge of the clock, SDCAS, SDRAS, and SDWE define the operation |

|||||||||||||||

|

SDCAS |

Input |

Pulse |

Active Low |

|||||||||||||||||

|

to be executed by the SDRAM. |

||||||||||||||||||||

|

|

SDWE |

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

Address bus for SSRAM and SDRAM |

|||||||||||

|

|

|

|

|

|

|

|

|

|

A0 and A1 are the burst address inputs for the SSRAM |

|||||||||||

|

|

|

|

|

|

|

|

|

|

During a Bank Active command cycle, A0-11, SDA10 defines the row address (RA0-10) when sampled at the |

|||||||||||

|

|

|

|

|

|

|

|

|

|

rising clock edge. |

|||||||||||

|

|

|

A0-16, |

Input |

Level |

— |

During a Read or Write command cycle, A0-7 defines the column address (CA0-7) when sampled at the |

||||||||||||||

|

|

SDA10 |

rising clock edge. In addition to the row address, SDA10 is used to invoke Autoprecharge operation at the |

||||||||||||||||||

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

end of the Burst Read or Write Cycle. If SDA10 is high, autoprecharge is selected and A12 and A13 define |

|||||||||||

|

|

|

|

|

|

|

|

|

|

the bank to be precharged. If SDA10 is low, autoprecharge is disabled. |

|||||||||||

|

|

|

|

|

|

|

|

|

|

During a Precharge command cycle, SDA10 is used in conjunction with A12 and A13 to control which bank(s) |

|||||||||||

|

|

|

|

|

|

|

|

|

|

to precharge. If SDA10 is high, all banks will be precharged regardless of the state of A12 and A13. If |

|||||||||||

|

|

|

|

|

|

|

|

|

|

SDA10 is low, then A12 and A13 are used to define which bank to precharge. |

|||||||||||

|

|

DQ0-31 |

Input |

Level |

— |

Data Input/Output are multiplexed on the same pins. |

|||||||||||||||

|

|

Output |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BWE0-3 |

Input |

Pulse |

|

BWE0-3 perform the byte write enable function for the SSRAM and DQM function for the SDRAM. BWE0 |

||||||||||||||||

|

|

is associated with DQ0-7, BWE1 with DQ8-15, BWE2 with DQ16-23 and BWE3 with DQ24-31. |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vcc, Vss |

Supply |

|

|

Power and ground for the input buffers and the core logic. |

|||||||||||||||||

|

|

|

VCCQ |

Supply |

|

|

Data base power supply pins, 3.3V (2.5V future). |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

January 20001 |

3 |

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

WED9LC6416V

ABSOLUTE MAXIMUM RATINGS |

|

|

RECOMMENDED DC OPERATING CONDITIONS |

|||||||

|

|

|

|

(VCC = 3.3V -5% / +10% unless otherwise noted; |

|

|||||

Voltage on Vcc Relative to Vss |

-0.5V to +4.6V |

|

|

|||||||

|

0° C ≤ TA ≤ |

70° C, Commercial; |

-40° C ≤ |

TA ≤ 85° C, Industrial) |

||||||

Vin (DQx) |

-0.5V to Vcc +0.5V |

|

||||||||

|

|

|

|

|

|

|

|

|||

Storage Temperature (BGA) |

-55° |

C to +125° C |

|

Parameter |

|

|

Symbol |

Min |

Max |

Units |

|

Supply Voltage (1) |

|

VCC |

3.135 |

3.6 |

V |

||||

Junction Temperature |

|

+175° C |

|

|

||||||

|

|

Input High Voltage (1,2) |

|

VIH |

2.0 |

VCC +0.3 |

V |

|||

Short Circuit Output Current |

|

100 mA |

|

|

||||||

|

|

Input Low Voltage (1,2) |

|

VIL |

-0.3 |

0.8 |

V |

|||

*Stress greater than those listed under "Absolute Maximum Ratings" may cause |

|

|||||||||

Input Leakage Current |

|

ILI |

-10 |

10 |

A |

|||||

permanent damage to the device. This is a stress rating only and functional operation |

|

|||||||||

0 ≤ VIN ≤ Vcc |

|

|

|

|

|

|

||||

of the device at these or any other conditions greater than those indicated in operational |

|

|

|

|

|

|

||||

Output Leakage (Output Disabled) |

|

ILo |

-10 |

10 |

A |

|||||

sections of this specifications is not implied. Exposure to absolute maximum rating |

|

|||||||||

0 ≤ VIN ≤ Vcc |

|

|

|

|

|

|

||||

conditions for extended periods may affect reliability. |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output High (IOH = -4mA) (1) |

|

VOH |

2.4 |

— |

V |

||

|

|

|

|

|

||||||

|

|

|

|

Output Low (IOL = 8mA) (1) |

|

VOL |

— |

0.4 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES: |

|

|

|

|

|

|

|

|

|

|

1. All voltages referenced to Vss (GND). |

|

|

|

|||

|

|

|

|

2. Overshoot: VIH ≤ +6.0V for t ≤ tKC/2 |

|

|

|

|||

|

|

|

|

Underershoot: |

VIL ≥ -2.0V for t ≤ |

tKC/2 |

|

|

|

|

DC ELECTRICAL CHARACTERISTICS

|

(VCC = 3.3V -5% / +10% unless otherwise noted; |

0° C ≤ TA ≤ 70° C, Commercial; -40° C ≤ |

TA ≤ 85° C, Industrial) |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Description |

|

|

|

|

|

|

|

Conditions |

|

Symbol |

Frequency |

|

Typ |

Max |

Units |

||

Power Supply Current: |

|

|

|

|

|

|

|

|

|

|

|

|

133MHz |

|

400 |

550 |

|

|

|

SSRAM Active / DRAM Auto Refresh |

|

Icc1 |

150MHz |

|

450 |

580 |

mA |

||||||||

Operating (1,2,3) |

|

|

|

|

|||||||||||||

|

|

|

166MHz |

|

500 |

625 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

200MHz |

|

550 |

700 |

|

Power Supply Current |

|

|

|

|

|

|

|

|

|

|

|

|

133MHz |

|

300 |

450 |

|

|

|

SSRAM Active / DRAM Idle |

|

Icc2 |

150MHz |

|

350 |

480 |

mA |

||||||||

Operating (1,2,3) |

|

|

|

|

|||||||||||||

|

|

|

166MHz |

|

400 |

525 |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

200MHz |

|

450 |

585 |

|

Power Supply Current |

|

|

|

|

|

|

|

|

|

|

|

|

83MHz |

|

220 |

240 |

|

|

|

SDRAM Active / SSRAM Idle |

|

Icc3 |

100MHz |

|

235 |

250 |

mA |

||||||||

Operating (1,2,3) |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

125MHz |

|

255 |

280 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

and |

|

|

≤ Vcc -0.2V, |

|

|

|

|

|

|

|

|

|

|

SSCE |

SDCE |

|

ISB1 |

|

|

20.0 |

40.0 |

|

|||||||

CMOS Standby |

|

|

All other inputs at Vss +0.2 ≤ VIN or |

|

|

|

mA |

||||||||||

|

|

|

VIN ≤ VCC -0.2V, Clk frequency = 0 |

|

|

|

|

|

|

|

|||||||

|

|

|

|

and |

|

≤ VIH min |

|

|

|

|

|

|

|

||||

TTL Standby |

|

|

SSCE |

SDCE |

|

ISB2 |

|

|

30.0 |

55.0 |

|

||||||

|

|

All other inputs at VIL max ≤ VIN or |

|

|

|

mA |

|||||||||||

|

|

|

VIN ≤ VCC -0.2V, Clk frequency = 0 |

|

|

|

|

|

|

|

|||||||

Auto Refresh |

|

|

|

|

|

|

|

|

|

|

|

Icc5 |

|

|

190 |

250 |

mA |

NOTES:

1.ICC (operating) is specified with no output current. ICC (operating) increases with faster cycle times and greater output loading.

2."Device idle" means device is deselected (CE ≥ VIH) Clock is running at max frequency and Addresses are switching each cycle.

3.Typical values are measured at 3.3V, 25° C. ICC (operating) is specified at specified frequency.

BGA CAPACITANCE

Description |

Conditions |

Symbol |

Typ |

Max |

Units |

Address Input Capacitance (1) |

TA = 25° C; f = 1MHz |

CI |

5 |

8 |

pF |

Input/Output Capacitance (DQ) (1) |

TA = 25° C; f = 1MHz |

CO |

8 |

10 |

pF |

Control Input Capacitance (1) |

TA = 25° C; f = 1MHz |

CA |

5 |

8 |

pF |

Clock Input Capacitance (1) |

TA = 25° C; f = 1MHz |

CCK |

4 |

6 |

pF |

NOTE:

1. This parameter is sampled.

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com 4 January 2001

WED9LC6416V

SSRAM AC CHARACTERISTICS

(VCC = 3.3V -5% / +10% unless otherwise noted; 0° C ≤ |

TA ≤ |

70° C, Commercial; |

-40° C ≤ TA ≤ |

85° C, Industrial) |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

200MHz |

|

166MHz |

|

150MHz |

133MHz |

|

|||||

Parameter |

|

Min |

Max |

|

Min |

Max |

|

Min |

Max |

Min |

Max |

Units |

|

Clock Cycle Time |

tKHKH |

5 |

|

|

|

6 |

|

|

7 |

|

8 |

|

ns |

Clock HIGH Time |

tKLKH |

1.6 |

|

|

|

2.4 |

|

|

2.6 |

|

2.8 |

|

ns |

Clock LOW Time |

tKHKL |

1.6 |

|

|

|

2.4 |

|

|

2.6 |

|

2.8 |

|

ns |

Clock to output valid |

tKHQV |

|

|

2.5 |

|

|

3.5 |

|

|

3.8 |

|

4.0 |

ns |

Clock to output invalid |

tKHQX |

1.5 |

|

|

|

1.5 |

|

|

1.5 |

|

1.5 |

|

ns |

Clock to output on Low-Z |

tKQLZ |

0 |

|

|

|

0 |

|

|

0 |

|

0 |

|

ns |

Clock to output in High-Z |

tKQHZ |

1.5 |

|

3 |

|

1.5 |

3.5 |

|

1.5 |

3.8 |

1.5 |

4.0 |

ns |

Output Enable to output valid |

tOELQV |

|

|

2.5 |

|

|

3.5 |

|

|

3.8 |

|

4.0 |

ns |

Output Enable to output in Low-Z |

tOELZ |

0 |

|

|

|

0 |

|

|

0 |

|

0 |

|

ns |

Output Enable to output in High-Z |

tOEHZ |

|

|

3.0 |

|

|

3.5 |

|

|

3.5 |

|

3.8 |

ns |

Address, Control, Data-in Setup Time to Clock |

tS |

1.5 |

|

|

|

1.5 |

|

|

1.5 |

|

1.5 |

|

ns |

Address, Control, Data-in Hold Time to Clock |

tH |

0.5 |

|

|

|

0.5 |

|

|

0.5 |

|

0.5 |

|

ns |

January 20001 |

5 |

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

WED9LC6416V

SSRAM OPERATION TRUTH TABLE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Operation |

Address Used |

SSCE |

|

SSADS |

SSWE |

SSOE |

DQ |

|||||||

Deselected Cycle, Power Down |

None |

|

H |

|

L |

|

X |

|

X |

High-Z |

||||

WRITE Cycle, Begin Burst |

External |

|

L |

|

L |

|

L |

|

X |

D |

||||

READ Cycle, Begin Burst |

External |

|

L |

|

L |

|

H |

|

L |

Q |

||||

READ Cycle, Begin Burst |

External |

|

L |

|

L |

|

H |

|

H |

High-Z |

||||

READ Cycle, Suspend Burst |

Current |

|

X |

|

H |

|

H |

|

L |

Q |

||||

READ Cycle, Suspend Burst |

Current |

|

X |

|

H |

|

H |

|

H |

High-Z |

||||

READ Cycle, Suspend Burst |

Current |

|

H |

|

H |

|

H |

|

L |

Q |

||||

READ Cycle, Suspend Burst |

Current |

|

H |

|

H |

|

H |

|

H |

High-Z |

||||

WRITE Cycle, Suspend Burst |

Current |

|

X |

|

H |

|

L |

|

X |

D |

||||

WRITE Cycle, Suspend Burst |

Current |

|

H |

|

H |

|

L |

|

X |

D |

||||

NOTE:

1.X means “don’t care”, H means logic HIGH. L means logic LOW.

2.All inputs except SSOE must meet setup and hold times around the rising edge (LOW to HIGH) of SSCLK.

3.Suspending burst generates wait cycle

4.For a write operation following a read operation, SSOE must be HIGH before the input data required setup time plus High-Z time for SSOE and staying HIGH though out the input data hold time.

5.This device contains circuitry that will ensure the outputs will be in High-Z during power-up.

SSRAM PARTIAL TRUTH TABLE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Function |

SSWE |

BWE0 |

|

BWE1 |

BWE2 |

BWE3 |

|||||||||

READ |

|

H |

|

X |

|

X |

|

X |

|

X |

|||||

WRITE one Byte (DQ0-7) |

|

L |

|

L |

|

H |

|

H |

|

H |

|||||

WRITE all Bytes |

|

L |

|

L |

|

L |

|

L |

|

L |

|||||

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

6 |

January 2001 |

WED9LC6416V

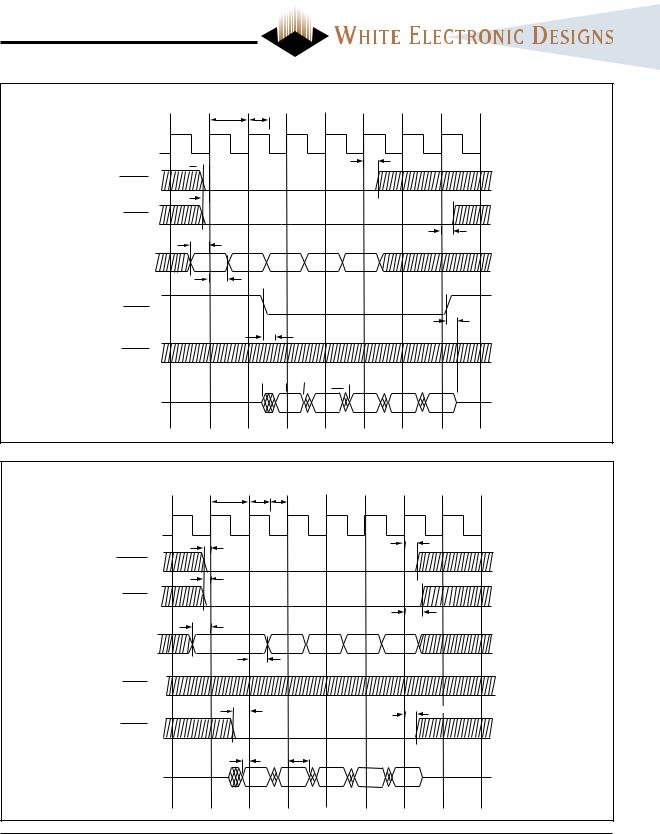

FIG. 3 SSRAM READ TIMING

tKHKH tKHKL

tKLKH

tKLKH

SSCLK

tS

tH

tH

SSADS

tS

tS

SSCE

tH

tS

ADDR |

A1 |

A2 |

A3 |

A4 |

A5 |

tH

SSOE

tOEHQZ

tOELQV

SSWE

tKHQX tKHQV tKQLZ

DQ |

Q(A1) |

Q(A2) |

Q(A3) |

Q(A4) |

Q(A5) |

FIG. 4 SSRAM WRITE TIMING

|

tKHKH |

tKHKL |

|

|

|

|

|

tKLKH |

|

|

|

SSCLK |

|

|

|

|

|

|

tS |

|

|

|

tH |

|

|

|

|

|

|

SSADS |

|

|

|

|

|

|

tH |

|

|

|

|

SSCE |

|

|

|

|

|

|

|

|

|

|

tH |

|

tS |

|

|

|

|

ADDR |

A1 |

A2 |

A3 |

A4 |

A5 |

|

tH |

|

|

|

|

SSOE |

|

|

|

|

|

|

|

tS |

|

|

KHG WX |

|

|

|

|

|

tH |

SSWE |

|

|

|

|

|

|

|

tH |

|

|

|

|

|

t S |

|

|

|

DQ |

|

D(A1) D(A2) |

D(A3) |

D(A4) |

D(A5) |

January 20001 |

7 |

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

WED9LC6416V

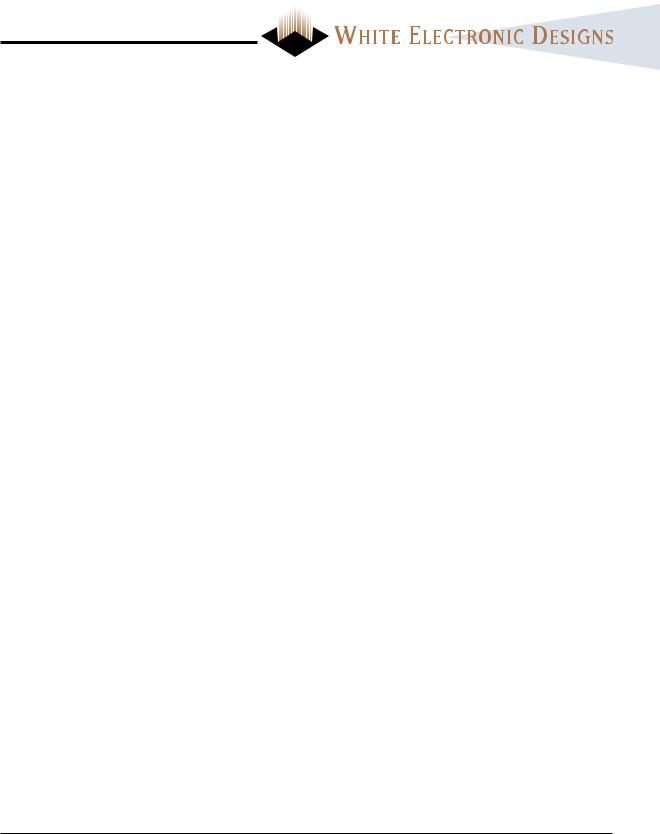

SDRAM AC CHARACTERISTICS

(VCC = 3.3V -5% / +10% unless otherwise noted; 0° C ≤ TA ≤ 70° C, Commercial; |

-40° C ≤ TA ≤ |

85° C, Industrial) |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

|

125MHz |

|

100MHz |

|

|

83MHz |

|

|||

Parameter |

|

|

Min |

|

Max |

Min |

|

Max |

|

Min |

|

Max |

Units |

Clock Cycle Time (1) |

CL = 3 |

tCC |

8 |

|

1000 |

10 |

|

1000 |

|

12 |

|

1000 |

ns |

CL = 2 |

tCC |

10 |

|

1000 |

12 |

|

1000 |

|

15 |

|

1000 |

||

|

|

|

|

|

|

||||||||

Clock to valid Output delay (1,2) |

|

tSAC |

|

|

6 |

|

|

7 |

|

|

|

8 |

ns |

Output Data Hold Time (2) |

|

tOH |

3 |

|

|

3 |

|

|

|

3 |

|

|

ns |

Clock HIGH Pulse Width (3) |

|

tCH |

3 |

|

|

3 |

|

|

|

3 |

|

|

ns |

Clock LOW Pulse Width (3) |

|

tCL |

3 |

|

|

3 |

|

|

|

3 |

|

|

ns |

Input Setup Time (3) |

|

tSS |

2 |

|

|

2 |

|

|

|

2 |

|

|

ns |

Input Hold Time (3) |

|

tSH |

1 |

|

|

1 |

|

|

|

1 |

|

|

ns |

CLK to Output Low-Z (2) |

|

tSLZ |

2 |

|

|

2 |

|

|

|

2 |

|

|

ns |

CLK to Output High-Z |

|

tSHZ |

|

|

7 |

|

|

7 |

|

|

|

8 |

ns |

Row Active to Row Active Delay (4) |

|

tRRD |

20 |

|

|

20 |

|

|

|

24 |

|

|

ns |

RAS\ to CAS\ Delay (4) |

|

tRCD |

20 |

|

|

20 |

|

|

|

24 |

|

|

ns |

Row Precharge Time (4) |

|

tRP |

20 |

|

|

20 |

|

|

|

24 |

|

|

ns |

Row Active Time (4) |

|

tRAS |

50 |

|

10,000 |

50 |

|

10,000 |

|

60 |

|

10,000 |

ns |

Row Cycle Time - Operation (4) |

|

tRC |

70 |

|

|

80 |

|

|

|

90 |

|

|

ns |

Row Cycle Time - Auto Refresh (4,8) |

|

tRFC |

70 |

|

|

80 |

|

|

|

90 |

|

|

ns |

Last Data in to New Column Address Delay (5) |

tCDL |

1 |

|

|

1 |

|

|

|

1 |

|

|

CLK |

|

Last Data in to Row Precharge (5) |

|

tRDL |

1 |

|

|

1 |

|

|

|

1 |

|

|

CLK |

Last Data in to Burst Stop (5) |

|

tBDL |

1 |

|

|

1 |

|

|

|

1 |

|

|

CLK |

Column Address to Column Address Delay (6) |

tCCD |

1.5 |

|

|

1.5 |

|

|

|

1.5 |

|

|

CLK |

|

Number of Valid Output Data (7) |

|

|

2 |

|

|

2 |

|

|

|

2 |

|

|

ea |

|

|

|

1 |

|

|

2 |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

NOTES:

1.Parameters depend on programmed CAS latency.

2.If clock rise time is longer than 1ns (trise/2 -0.5)ns should be added to the parameter.

3.Assumed input rise and fall time = 1ns. If trise of tfall are longer than 1ns. [(trise = tfall)/2] - 1ns should be added to the parameter.

4.The minimum number of clock cycles required is detemined by dividing the minimum time required by the clock cycle time and then rounding up to the next higher integer.

5.Minimum delay is required to complete write.

6.All devices allow every cycle column address changes.

7.In case of row precharge interrupt, auto precharge and read burst stop.

8.A new command may be given tRFC after self-refresh exit.

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

8 |

January 2001 |

WED9LC6416V

CLOCK FREQUENCY AND LATENCY PARAMETERS - 125MHz SDRAM

(Unit = number of clock)

Frequency |

CAS |

tRC |

tRAS |

tRP |

tRRD |

tRCD |

tCCD |

tCDL |

tRDL |

|

Latency |

70ns |

50ns |

20ns |

20ns |

20ns |

10ns |

10ns |

10ns |

|

|

||||||||

125MHz (8.0ns) |

3 |

9 |

6 |

3 |

2 |

3 |

1 |

1 |

1 |

100MHz (10.0ns) |

3 |

7 |

5 |

2 |

2 |

2 |

1 |

1 |

1 |

83MHz (12.0ns) |

2 |

6 |

4 |

2 |

2 |

2 |

1 |

1 |

1 |

CLOCK FREQUENCY AND LATENCY PARAMETERS - 100MHz SDRAM

(Unit = number of clock)

Frequency |

CAS |

tRC |

tRAS |

tRP |

tRRD |

tRCD |

tCCD |

tCDL |

tRDL |

|

Latency |

70ns |

50ns |

20ns |

20ns |

20ns |

10ns |

10ns |

10ns |

|

|

||||||||

100MHz (12.0ns) |

3 |

7 |

5 |

2 |

2 |

2 |

1 |

1 |

1 |

83MHz (12.0ns) |

2 |

6 |

5 |

2 |

2 |

2 |

1 |

1 |

1 |

REFRESH CYCLE PARAMETERS

|

|

|

-10 |

|

-12 |

|

||

Parameter |

Symbol |

Min |

|

Max |

Min |

|

Max |

Units |

Refresh Period (1,2) |

tREF |

— |

|

64 |

— |

|

64 |

ms |

|

|

|

|

|

|

|

|

|

NOTES:

1.4096 cycles

2.Any time that the Refresh Period has been exceeded, a minimum of two Auto (CBR) Refresh commands must be given to "wake-up" the device.

SDRAM COMMAND TRUTH TABLE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Function |

|

SDCE |

SDRAS |

|

SDCAS |

SDWE |

BWE |

A12, A13 |

SDA10 |

Notes |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A11-0 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Mode Register Set |

|

L |

|

L |

|

L |

|

L |

X |

OP CODE |

|

||||||

Auto Refresh (CBR) |

|

L |

|

L |

|

L |

|

H |

X |

X |

X |

|

|||||

Precharge |

Single Bank |

|

L |

|

L |

|

H |

|

L |

X |

BA |

L |

2 |

||||

Precharge all Banks |

|

L |

|

L |

|

H |

|

L |

X |

X |

H |

|

|||||

|

|

|

|

|

|

||||||||||||

Bank Activate |

|

L |

|

L |

|

H |

|

H |

X |

BA |

Row Address |

2 |

|||||

Write |

|

L |

|

H |

|

L |

|

L |

X |

BA |

L |

2 |

|||||

Write with Auto Precharge |

|

L |

|

H |

|

L |

|

L |

X |

BA |

H |

2 |

|||||

Read |

|

L |

|

H |

|

L |

|

L |

X |

BA |

L |

2 |

|||||

Read with Auto Precharge |

|

L |

|

H |

|

L |

|

H |

X |

BA |

H |

2 |

|||||

Burst Termination |

|

L |

|

H |

|

H |

|

L |

X |

X |

X |

3 |

|||||

No Operation |

|

L |

|

H |

|

H |

|

H |

X |

X |

X |

|

|||||

Device Deselect |

|

H |

|

X |

|

X |

|

X |

X |

X |

X |

|

|||||

Data Write/Output Disable |

|

X |

|

X |

|

X |

|

X |

L |

X |

X |

4 |

|||||

Data Mask/Output Disable |

|

X |

|

X |

|

X |

|

X |

H |

X |

X |

4 |

|||||

NOTES:

1.All of the SDRAM operations are defined by states of SDCE\, SDWE\, SDRAS\, SDCAS\, and BWE0-3 at the positive rising edge of the clock.

2.Bank Select (BA), if A12 (BA0) and A13 (BA1) select between different banks.

3.During a Burst Write cycle there is a zero clock delay, for a Burst Read cycle the delay is equal to the CAS latency.

4.The BWE has two functions for the data DQ Read and Write operations. During a Read cycle, when BWE goes high at a clock timing the data outputs are disabled and become high impedance after a two clock delay. BWE also provides a data mask function for Write cycles. When it activates, the Write operation at the clock is prohibited (zero clock latency).

January 20001 |

9 |

White Electronic Designs Corporation • (508) 366-5151 • www.whiteedc.com |

Loading...

Loading...