White Electronic Designs WS512K32NV-70HM, WS512K32NV-70HIA, WS512K32NV-70HI, WS512K32NV-70HC, WS512K32NV-70HCA Datasheet

...

WS512K32V-XXX

HI-RELIABILITY PRODUCT

512Kx32 SRAM 3.3V MODULE ADVANCED*

FEATURES

■Access Times of 70, 85, 100, 120ns

■Packaging

¥66-pin, PGA Type, 1.185 inch square, Hermetic Ceramic HIP (Package 401)

¥68 lead, Hermetic CQFP (G2T), 22.4mm (0.880 inch) square 4.57mm (0.180 inch) high (Package 509). Designed to fit JEDEC 68 lead 0.990" CQFJ footprint.

■Organized as 512Kx32, User Configurable as 1024Kx16 or 2Mx8

■Commercial, Industrial and Military Temperature Ranges

■TTL Compatible Inputs and Outputs

■Low Voltage

¥ 3.3V ±10% Power Supply

■Low Power CMOS

■Built-in Decoupling Caps and Multiple Ground Pins for Low Noise Operation

■Weight

WS512K32V-XG2TX - 8 grams typical WS512K32V-XHX - 13 grams typical

*This data sheet describes a product that may or may not be under development and is subject to change or cancellation without notice.

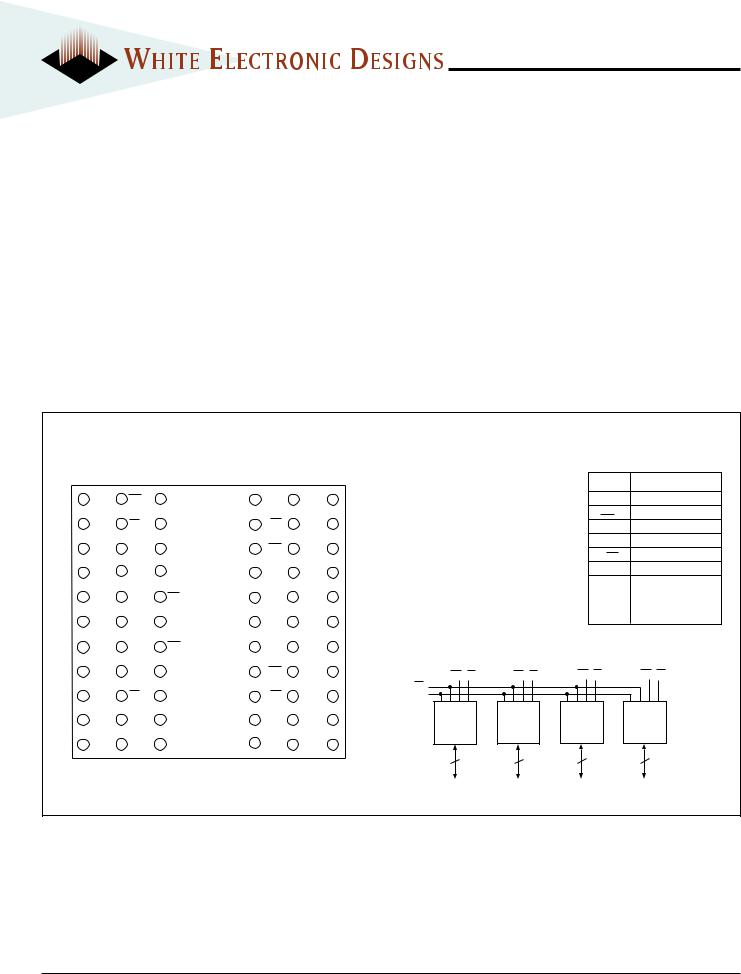

FIG. 1 PIN CONFIGURATION FOR WS512K32V-XHX |

|

|

|

|||||||

|

|

TOP VIEW |

|

|

|

|

|

PIN DESCRIPTION |

||

1 |

12 |

23 |

|

34 |

45 |

|

56 |

|

I/O0-31 |

Data Inputs/Outputs |

|

|

|

|

|

|

|

|

|

||

I/O8 |

WE2 |

I/O15 |

I/O24 |

|

VCC |

I/O31 |

|

|

A0-18 |

Address Inputs |

|

|

|

WE1-4 Write Enables |

|||||||

|

|

|

|

|

|

|

|

|

||

I/O9 |

CS2 |

I/O14 |

I/O25 |

|

CS4 |

I/O30 |

|

|

CS1-4 |

Chip Selects |

I/O10 |

GND |

I/O13 |

I/O26 |

|

WE4 |

I/O29 |

|

|

OE |

Output Enable |

|

|

|

VCC |

Power Supply |

||||||

A13 |

I/O11 |

I/O12 |

A6 |

|

I/O27 |

I/O28 |

|

|

GND |

Ground |

|

|

|

NC |

Not Connected |

||||||

|

|

|

|

|

|

|

|

|

||

A14 |

A10 |

OE |

A7 |

|

A3 |

A0 |

|

|

|

|

A15 |

A11 |

A18 |

NC |

|

A4 |

A1 |

|

|

|

|

A16 |

A12 |

WE1 |

A8 |

|

A5 |

A2 |

BLOCK DIAGRAM |

|

||

|

|

|

|

|

|

|

|

|||

A17 |

VCC |

I/O7 |

A9 |

|

WE3 |

I/O23 |

WE1 CS1 |

WE2 CS2 |

WE3 CS3 |

WE4 CS4 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

OE |

|

|

|

I/O0 |

CS1 |

I/O6 |

I/O16 |

|

CS3 |

I/O22 |

A 0 - 18 |

|

|

|

I/O1 |

NC |

I/O5 |

I/O17 |

|

GND |

I/O21 |

512K x 8 |

512K x 8 |

512K x 8 |

512K x 8 |

I/O2 |

I/O3 |

I/O4 |

I/O18 |

|

I/O19 |

I/O20 |

|

|

|

|

11 |

22 |

33 |

|

44 |

55 |

|

8 |

8 |

8 |

8 |

|

|

66 |

|

|

|

|||||

|

|

|

|

|

|

|

I/O 0 - 7 |

I/O 8 - 15 |

I/O 16 - 23 |

I/O 24 - 31 |

February 2000 Rev. 2 |

1 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

WS512K32V-XXX

FIG. 2 PIN CONFIGURATION FOR WS512K32V-XG2TX

TOP VIEW

|

NC |

A0 |

A1 |

A2 |

A3 |

A4 |

A5 |

|

|

CS3 |

|

GND |

|

CS4 |

|

WE1 A6 A7 |

|

A8 |

A9 |

A10 |

VCC |

|

||||

|

|

|

|

|

|

|||||||||||||||||||||

|

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

68 67 66 65 64 63 62 61 |

|

|||||||||||||||

I/O0 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

60 |

I/O16 |

I/O1 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

59 |

I/O17 |

I/O2 |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

58 |

I/O18 |

I/O3 |

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

I/O19 |

I/O4 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

56 |

I/O20 |

I/O5 |

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

55 |

I/O21 |

I/O6 |

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

54 |

I/O22 |

I/O7 |

17 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

53 |

I/O23 |

GND |

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

52 |

GND |

I/O8 |

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

51 |

I/O24 |

I/O9 |

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

50 |

I/O25 |

I/O10 |

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

49 |

I/O26 |

I/O11 |

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

I/O27 |

I/O12 |

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

I/O28 |

I/O13 |

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

I/O29 |

I/O14 |

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

I/O30 |

I/O15 |

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

I/O31 |

|

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 |

|

||||||||||||||||||||||||

|

VCC |

A11 |

A12 |

A13 |

A14 |

A15 |

A16 |

|

|

CS1 |

|

OE |

|

CS2 |

|

A17 |

|

WE2 |

|

WE3 |

|

WE4 |

A18 |

NC |

NC |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

0.940"

The WEDC 68 lead G2T CQFP fills the same fit and function as the JEDEC 68 lead CQFJ or 68 PLCC. But the G2T has the TCE and lead inspection advantage of the CQFP form.

WE1 CS1

OE

A 0 - 18

PIN DESCRIPTION

I/O0-31 |

Data Inputs/Outputs |

|||||

|

|

|

|

|

|

|

|

|

A0-18 |

Address Inputs |

|||

|

WE |

1-4 |

Write Enables |

|

||

|

|

|

|

|

|

|

|

CS1-4 |

Chip Selects |

||||

|

|

OE |

Output Enable |

|

||

|

|

VCC |

Power Supply |

|

||

|

|

GND |

Ground |

|

||

|

|

NC |

Not Connected |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WE2 CS2 |

WE3 CS3 |

WE4 CS4 |

|||||||||

512K x 8 |

|

512K x 8 |

|

512K x 8 |

|

512K x 8 |

|

|

|

|

|

|

|

8 |

8 |

8 |

8 |

|||

I/O 0 - 7 |

|

I/O 8 - 15 |

|

I/O 16 - 23 |

|

I/O 24 - 31 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

2 |

WS512K32V-XXX

ABSOLUTE MAXIMUM RATINGS

Parameter |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

Operating Temperature |

TA |

-55 |

+125 |

°C |

|

|

|

|

|

Storage Temperature |

TSTG |

-65 |

+150 |

°C |

|

|

|

|

|

Signal Voltage Relative to GND |

VG |

-0.5 |

Vcc+0.5 |

V |

|

|

|

|

|

Junction Temperature |

TJ |

|

150 |

°C |

|

|

|

|

|

Supply Voltage |

VCC |

-0.5 |

4.0 |

V |

|

|

|

|

|

RECOMMENDED OPERATING CONDITIONS

Parameter |

Symbol |

Min |

Max |

Unit |

|

|

|

|

|

Supply Voltage |

VCC |

3.0 |

3.6 |

V |

|

|

|

|

|

Input High Voltage |

VIH |

2.2 |

VCC + 0.3 |

V |

|

|

|

|

|

Input Low Voltage |

VIL |

-0.5 |

+0.8 |

V |

|

|

|

|

|

Operating Temp (Mil) |

TA |

-55 |

+125 |

°C |

|

|

|

|

|

TRUTH TABLE

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

OE |

|

|

WE |

|

Mode |

Data I/O |

Power |

|||||

|

H |

|

X |

|

|

X |

|

Standby |

High Z |

Standby |

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

|

L |

|

L |

|

|

H |

|

Read |

Data Out |

Active |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

L |

|

H |

|

|

H |

|

Out Disable |

High Z |

Active |

|

||

|

L |

|

X |

|

|

L |

|

Write |

Data In |

Active |

|||

CAPACITANCE

(TA = +25°C)

|

Parameter |

Symbol |

Conditions |

Max |

Unit |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Capacitance |

COE |

VIN = 0 V, f = 1.0 MHz |

50 |

pF |

|

OE |

|

|||||||

|

|

|

|

|

Capacitance |

CWE |

VIN = 0 V, f = 1.0 MHz |

|

pF |

|

WE |

|

|||||||

|

|

|

|

|

HIP (PGA) |

|

|

20 |

|

|

|

|

|

|

CQFP G2T |

|

|

15 |

|

|

|

CCS |

VIN = 0 V, f = 1.0 MHz |

20 |

pF |

||||

|

|

CS |

Capacitance |

||||||

|

Data I/O Capacitance |

CI/O |

VI/O = 0 V, f = 1.0 MHz |

20 |

pF |

||||

|

Address Input Capacitance |

CAD |

VIN = 0 V, f = 1.0 MHz |

50 |

pF |

||||

This parameter is guaranteed by design but not tested.

DC CHARACTERISTICS

(VCC = 3.3V, VSS = 0V, TA = -55°C to +125°C)

Parameter |

Symbol |

|

|

|

|

|

|

|

|

|

|

Conditions |

Min |

Max |

Units |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Input Leakage Current |

ILI |

|

VCC = 3.6, VIN = GND to VCC |

|

10 |

A |

|||||||||

Output Leakage Current |

ILO |

|

|

|

|

= VIH, |

|

|

|

= VIH, VOUT = GND to VCC |

|

10 |

A |

||

CS |

|

OE |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Operating Supply Current x 32 Mode |

ICC x 32 |

|

CS |

= VIL, |

|

OE |

|

= VIH, f = 5MHz, Vcc = 3.6 |

|

100 |

mA |

||||

|

|

|

|

|

|

|

|

|

|||||||

Standby Current |

ISB |

|

|

CS |

= VIH, |

OE |

= VIH, f = 5MHz, Vcc = 3.6 |

|

2.0 |

mA |

|||||

Output Low Voltage |

VOL |

|

IOL = 2.1mA, VCC = 3.0 |

|

0.4 |

V |

|||||||||

Output High Voltage |

VOH |

|

IOH = -1.0mA, VCC = 3.0 |

2.4 |

|

V |

|||||||||

NOTE: DC test conditions: VIH = VCC -0.3V, VIL = 0.3V

3 |

White Electronic Designs Corporation • (602) 437-1520 • www.whiteedc.com |

Loading...

Loading...