Texas Instruments CD4051BPWR, CD4051BPW, CD4051BNSR, CD4051BM96, CD4051BM Datasheet

...

CD4051B, CD4052B, CD4053B

Data sheet acquired from Harris Semiconductor SCHS047D

August 1998 - Revised March 2000

|

CMOS Analog Multiplexers/Demultiplexers |

|

|

with Logic Level Conversion |

|

|

The CD4051B, CD4052B, and CD4053B analog multiplexers |

|

|

are digitally-controlled analog switches having low ON |

|

[ /Title |

impedance and very low OFF leakage current. Control of |

|

analog signals up to 20VP-P can be achieved by digital |

||

(CD405 |

||

signal amplitudes of 4.5V to 20V (if VDD -VSS = 3V, a |

||

1B, |

VDD -VEE of up to 13V can be controlled; for VDD -VEE level |

|

CD4052 |

||

differences above 13V, a VDD -VSS of at least 4.5V is |

||

B, |

required). For example, if VDD = +4.5V, VSS = 0V, and |

|

CD4053 |

VEE = -13.5V, analog signals from -13.5V to +4.5V can be |

B)controlled by digital inputs of 0V to 5V. These multiplexer

/Sub- |

circuits dissipate extremely low quiescent power over the |

|||

full VDD -VSS and VDD -VEE supply-voltage ranges, |

||||

ject |

||||

independent of the logic state of the control signals. When |

||||

(CMOS |

a logic “1” is present at the inhibit input terminal, all |

|||

Analog |

channels are off. |

|

|

|

Multi- |

The CD4051B is a single 8-Channel multiplexer having three |

|||

plex- |

binary control inputs, A, B, and C, and an inhibit input. The |

|||

ers/Dem |

three binary signals select 1 of 8 channels to be turned on, |

|||

ultiplex- |

and connect one of the 8 inputs to the output. |

|||

ers with |

The CD4052B is a differential 4-Channel multiplexer having |

|||

Logic |

two binary control inputs, A and B, and an inhibit input. The |

|||

Level |

two binary input signals select 1 of 4 pairs of channels to be |

|||

Conver- |

turned on and connect the analog inputs to the outputs. |

|||

sion) |

The CD4053B is a triple 2-Channel multiplexer having three |

|||

/Author |

separate digital control inputs, A, B, and C, and an inhibit |

|||

() |

input. Each control input selects one of a pair of channels |

|||

which are connected in a single-pole, double-throw |

||||

/Key- |

||||

configuration. |

|

|

||

words |

|

|

||

When these devices are used as demultiplexers, the |

||||

(Harris |

||||

“CHANNEL IN/OUT” terminals are the outputs and the |

||||

Semi- |

||||

“COMMON OUT/IN” terminals are the inputs. |

||||

conduc- |

||||

|

|

|

||

tor, |

Ordering Information |

|

||

CD4000 |

|

|||

|

|

TEMP. RANGE |

|

|

|

PART NUMBER |

(oC) |

PACKAGE |

|

|

CD4051BF, CD4052BF, |

-55 to 125 |

16 Ld CERAMIC |

|

|

CD4053BF |

|

DIP |

|

|

|

|

|

|

|

CD4051BE, CD4052BE, |

-55 to 125 |

16 Ld PDIP |

|

|

CD4053BE |

|

|

|

|

|

|

|

|

|

CD4051BM, CD4051BNS |

-55 to 125 |

16 Ld SOIC |

|

|

|

|

|

|

|

CD4051BPW, CD4052BPW, |

-55 to 125 |

16 Ld TSSOP |

|

|

CD4053BPW |

|

|

|

|

|

|

|

|

Features

•Wide Range of Digital and Analog Signal Levels

-Digital . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3V to 20V

-Analog. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ≤20VP-P

•Low ON Resistance, 125Ω (Typ) Over 15VP-P Signal Input Range for VDD-VEE = 18V

•High OFF Resistance, Channel Leakage of ±100pA (Typ) at VDD-VEE = 18V

•Logic-Level Conversion for Digital Addressing Signals of

3V to 20V (VDD-VSS = 3V to 20V) to Switch Analog Signals to 20VP-P (VDD-VEE = 20V)

•Matched Switch Characteristics, rON = 5Ω (Typ) for VDD-VEE = 15V

•Very Low Quiescent Power Dissipation Under All DigitalControl Input and Supply Conditions, 0.2µW (Typ) at VDD-VSS = VDD-VEE = 10V

•Binary Address Decoding on Chip

•5V, 10V and 15V Parametric Ratings

•10% Tested for Quiescent Current at 20V

•Maximum Input Current of 1µA at 18V Over Full Package Temperature Range, 100nA at 18V and 25oC

•Break-Before-Make Switching Eliminates Channel Overlap

Applications

•Analog and Digital Multiplexing and Demultiplexing

•A/D and D/A Conversion

•Signal Gating

1 |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. |

|

Copyright © 2000, Texas Instruments Incorporated |

|

CD4051B, CD4052B, CD4053B

Pinouts

CD4051B (PDIP, CDIP, SOIC, TSSOP) |

|

|

|

CD4052B (PDIP, CDIP, TSSOP) |

||||||||

|

|

|

TOP VIEW |

|

|

|

|

|

|

TOP VIEW |

|

|

CHANNELS |

4 |

1 |

16 |

VDD |

|

|

Y CHANNELS |

0 |

1 |

16 |

VDD |

|

IN/OUT |

6 |

2 |

15 |

2 |

|

|

IN/OUT |

2 |

2 |

15 |

2 |

X CHANNELS |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

COM OUT/IN |

3 |

14 |

1 |

|

COMMON “Y” OUT/IN |

3 |

14 |

1 |

IN/OUT |

|||

|

|

|||||||||||

|

|

|

|

CHANNELS IN/OUT |

|

|

|

|

|

|

|

|

CHANNELS |

7 |

4 |

13 |

0 |

|

|

Y CHANNELS |

3 |

4 |

13 |

COMMON “X” OUT/IN |

|

IN/OUT |

5 |

5 |

12 |

3 |

|

|

IN/OUT |

1 |

5 |

12 |

0 |

X CHANNELS |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INH |

6 |

11 |

A |

|

|

|

INH |

6 |

11 |

3 |

IN/OUT |

|

|

|

|

|

||||||||

|

VEE |

7 |

10 |

B |

|

|

|

VEE |

7 |

10 |

A |

|

|

VSS |

8 |

9 |

C |

|

|

|

VSS |

8 |

9 |

B |

|

|

|

|

|

CD4053B (PDIP, CDIP, TSSOP) |

|

|

|

|

|

|||

|

|

|

|

|

|

TOP VIEW |

|

|

|

|

|

|

|

|

|

|

by |

1 |

16 |

VDD |

|

|

|

|

|

|

|

|

|

IN/OUT bx |

2 |

15 |

OUT/IN bx OR by |

|

|

|

|

|

|

|

|

|

cy |

3 |

14 |

OUT/IN ax OR ay |

|

|

|

|

|

|

|

|

|

OUT/IN CX OR CY |

4 |

13 |

ay |

|

|

|

|

|

|

|

|

|

IN/OUT CX |

5 |

12 |

IN/OUT |

|

|

|

|

|

|

|

|

|

ax |

|

|

|

|

|

|||

|

|

|

|

INH |

6 |

11 |

A |

|

|

|

|

|

|

|

|

|

VEE |

7 |

10 |

B |

|

|

|

|

|

|

|

|

|

VSS |

8 |

9 |

C |

|

|

|

|

|

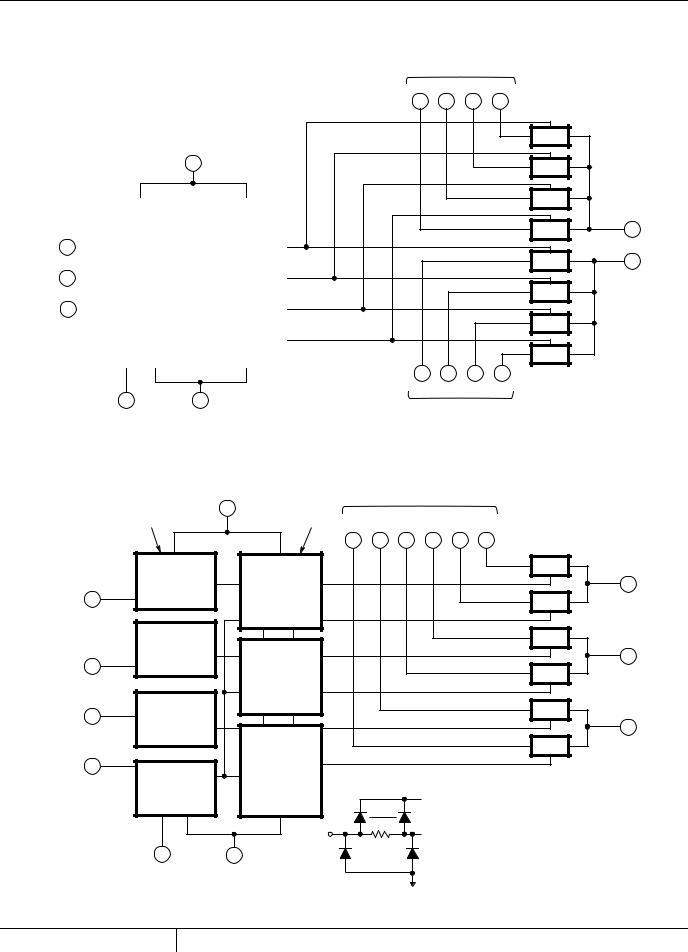

Functional Block Diagrams

CD4051B

|

|

|

CHANNEL IN/OUT |

|

|

|||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

16 VDD |

4 |

2 |

5 |

1 |

12 |

15 |

14 |

13 |

A † |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

B † |

10 |

|

|

|

|

|

|

|

BINARY |

|

|

|

|

|

|

|

|

||||

|

|

|

LOGIC |

|

|

|

TO |

|||

|

|

|

|

|

|

1 OF 8 |

||||

|

|

|

LEVEL |

|

|

|

||||

|

|

|

|

|

|

DECODER |

||||

|

|

|

CONVERSION |

|

|

|

||||

C † |

|

|

|

|

|

WITH |

||||

9 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

INHIBIT |

|||

|

|

|

|

|

|

|

||||

INH † |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TG |

TG |

TG |

TG |

COMMON |

OUT/IN |

|

|

3 |

TG |

TG |

TG |

TG |

8 VSS |

7 VEE |

† All inputs are protected by standard CMOS protection network.

2

CD4051B, CD4052B, CD4053B

Functional Block Diagrams (Continued)

CD4052B

X CHANNELS IN/OUT 3 2 1 0 11 15 14 12

16 VDD

A † |

10 |

|

|

|

|

|

BINARY |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC |

|

TO |

B † |

9 |

|

|

|

|

1 OF 4 |

|

|

|

|

LEVEL |

|

|||

|

|

||||||

|

|

|

|

|

CONVERSION |

|

DECODER |

|

|

|

|

|

|

WITH |

|

INH † |

6 |

|

|

|

|

|

|

|

|

|

|

|

INHIBIT |

||

|

|

|

|

||||

|

|

|

|

|

|

|

|

8 VSS |

7 VEE |

TG |

TG |

|

TG |

COMMON X |

|

|

|

OUT/IN |

TG |

13 |

TG |

3 |

|

COMMON Y |

TG |

OUT/IN |

|

TG |

TG |

1 |

5 |

2 |

4 |

0 |

1 |

2 |

3 |

Y CHANNELS IN/OUT

|

|

|

CD4053B |

|

|

|

|

|

|

|

|

|

|

BINARY TO |

|

|

|

|

|

|

|

|

LOGIC |

|

1 OF 2 |

|

|

IN/OUT |

|

|

|

|

|

16 VDD |

DECODERS |

|

|

|

|

|

|

|

|

|

LEVEL |

WITH |

cy |

cx |

by |

bx |

ay |

ax |

|

|

|

CONVERSION |

|

INHIBIT |

|

||||||

|

|

|

|

3 |

5 |

1 |

2 |

13 |

12 |

COMMON |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT/IN |

|

|

|

|

|

|

|

|

|

TG |

ax OR ay |

|

|

|

|

|

|

|

|

|

|

14 |

A † |

11 |

|

|

|

|

|

|

|

TG |

|

|

|

|

|

|

|

|

|

|

|

COMMON |

|

|

|

|

|

|

|

|

|

TG |

OUT/IN |

|

|

|

|

|

|

|

|

|

bx OR by |

|

B † |

10 |

|

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

TG |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COMMON |

|

|

|

|

|

|

|

|

|

TG |

OUT/IN |

C † |

9 |

|

|

|

|

|

|

|

cx OR cy |

|

|

|

|

|

|

|

|

|

4 |

||

|

|

|

|

|

|

|

|

|

|

|

TG |

INH † 6

VDD

8 VSS |

7 VEE |

† All inputs are protected by standard CMOS protection network.

3

CD4051B, CD4052B, CD4053B

TRUTH TABLES

|

INPUT STATES |

|

|

||||

|

|

|

|

|

|

|

|

INHIBIT |

|

C |

|

B |

|

A |

“ON” CHANNEL(S) |

|

|

|

|

|

|

|

|

CD4051B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

|

0 |

0 |

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

|

1 |

1 |

|

|

|

|

|

|

|

|

0 |

|

0 |

|

1 |

|

0 |

2 |

|

|

|

|

|

|

|

|

0 |

|

0 |

|

1 |

|

1 |

3 |

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

|

0 |

4 |

|

|

|

|

|

|

|

|

0 |

|

1 |

|

0 |

|

1 |

5 |

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

|

0 |

6 |

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

|

1 |

7 |

|

|

|

|

|

|

|

|

1 |

|

X |

|

X |

|

X |

None |

|

|

|

|

|

|

|

|

CD4052B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INHIBIT |

|

|

B |

|

A |

|

|

|

|

|

|

|

|

|

|

0 |

|

|

0 |

|

0 |

0x, 0y |

|

|

|

|

|

|

|

|

|

0 |

|

|

0 |

|

1 |

1x, 1y |

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

|

0 |

2x, 2y |

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

|

1 |

3x, 3y |

|

|

|

|

|

|

|

|

|

1 |

|

|

X |

|

X |

None |

|

|

|

|

|

|

|

|

|

CD4053B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INHIBIT |

|

|

A OR B OR C |

|

|

||

|

|

|

|

|

|

|

|

0 |

|

|

0 |

|

|

ax or bx or cx |

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

|

|

ay or by or cy |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

X |

|

None |

|

|

|

|

|

|

|

|

|

X = Don’t Care

4

Loading...

Loading...