NSC 5962R8853401VFA, 5962R8853401VEA, 5962R8853401V2A, 5962R8853401FA, 5962R8853401EA Datasheet

...

August 1998

54AC109 · 54ACT109

Dual JK Positive Edge-Triggered Flip-Flop

General Description

The 'AC/'ACT109 consists of two high-speed completely independent transition clocked JK flip-flops. The clocking operation is independent of rise and fall times of the clock waveform. The JK design allows operation as a D flip-flop (refer to 'AC/'ACT74 data sheet) by connecting the J and K inputs together.

Asynchronous Inputs:

LOW input to SD (Set) sets Q to HIGH level

LOW input to CD (Clear) sets Q to LOW level Clear and Set are independent of clock

Simultaneous LOW on CD and SD makes both Q and Q HIGH

Features

nICC reduced by 50%

nOutputs source/sink 24 mA

n'ACT109 has TTL-compatible inputs

nStandard Military Drawing (SMD)

Ð'AC109: 5962-89551

Ð'ACT109: 5962-88534

Logic Symbol

IEEE/IEC

DS100267-1

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DS100267-7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin Names |

Description |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

J1, J2, |

K |

1, |

K |

2 |

|

Data Inputs |

|

|||||||||

|

CP1, CP2 |

Clock Pulse Inputs |

|

||||||||||||||

|

|

|

|

|

|

D2 |

Direct Clear Inputs |

|

|||||||||

|

C |

D1, |

C |

|

|||||||||||||

|

|

|

D2 |

Direct Set Inputs |

|

||||||||||||

|

S |

D1, |

S |

|

|||||||||||||

|

Q1, Q2, |

Q |

1, |

Q |

2 |

Outputs |

|

||||||||||

DS100267-2

FACT® is a registered trademark of Fairchild Semiconductor Corporation.

Flop-Flip Triggered-Edge Positive JK Dual 54ACT109 · 54AC109

© 1998 National Semiconductor Corporation |

DS100267 |

www.national.com |

Connection Diagrams

Pin Assignment for DIP and Flatpak

DS100267-3

Truth Table

(each half)

|

|

|

|

|

|

Inputs |

|

|

|

|

Outputs |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

D |

|

C |

D |

CP |

J |

|

K |

|

Q |

|

Q |

|

|

|

L |

|

H |

X |

X |

|

X |

H |

|

L |

|||||

|

H |

|

L |

X |

X |

|

X |

L |

|

H |

|||||

|

L |

|

L |

X |

X |

|

X |

H |

|

H |

|||||

|

H |

|

H |

N |

L |

|

L |

L |

|

H |

|||||

|

H |

|

H |

N |

H |

|

L |

Toggle |

|||||||

|

H |

|

H |

N |

|

|

|

|

|

|

|

|

|

||

|

|

L |

|

H |

Q0 |

Q0 |

|||||||||

|

|

|

|

||||||||||||

|

H |

|

H |

N |

H |

|

H |

H |

|

L |

|||||

|

H |

|

H |

L |

X |

|

X |

Q0 |

|

||||||

|

|

|

Q |

0 |

|||||||||||

H = HIGH Voltage Level

L = LOW Voltage Level

N = LOW-to-HIGH Transition

X = Immaterial

Q0(Q0) = Previous Q0 (Q0) before LOW-to-HIGH Transition of Clock

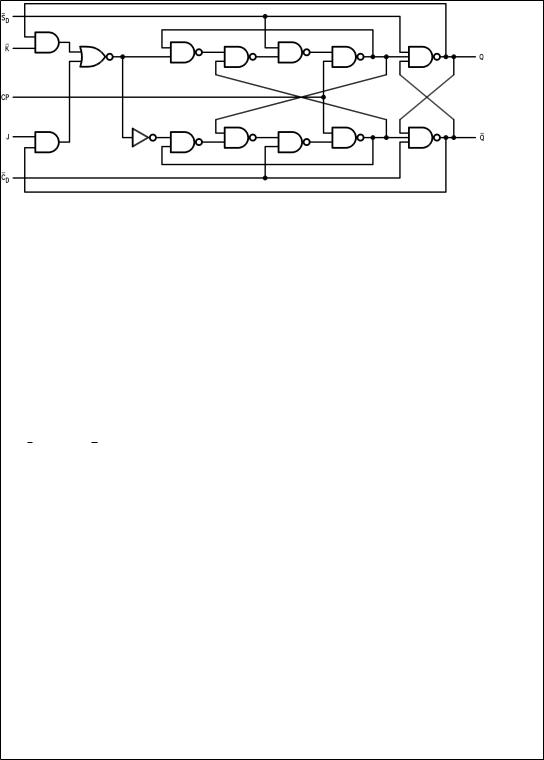

Logic Diagram (one half shown)

Pin Assignment

for LCC

DS100267-4

DS100267-5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.national.com |

2 |

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage (VCC) |

−0.5V to +7.0V |

DC Input Diode Current (IIK) |

|

VI = −0.5V |

−20 mA |

VI = VCC + 0.5V |

+20 mA |

DC Input Voltage (VI) |

−0.5V to V CC + 0.5V |

DC Output Diode Current (IOK) |

|

VO = −0.5V |

−20 mA |

VO = VCC + 0.5V |

+20 mA |

DC Output Voltage (VO) |

−0.5V to V CC + 0.5V |

DC Output Source |

|

or Sink Current (IO) |

±50 mA |

DC VCC or Ground Current |

|

per Output Pin (ICC or IGND) |

±50 mA |

Storage Temperature (TSTG) |

−65ÊC to +150ÊC |

Junction Temperature (TJ) |

|

CDIP |

175ÊC |

Recommended Operating

Conditions

Supply Voltage (VCC) |

|

|

'AC |

|

2.0V to 6.0V |

'ACT |

|

4.5V to 5.5V |

Input Voltage (VI) |

|

0V to VCC |

Output Voltage (VO) |

|

0V to VCC |

Operating Temperature (TA) |

|

|

54AC/ACT |

|

−55ÊC to +125ÊC |

Minimum Input Edge Rate ( |

V/ |

t) |

'AC Devices |

|

|

VIN from 30% to 70% of VCC |

|

|

VCC @ 3.3V, 4.5V, 5.5V |

|

125 mV/ns |

Minimum Input Edge Rate ( |

V/ |

t) |

'ACT Devices |

|

|

VIN from 0.8V to 2.0V |

|

|

VCC @ 4.5V, 5.5V |

|

125 mV/ns |

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. National does not recommend operation of FACT® circuits outside databook specifications.

DC Characteristics for 'AC Family Devices

|

|

|

54AC |

|

|

|

|

|

|

|

|

Symbol |

Parameter |

VCC |

TA = −55ÊC to +125ÊC |

Units |

Conditions |

|

|

(V) |

Guaranteed Limits |

|

|

|

|

|

|

|

|

VIH |

Minimum High Level |

3.0 |

2.1 |

|

VOUT = 0.1V |

|

Input Voltage |

4.5 |

3.15 |

V |

or VCC − 0.1V |

|

|

5.5 |

3.85 |

|

|

|

|

|

|

|

|

VIL |

Maximum Low Level |

3.0 |

0.9 |

|

VOUT = 0.1V |

|

Input Voltage |

4.5 |

1.35 |

V |

or VCC − 0.1V |

|

|

5.5 |

1.65 |

|

|

|

|

|

|

|

|

VOH |

Minimum High Level |

3.0 |

2.9 |

|

IOUT = −50 µA |

|

Output Voltage |

4.5 |

4.4 |

V |

|

|

|

5.5 |

5.4 |

|

|

|

|

|

|

|

(Note 2) |

|

|

|

|

|

VIN = VIL or VIH |

|

|

3.0 |

2.4 |

|

IOH = −12 mA |

|

|

4.5 |

3.7 |

V |

IOH = −24 mA |

|

|

5.5 |

4.7 |

|

IOH = −24 mA |

VOL |

Maximum Low Level |

3.0 |

0.1 |

|

IOUT = 50 µA |

|

Output Voltage |

4.5 |

0.1 |

V |

|

|

|

5.5 |

0.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

(Note 2) |

|

|

|

|

|

VIN = VIL or VIH |

|

|

3.0 |

0.5 |

|

IOL = 12 mA |

|

|

4.5 |

0.5 |

V |

IOL = 24 mA |

|

|

5.5 |

0.5 |

|

IOL = 24 mA |

IIN |

Maximum Input |

5.5 |

±1.0 |

µA |

VI = VCC, GND |

|

Leakage Current |

|

|

|

|

|

|

|

|

|

|

|

(Note 3) |

|

|

|

|

IOLD |

Minimum Dynamic |

5.5 |

50 |

mA |

VOLD = 1.65V Max |

IOHD |

Output Current |

5.5 |

−50 |

mA |

V OHD = 3.85V Min |

|

3 |

www.national.com |

Loading...

Loading...