NSC 5962-9314101M3A, 5962-9314101MXA, 54ACT899FMQB, 54ACT899DM Datasheet

August 1998

54ACT899

9-Bit Latchable Transceiver with Parity

Generator/Checker

General Description

The ACT899 is a 9-bit to 9-bit parity transceiver with transparent latches. The device can operate as a feed-through transceiver or it can generate/check parity from the 8-bit data busses in either direction. The ACT899 features independent latch enables for the A-to-B direction and the B-to-A direction, a select pin for ODD/EVEN parity, and separate error signal output pins for checking parity.

Features

nLatchable transceiver with output sink of 24 mA

nOption to select generate parity and check or ªfeed-throughº data/parity in directions A-to-B or B-to-A

nIndependent latch enable for A-to-B and B-to-A directions

nSelect pin for ODD/EVEN parity

nERRA and ERRB output pins for parity checking

nAbility to simultaneously generate and check parity

nMay be used in system applications in place of the '280

nMay be used in system applications in place of the '657 and '373 (no need to change T/R to check parity)

n4 kV minimum ESD immunity

nStandard Microcircuit Drawing (SMD) 5962-9314101

Logic Symbol |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin Names |

|

|

Description |

||||||||||

|

|

A0±A7 |

A Bus Data Inputs/Data Outputs |

||||||||||||

|

|

B0±B7 |

B Bus Data Inputs/Data Outputs |

||||||||||||

|

|

APAR, BPAR |

A and B Bus Parity Inputs |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ODD/EVEN |

|

|

ODD/EVEN Parity Select, Active LOW |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

for EVEN Parity |

||

|

|

|

|

|

|

|

|

|

Output Enables for A or B Bus, Active |

||||||

|

|

|

GBA, |

|

GAB |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

LOW |

||

|

|

|

|

|

|

Select Pin for Feed-Through or |

|||||||||

|

|

|

SEL |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Generate Mode, LOW for Generate |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Mode |

||

|

|

LEA, LEB |

Latch Enables for A and B Latches, |

||||||||||||

|

DS100245-1 |

|

|

|

|

|

|

|

|

|

|

|

HIGH for Transparent Mode |

||

|

|

|

|

|

Error Signals for Checking Generated |

||||||||||

Connection Diagram |

|

|

ERRA, |

|

ERRB |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

Parity with Parity In, LOW if Error |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Pin Assignment for LCC |

|

|

|

|

|

|

|

|

|

|

|

|

Occurs |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DS100245-2

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

FACT® is a registered trademark of Fairchild Semiconductor Corporation.

Generator/Checker Parity with Transceiver Latchable Bit-9 54ACT899

© 1998 National Semiconductor Corporation |

DS100245 |

www.national.com |

Functional Description

The ACT899 has three principal modes of operation which are outlined below. These modes apply to both the A-to-B and B-to-A directions.

·Bus A (B) communicates to Bus B (A), parity is generated and passed on to the B (A) Bus as BPAR (APAR). If LEB (LEA) is HIGH and the Mode Select (SEL) is LOW, the parity generated from B[0:7] (A[0:7]) can be checked and monitored by ERRB (ERRA).

·Bus A (B) communicates to Bus B (A) in a feed-through mode if SEL is HIGH. Parity is still generated and checked as ERRA and ERRB in the feed-through mode (can be used as an interrupt to signal a data/parity bit error to the CPU).

·Independent Latch Enables (LEA and LEB) allow other permutations of generating/checking (see Function Table below).

Function Table

|

|

|

|

|

|

|

|

Inputs |

|

|

|

|

|

|

|

|

|

|

Operation |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GAB |

|

|

GBA |

|

|

SEL |

|

|

LEA |

LEB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

H |

|

|

|

H |

|

|

X |

X |

X |

|

Busses A and B are TRI-STATE® . |

|||||||||||||||||||||||

|

H |

|

|

|

L |

|

|

L |

L |

H |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

Generates parity from B[0:7] based on O/E |

(Note 1). Generated parity |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

→ APAR. Generated parity checked against BPAR and output as |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ERRB. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

H |

|

|

|

L |

|

|

L |

H |

H |

|

|

|

|

|

|

|

|

|

|

|

Generated parity → |

|||||||||||||

|

|

|

|

|

|

Generates parity from B[0:7] based on O/E. |

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

APAR. Generated parity checked against BPAR and output as |

ERRB. |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Generated parity also fed back through the A latch for generate/check |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

as |

ERRA. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

H |

|

|

|

L |

|

|

L |

X |

L |

|

|

|

|

|

|

|

|

|

|

|

Generated parity → |

|||||||||||||

|

|

|

|

|

|

|

Generates parity from B latch data based on O/E. |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

APAR. Generated parity checked against latched BPAR and output as |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ERRB. |

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

H |

|

|

|

L |

|

|

H |

X |

H |

BPAR/B[0:7] → APAR/A0:7] Feed-through mode. Generated parity |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

checked against BPAR and output as |

ERRB. |

|

|

|

|||||||||||||||

|

H |

|

|

|

L |

|

|

H |

H |

H |

BPAR/B[0:7] → APAR/A[0:7] |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Feed-through mode. Generated parity checked against BPAR and |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

output as |

ERRB. |

Generated parity also fed back through the A latch |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

for generate/check as |

ERRA. |

|

|

|

|

|

|||||||||||||

|

L |

|

|

|

H |

|

|

L |

H |

L |

|

|

|

Generated parity → BPAR. |

|||||||||||||||||||||

|

|

|

|

|

|

|

Generates parity for A[0:7] based on O/E. |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Generated parity checked against APAR and output as |

ERRA. |

|

|||||||||||||||||

|

L |

|

|

|

H |

|

|

L |

H |

H |

|

|

|

Generated parity → |

|||||||||||||||||||||

|

|

|

|

|

|

|

Generates parity from A[0:7] based on O/E. |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BPAR. Generated parity checked against APAR and output as |

ERRA. |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Generated parity also fed back through the B latch for generate/check |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

as |

ERRB. |

|

|||||||||||||||||

|

L |

|

|

|

H |

|

|

L |

L |

X |

|

|

|

Generated parity → |

|||||||||||||||||||||

|

|

|

|

|

|

|

Generates parity from A latch data based on O/E. |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BPAR. Generated parity checked against latched APAR and output as |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ERRA. |

|

||||||||||||||||||

|

L |

|

|

|

H |

|

|

H |

H |

L |

|

APAR/A[0:7] → BPAR/B[0:7] |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Feed-through mode. Generated parity checked against APAR and |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

output as |

ERRA. |

|

|||||||||||||||||

|

L |

|

|

|

H |

|

|

H |

H |

H |

|

APAR/A[0:7] → BPAR/B[0:7] |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Feed-through mode. Generated parity checked against APAR and |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

output as |

ERRA. |

Generated parity also fed back through the B latch |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

for generate/check as |

ERRB. |

|

|||||||||||||||||

H = HIGH Voltage Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

L = LOW Voltage Level |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

X = Immaterial |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

Note 1: O/E |

= ODD/EVEN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

www.national.com |

2 |

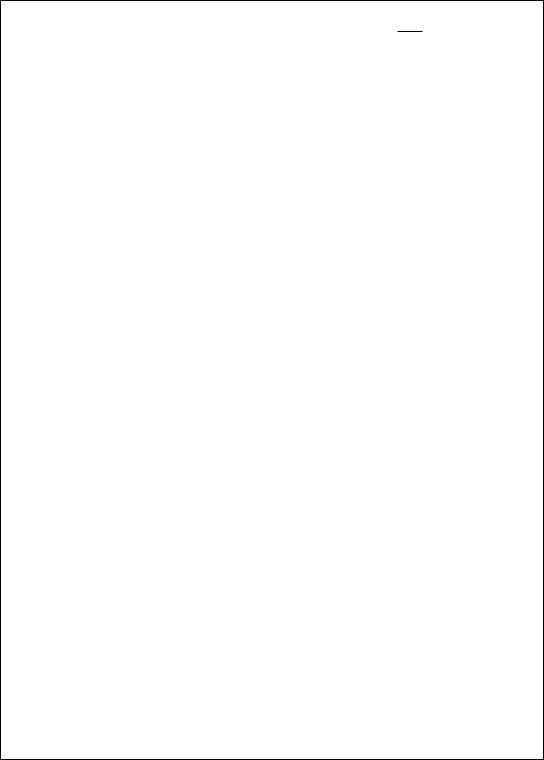

Functional Block Diagram

DS100245-3

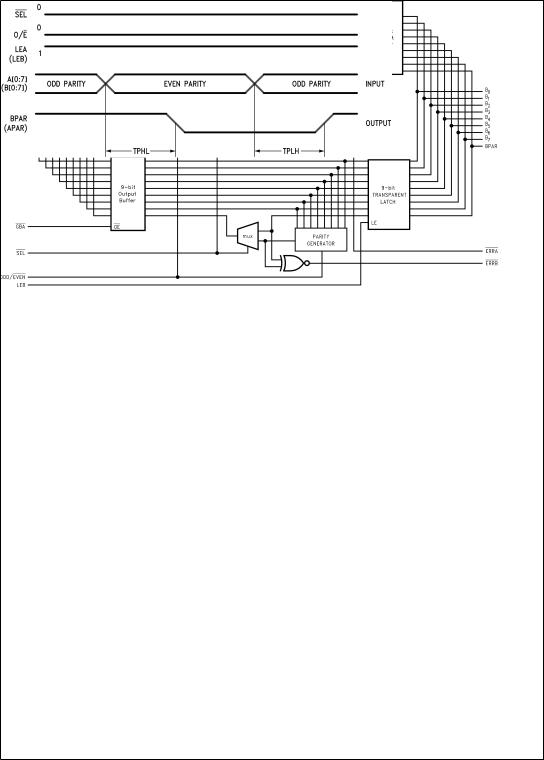

AC Path

DS100245-4

An, APAR → Bn, BPAR (Bn, BPAR → An, APAR)

FIGURE 1.

DS100245-5

An → BPAR (Bn → APAR)

FIGURE 2.

3 |

www.national.com |

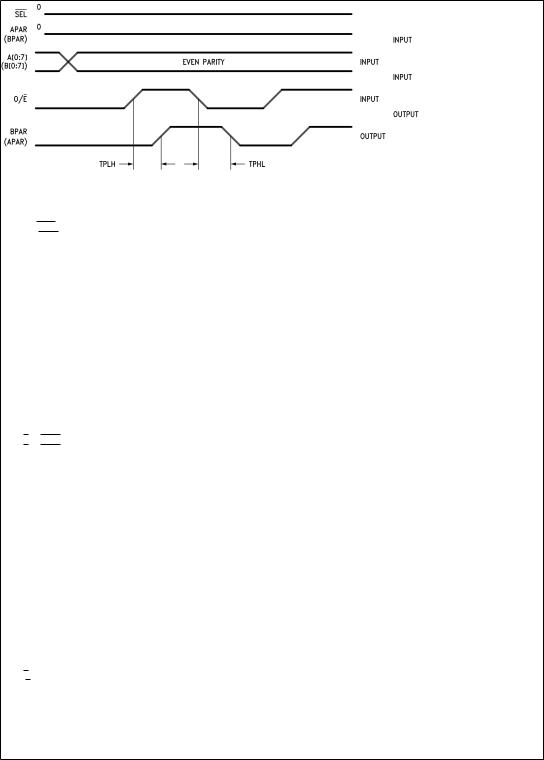

AC Path (Continued)

DS100245-6

An → ERRA (Bn → ERRB)

FIGURE 3.

DS100245-7

O/E → ERRA

O/E → ERRB

FIGURE 4.

DS100245-8

O/E → BPAR (O/E → APAR)

FIGURE 5.

www.national.com |

4 |

Loading...

Loading...