NSC ADC12H038CIWM, ADC12H034CIWM, ADC12038CIWM, ADC12034CIWM, ADC12034CIN Datasheet

...

July 1999

ADC12H030/ADC12H032/ADC12H034/ADC12H038,

ADC12030/ADC12032/ADC12034/ADC12038 Self-Calibrating 12-Bit Plus Sign Serial I/O A/D Converters with MUX and Sample/Hold

General Description

The ADC12030, and ADC12H030 families are 12-bit plus sign successive approximation A/D converters with serial I/O and configurable input multiplexers. The ADC12032/ ADC12H032, ADC12034/ADC12H034 and ADC12038/ ADC12H038 have 2, 4 and 8 channel multiplexers, respectively. The differential multiplexer outputs and A/D inputs are available on the MUXOUT1, MUXOUT2, A/DIN1 and A/DIN2 pins. The ADC12030/ADC12H030 has a two channel multiplexer with the multiplexer outputs and A/D inputs internally connected. The ADC12030 family is tested with a 5 MHz clock, while the ADC12H030 family is tested with an 8 MHz clock. On request, these A/Ds go through a self calibration process that adjusts linearity, zero and full-scale errors to less than ±1 LSB each.

The analog inputs can be configured to operate in various combinations of single-ended, differential, or pseudo-differential modes. A fully differential unipolar analog input range (0V to +5V) can be accommodated with a single +5V supply. In the differential modes, valid outputs are obtained even when the negative inputs are greater than the positive because of the 12-bit plus sign output data format.

The serial I/O is configured to comply with the NSC MICROWIRE™ . For voltage references see the LM4040 or LM4041.

Features

nSerial I/O (MICROWIRE Compatible)

n2, 4, or 8 channel differential or single-ended multiplexer

nAnalog input sample/hold function

nPower down mode

nVariable resolution and conversion rate

nProgrammable acquisition time

nVariable digital output word length and format

nNo zero or full scale adjustment required

nFully tested and guaranteed with a 4.096V reference

n0V to 5V analog input range with single 5V power supply

nNo Missing Codes over temperature

Key Specifications

n Resolution |

12-bit plus sign |

|

n 12-bit plus sign conversion time |

|

|

Ð ADC12H030 family |

5.5 |

µs (max) |

Ð ADC12030 family |

8.8 |

µs (max) |

n 12-bit plus sign throughput time |

|

|

Ð ADC12H030 family |

8.6 |

µs (max) |

Ð ADC12030 family |

14 |

µs (max) |

n Integral linearity error |

±1 LSB (max) |

|

n Single supply |

|

5V ±10% |

n Power dissipation |

33 mW (max) |

|

Ð Power down |

100 µW (typ) |

|

Applications

n Medical instruments

n Process control systems n Test equipment

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

COPS™ microcontrollers, HPC™ and MICROWIRE™ are trademarks of National Semiconductor Corporation.

ADC12030/ADC12032/ADC12034/ADC12038 ADC12H030/ADC12H032/ADC12H034/ADC12H038,

Sample/Hold and MUX with Converters A/D I/O Serial Sign Plus Bit-12 Calibrating-Self

© 1999 National Semiconductor Corporation |

DS011354 |

www.national.com |

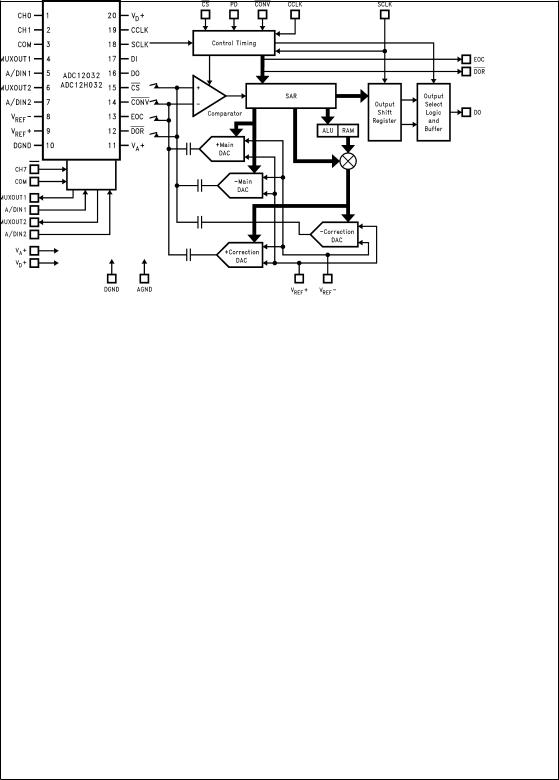

ADC12038 Simplified Block Diagram

DS011354-1

Connection Diagrams

16-Pin Wide Body |

20-Pin Wide Body |

SO Packages |

SO Packages |

DS011354-6

Top View

DS011354-7

Top View

www.national.com |

2 |

Connection Diagrams (Continued)

28-Pin Wide Body

SO Packages

24-Pin Wide Body

SO Packages

DS011354-8

DS011354-9

Top View

Top View

Ordering Information

Industrial Temperature Range |

Package |

−40ÊC ≤ TA ≤ +85ÊC |

|

ADC12H030CIWM, ADC12030CIWM |

M16B |

|

|

ADC12H032CIWM, ADC12032CIWM |

M20B |

|

|

ADC12H034CIN, ADC12034CIN |

N24C |

|

|

ADC12H034CIWM, ADC12034CIWM |

M24B |

|

|

ADC12H038CIWM, ADC12038CIWM |

M28B |

|

|

Pin Descriptions

CCLK |

The clock applied to this input controls the |

||

|

sucessive approximation conversion time |

||

|

interval and the acquisition time. The rise |

||

|

and fall times of the clock edges should not |

||

|

exceed 1 µs. |

||

SCLK |

This is the serial data clock input. The clock |

||

|

applied to this input controls the rate at |

||

|

which the serial data exchange occurs. The |

||

|

rising edge loads the information on the DI |

||

|

pin into the multiplexer address and mode |

||

|

select shift register. This address controls |

||

|

which channel of the analog input multi- |

||

|

plexer (MUX) is selected and the mode of |

||

|

operation for the A/D. With |

CS |

low the fall- |

|

ing edge of SCLK shifts the data resulting |

||

|

from the previous ADC conversion out on |

||

|

DO, with the exception of the first bit of data. |

||

|

When CS is low continously, the first bit of |

||

|

the data is clocked out on the rising edge of |

||

|

EOC (end of conversion). When CS is |

||

|

toggled the falling edge of CS always clocks |

||

|

out the first bit of data. CS should be |

||

|

brought low when SCLK is low. The rise and |

||

|

fall times of the clock edges should not ex- |

||

|

ceed 1 µs. |

||

DI |

This is the serial data input pin. The data ap- |

||

|

plied to this pin is shifted by the rising edge |

||

|

of SCLK into the multiplexer address and |

||

|

|

|

mode select register. Table 2 through Table |

||

|

|

|

5 show the assignment of the multiplexer |

||

|

|

|

address and the mode select data. |

||

DO |

The data output pin. This pin is an active |

||||

|

|

|

push/pull output when CS is low. When CS |

||

|

|

|

is high, this output is TRI-STATE. The A/D |

||

|

|

|

conversion result (D0±D12) and converter |

||

|

|

|

status data are clocked out by the falling |

||

|

|

|

edge of SCLK on this pin. The word length |

||

|

|

|

and format of this result can vary (see Table |

||

|

|

|

1). The word length and format are con- |

||

|

|

|

trolled by the data shifted into the multi- |

||

|

|

|

plexer address and mode select register |

||

|

|

|

(see Table 5). |

||

EOC |

This pin is an active push/pull output and in- |

||||

|

|

|

dicates the status of the ADC12030/2/4/8. |

||

|

|

|

When low, it signals that the A/D is busy with |

||

|

|

|

a conversion, auto-calibration, auto-zero or |

||

|

|

|

power down cycle. The rising edge of EOC |

||

|

|

|

signals the end of one of these cycles. |

||

|

This is the chip select pin. When a logic low |

||||

|

CS |

|

|||

|

|

|

is applied to this pin, the rising edge of |

||

|

|

|

SCLK shifts the data on DI into the address |

||

|

|

|

register. This low also brings DO out of |

||

|

|

|

TRI-STATE. With |

CS |

low the falling edge of |

|

|

|

SCLK shifts the data resulting from the pre- |

||

|

|

|

vious ADC conversion out on DO, with the |

||

3 |

www.national.com |

Pin Descriptions (Continued)

|

|

|

|

|

|

|

|

|

|

|

exception of the first bit of data. When CS is |

||

|

|

|

|

low continously, the first bit of the data is |

||

|

|

|

|

clocked out on the rising edge of EOC (end |

||

|

|

|

|

of conversion). When CS is toggled the fall- |

||

|

|

|

|

ing edge of CS always clocks out the first bit |

||

|

|

|

|

of data. CS should be brought low when |

||

|

|

|

|

SCLK is low. The falling edge of CS resets a |

||

|

|

|

|

conversion in progress and starts the se- |

||

|

|

|

|

quence for a new conversion. When CS is |

||

|

|

|

|

brought back low during a conversion, that |

||

|

|

|

|

conversion is prematurely terminated. The |

||

|

|

|

|

data in the output latches may be corrupted. |

||

|

|

|

|

Therefore, when CS is brought back low |

||

|

|

|

|

during a conversion in progress the data |

||

|

|

|

|

output at that time should be ignored. CS |

||

|

|

|

|

may also be left continuously low. In this |

||

|

|

|

|

case it is imperative that the correct number |

||

|

|

|

|

of SCLK pulses be applied to the ADC in or- |

||

|

|

|

|

der to remain synchronous. After the ADC |

||

|

|

|

|

supply power is applied it expects to see 13 |

||

|

|

|

|

clock pulses for each I/O sequence. The |

||

|

|

|

|

number of clock pulses the ADC expects is |

||

|

|

|

|

the same as the digital output word length. |

||

|

|

|

|

This word length can be modified by the |

||

|

|

|

|

data shifted in on the DO pin. Table 5 details |

||

|

|

|

|

the data required. |

||

|

|

This is the data output ready pin. This pin is |

||||

|

DOR |

|

|

|||

|

|

|

|

an active push/pull output. It is low when the |

||

|

|

|

|

conversion result is being shifted out and |

||

|

|

|

|

goes high to signal that all the data has |

||

|

|

|

|

been shifted out. |

||

|

|

A logic low is required on this pin to program |

||||

|

CONV |

|

||||

|

|

|

|

any mode or change the ADC's configura- |

||

|

|

|

|

tion as listed in the Mode Programming |

||

|

|

|

|

Table 5 such as 12-bit conversion, 8-bit con- |

||

|

|

|

|

version, Auto Cal, Auto Zero etc. When this |

||

|

|

|

|

pin is high the ADC is placed in the read |

||

|

|

|

|

data only mode. While in the read data only |

||

|

|

|

|

mode, bringing CS low and pulsing SCLK |

||

|

|

|

|

will only clock out on DO any data stored in |

||

|

|

|

|

the ADCs output shift register. The data on |

||

|

|

|

|

DI will be neglected. A new conversion will |

||

|

|

|

|

not be started and the ADC will remain in |

||

|

|

|

|

the mode and/or configuration previously |

||

|

|

|

|

programmed. Read data only cannot be |

||

|

|

|

|

performed while a conversion, Auto-Cal or |

||

|

|

|

|

Auto-Zero are in progress. |

||

|

PD |

This is the power down pin. When PD is |

||||

|

|

|

|

high the A/D is powered down; when PD is |

||

|

|

|

|

low the A/D is powered up. The A/D takes a |

||

|

|

|

|

maximum of 250 µs to power up after the |

||

|

|

|

|

command is given. |

||

|

CH0±CH7 |

These are the analog inputs of the MUX. A |

||||

|

|

|

|

channel input is selected by the address in- |

||

|

|

|

|

formation at the DI pin, which is loaded on |

||

|

|

|

|

the rising edge of SCLK into the address |

||

|

|

|

|

register (See Tables 2, 3, 4). |

||

|

|

|

|

The voltage applied to these inputs should |

||

|

|

|

|

not exceed VA+ or go below GND. Exceed- |

||

|

|

|

|

ing this range on an unselected channel will |

||

|

|

|

|

corrupt the reading of a selected channel. |

||

|

COM |

This pin is another analog input pin. It is |

||||

|

|

|

|

used as a pseudo ground when the analog |

||

|

|

|

|

multiplexer is single-ended. |

||

MUXOUT1, |

These are the multiplexer output |

MUXOUT2 |

pins. |

A/DIN1, /DIN2 These are the converter input pins. MUXOUT1 is usually tied to A/DIN1. MUXOUT2 is usually tied to A/DIN2. If external circuitry is placed between MUXOUT1 and A/DIN1, or MUXOUT2 and A/DIN2 it may be necessary to protect these pins. The voltage at these pins should not exceed VA+ or go below AGND (see Figure 5).

VREF+ |

This is the positive analog voltage reference |

|

input. In order to maintain accuracy, the |

|

voltage range of VREF (VREF = VREF+ − |

|

VREF−) is 1 V DC to 5.0 VDC and the voltage |

|

at VREF+ cannot exceed VA+. See Figure 6 |

|

for recommended bypassing. |

VREF− |

The negative voltage reference input. In or- |

|

der to maintain accuracy, the voltage at this |

|

pin must not go below GND or exceed VA+. |

|

(See Figure 6). |

VA+, VD+ |

These are the analog and digital power sup- |

|

ply pins. VA+ and VD+ are not connected to- |

|

gether on the chip. These pins should be |

|

tied to the same power supply and by- |

|

passed separately (see Figure 6). The oper- |

|

ating voltage range of VA+ and VD+ is |

|

4.5 VDC to 5.5 VDC. |

DGND |

This is the digital ground pin (see Figure 6). |

AGND |

This is the analog ground pin (see Figure 6). |

www.national.com |

4 |

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Positive Supply Voltage |

|

(V+ = VA+ = VD+) |

6.5V |

Voltage at Inputs and Outputs |

|

except CH0±CH7 and COM |

−0.3V to V + +0.3V |

Voltage at Analog Inputs |

|

CH0±CH7 and COM |

GND −5V to V + +5V |

|VA+ − V D+| |

300 mV |

Input Current at Any Pin (Note 3) |

±30 mA |

Package Input Current (Note 3) |

±120 mA |

Package Dissipation at |

|

TA = 25ÊC (Note 4) |

500 mW |

ESD Susceptability (Note 5) |

|

Human Body Model |

1500V |

Soldering Information |

|

N Packages (10 seconds) |

260ÊC |

SO Package (Note 6): |

|

Vapor Phase (60 seconds) |

215ÊC |

Infrared (15 seconds) |

220ÊC |

Storage Temperature |

−65ÊC to +150ÊC |

Operating Ratings (Notes 1, 2)

Operating Temperature Range |

TMIN ≤ TA ≤ TMAX |

ADC12030CIWM, |

|

ADC12H030CIWM, |

|

ADC12032CIWM, |

|

ADC12H032CIWM, |

|

ADC12034CIN, ADC12034CIWM, |

|

ADC12H034CIN, |

|

ADC12H034CIWM, |

|

ADC12038CIWM, |

|

ADC12H038CIWM |

−40ÊC ≤ TA ≤ +85ÊC |

Supply Voltage (V+ = VA+ = VD+) |

+4.5V to +5.5V |

|VA+ − V D+| |

≤ 100 mV |

VREF+ |

0V to VA+ |

VREF− |

0V to V REF+ |

VREF (VREF+ − V REF−) |

1V to V A+ |

VREF Common Mode Voltage Range |

|

|

0.1 VA+ to 0.6 VA+ |

A/DIN1, A/DIN2, MUXOUT1 |

|

and MUXOUT2 Voltage Range |

0V to VA+ |

A/D IN Common Mode |

|

Voltage Range |

|

|

0V to VA+ |

Converter Electrical Characteristics

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5 MHz for the

ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Boldface limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Notes 7, 8, 9)

Symbol |

Parameter |

Conditions |

Typical |

Limits |

Units |

|

|

|

(Note 10) |

(Note 11) |

(Limits) |

|

|

|

|

|

|

STATIC CONVERTER CHARACTERISTICS |

|

|

|

|

|

|

|

|

|

|

|

|

Resolution with No |

|

|

12 + sign |

Bits (min) |

|

Missing Codes |

|

|

|

|

|

|

|

|

|

|

+ILE |

Positive Integral Linearity Error |

After Auto-Cal (Notes 12, 18) |

±1/2 |

± 1 |

LSB (max) |

|

|

|

|

|

|

−ILE |

Negative Integral Linearity Error |

After Auto-Cal (Notes 12, 18) |

±1/2 |

± 1 |

LSB (max) |

|

|

|

|

|

|

DNL |

Differential Non-Linearity |

After Auto-Cal |

|

± 1 |

LSB (max) |

|

|

|

|

|

|

|

Positive Full-Scale Error |

After Auto-Cal (Notes 12, 18) |

±1/2 |

± 3.0 |

LSB (max) |

|

|

|

|

|

|

|

Negative Full-Scale Error |

After Auto-Cal (Notes 12, 18) |

±1/2 |

± 3.0 |

LSB (max) |

|

|

|

|

|

|

|

Offset Error |

After Auto-Cal (Notes 5, 18) |

±1/2 |

± 2 |

LSB (max) |

|

|

VIN(+) = VIN (−) = 2.048V |

|

|

|

|

DC Common Mode Error |

After Auto-Cal (Note 15) |

±2 |

± 3.5 |

LSB (max) |

|

|

|

|

|

|

TUE |

Total Unadjusted Error |

After Auto-Cal |

±1 |

|

LSB |

|

|

(Notes 12, 13, 14) |

|

|

|

|

|

|

|

|

|

|

Resolution with No |

8-bit + sign mode |

|

8 + sign |

Bits (min) |

|

Missing Codes |

|

|

|

|

|

|

|

|

|

|

+INL |

Positive Integral Linearity Error |

8-bit + sign mode (Note 12) |

|

± 1/2 |

LSB (max) |

|

|

|

|

|

|

−INL |

Negative Integral Linearity Error |

8-bit + sign mode (Note 12) |

|

± 1/2 |

LSB (max) |

|

|

|

|

|

|

DNL |

Differential Non-Linearity |

8-bit + sign mode |

|

± 3/4 |

LSB (max) |

|

|

|

|

|

|

|

Positive Full-Scale Error |

8-bit + sign mode (Note 12) |

|

± 1/2 |

LSB (max) |

|

|

|

|

|

|

|

Negative Full-Scale Error |

8-bit + sign mode (Note 12) |

|

± 1/2 |

LSB (max) |

|

|

|

|

|

|

5 |

www.national.com |

Converter Electrical Characteristics (Continued)

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5 MHz for the

ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Boldface limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Notes 7, 8, 9)

Symbol |

Parameter |

Conditions |

Typical |

Limits |

Units |

|

|

|

(Note 10) |

(Note 11) |

(Limits) |

|

|

|

|

|

|

STATIC CONVERTER CHARACTERISTICS |

|

|

|

|

|

|

|

|

|

|

|

|

Offset Error |

8-bit + sign mode, |

|

|

|

|

|

after Auto-Zero (Note 13) |

|

± 1/2 |

LSB (max) |

|

|

VIN(+) = VIN(−) = + 2.048V |

|

|

|

TUE |

Total Unadjusted Error |

8-bit + sign mode |

|

|

|

|

|

after Auto-Zero |

|

± 3/4 |

LSB (max) |

|

|

(Notes 12, 13, 14) |

|

|

|

|

|

|

|

|

|

|

Multiplexer Channel |

|

±0.05 |

|

LSB |

|

to Channel Matching |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Sensitivity |

V+ = +5V ±10% |

|

|

|

|

|

VREF = +4.096V |

|

|

|

|

Offset Error |

|

±0.5 |

± 1 |

LSB (max) |

|

+ Full-Scale Error |

|

±0.5 |

±1.5 |

LSB (max) |

|

− Full-Scale Error |

|

±0.5 |

±1.5 |

LSB (max) |

|

+ Integral Linearity Error |

|

±0.5 |

|

LSB |

|

− Integral Linearity Error |

|

±0.5 |

|

LSB |

|

|

|

|

|

|

|

Output Data from |

(Note 20) |

|

+10 |

LSB (max) |

|

ª12-Bit Conversion of Offsetº |

|

|

−10 |

LSB (min) |

|

(see Table 5) |

|

|

|

|

|

|

|

|

|

|

|

Output Data from |

(Note 20) |

|

4095 |

LSB (max) |

|

ª12-Bit Conversion of Full-Scaleº |

|

|

4093 |

LSB (min) |

|

(see Table 5) |

|

|

|

|

|

|

|

|

|

|

UNIPOLAR DYNAMIC CONVERTER CHARACTERISTICS |

|

|

|

||

|

|

|

|

|

|

S/(N+D) |

Signal-to-Noise Plus |

fIN = 1 kHz, VIN = 5 VPP, VREF+ = 5.0V |

69.4 |

|

dB |

|

Distortion Ratio |

fIN = 20 kHz, VIN = 5 VPP, VREF+ = 5.0V |

68.3 |

|

dB |

|

|

fIN = 40 kHz, VIN = 5 VPP, VREF+ = 5.0V |

65.7 |

|

dB |

|

−3 dB Full Power Bandwidth |

V IN = 5 VPP, where S/(N+D) drops 3 dB |

31 |

|

kHz |

DIFFERENTIAL DYNAMIC CONVERTER CHARACTERISTICS |

|

|

|

||

|

|

|

|

|

|

S/(N+D) |

Signal-to-Noise Plus |

fIN = 1 kHz, VIN = ±5V, VREF+ = 5.0V |

77.0 |

|

dB |

|

Distortion Ratio |

fIN = 20 kHz, VIN = ±5V, VREF+ = 5.0V |

73.9 |

|

dB |

|

|

fIN = 40 kHz, VIN = ±5V, VREF+ = 5.0V |

67.0 |

|

dB |

|

−3 dB Full Power Bandwidth |

V IN = ±5V, where S/(N+D) drops 3 dB |

40 |

|

kHz |

REFERENCE INPUT, ANALOG INPUTS AND MULTIPLEXER CHARACTERISTICS |

|

|

|

||

|

|

|

|

|

|

CREF |

Reference Input Capacitance |

|

85 |

|

pF |

CA/D |

A/DIN1 and A/DIN2 Analog |

|

75 |

|

pF |

|

Input Capacitance |

|

|

|

|

|

|

|

|

|

|

|

A/DIN1 and A/DIN2 Analog |

VIN = +5.0V or |

±0.1 |

± 1.0 |

µA (max) |

|

Input Leakage Current |

VIN = 0V |

|

|

|

|

CH0±CH7 and COM |

|

|

GND − 0.05 |

V (min) |

|

Input Voltage |

|

|

VA+ + 0.05 |

V (max) |

CCH |

CH0±CH7 and COM |

|

10 |

|

pF |

|

Input Capacitance |

|

|

|

|

|

|

|

|

|

|

CMUXOUT |

MUX Output Capacitance |

|

20 |

|

pF |

www.national.com |

6 |

Converter Electrical Characteristics (Continued)

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5 MHz for the

ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Boldface limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Notes 7, 8, 9)

Symbol |

Parameter |

Conditions |

Typical |

Limits |

Units |

|

|

|

(Note 10) |

(Note 11) |

(Limits) |

|

|

|

|

|

|

REFERENCE INPUT, ANALOG INPUTS AND MULTIPLEXER CHARACTERISTICS |

|

|

|

||

|

|

|

|

|

|

|

Off Channel Leakage (Note 16) |

On Channel = 5V and |

−0.01 |

−0.3 |

µA (min) |

|

CH0±CH7 and COM Pins |

Off Channel = 0V |

|

|

|

|

|

|

|

|

|

|

|

On Channel = 0V and |

0.01 |

0.3 |

µA (max) |

|

|

Off Channel = 5V |

|

|

|

|

|

|

|

|

|

|

On Channel Leakage (Note 16) |

On Channel = 5V and |

0.01 |

0.3 |

µA (max) |

|

CH0±CH7 and COM Pins |

Off Channel = 0V |

|

|

|

|

|

|

|

|

|

|

|

On Channel = 0V and |

−0.01 |

−0.3 |

µA (min) |

|

|

Off Channel = 5V |

|

|

|

|

|

|

|

|

|

|

MUXOUT1 and MUXOUT2 |

VMUXOUT = 5.0V or |

0.01 |

0.3 |

µA (max) |

|

Leakage Current |

VMUXOUT = 0V |

|

|

|

RON |

MUX On Resistance |

VIN = 2.5V and |

850 |

1150 |

Ω (max) |

|

|

VMUXOUT = 2.4V |

|

|

|

|

RON Matching Channel |

VIN = 2.5V and |

5 |

|

% |

|

to Channel |

VMUXOUT = 2.4V |

|

|

|

|

Channel to Channel Crosstalk |

VIN = 5 VPP, fIN = 40 kHz |

−72 |

|

dB |

|

MUX Bandwidth |

|

90 |

|

kHz |

|

|

|

|

|

|

DC and Logic Electrical Characteristics

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5 MHz for the

ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Boldface limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Notes 7, 8, 9)

Symbol |

|

|

|

|

|

Parameter |

|

|

|

Conditions |

Typical |

Limits |

Units |

|

|

|

|

|

|

|

|

|

|

|

|

|

(Note 10) |

(Note 11) |

(Limits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CCLK, |

|

|

|

|

DI, PD AND SCLK INPUT CHARACTERISTICS |

|

|

|

||||||

CS, |

CONV, |

|

|

|

||||||||||

VIN(1) |

Logical ª1º Input Voltage |

+ |

= 5.5V |

|

2.0 |

V (min) |

||||||||

|

|

V |

|

|||||||||||

VIN(0) |

Logical ª0º Input Voltage |

+ |

= 4.5V |

|

0.8 |

V (max) |

||||||||

|

|

V |

|

|||||||||||

IIN(1) |

Logical ª1º Input Current |

|

|

VIN = 5.0V |

0.005 |

1.0 |

µA (max) |

|||||||

IIN(0) |

Logical ª0º Input Current |

|

|

VIN = 0V |

−0.005 |

−1.0 |

µA (min) |

|||||||

DO, EOC AND |

|

DIGITAL OUTPUT CHARACTERISTICS |

|

|

|

|||||||||

DOR |

|

|

|

|||||||||||

VOUT(1) |

Logical ª1º Output Voltage |

+ |

= 4.5V, IOUT = −360 µA |

|

2.4 |

V (min) |

||||||||

|

|

V |

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

V+ = 4.5V, IOUT = − 10 µA |

|

4.25 |

V (min) |

|

VOUT(0) |

Logical ª0º Output Voltage |

+ |

= 4.5V, IOUT = 1.6 mA |

|

0.4 |

V (max) |

||||||||

|

|

V |

|

|||||||||||

IOUT |

TRI-STATE® Output Current |

|

|

VOUT = 0V |

−0.1 |

−3.0 |

µA (max) |

|||||||

|

|

|

|

|

|

|

|

|

|

VOUT = 5V |

0.1 |

3.0 |

µA (max) |

|

+ISC |

Output Short Circuit Source Current |

|

|

VOUT = 0V |

14 |

6.5 |

mA (min) |

|||||||

−I SC |

Output Short Circuit Sink Current |

|

|

VOUT = VD+ |

16 |

8.0 |

mA (min) |

|||||||

POWER SUPPLY CHARACTERISTICS |

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ID+ |

Digital Supply Current |

|

|

Awake |

1.6 |

2.5 |

mA (max) |

|||||||

|

|

ADC12030, ADC12032, ADC12034 |

|

|

|

= HIGH, Powered Down, CCLK on |

600 |

|

µA |

|||||

|

|

|

|

CS |

|

|||||||||

|

|

and ADC12038 |

|

|

|

= HIGH, Powered Down, CCLK off |

20 |

|

µA |

|||||

|

|

CS |

|

|||||||||||

|

|

Digital Supply Current |

|

Awake |

2.3 |

3.2 |

mA |

|||||||

|

|

ADC12H030, ADC12H032, |

|

|

= HIGH, Powered Down, CCLK on |

0.9 |

|

mA |

||||||

|

|

|

CS |

|

||||||||||

|

|

ADC12H034 and ADC12H038 |

|

|

= HIGH, Powered Down, CCLK off |

20 |

|

µA |

||||||

|

|

|

CS |

|

||||||||||

7 |

www.national.com |

DC and Logic Electrical Characteristics (Continued)

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5 MHz for the

ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Boldface limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Notes 7, 8, 9)

Symbol |

Parameter |

|

|

|

Conditions |

Typical |

Limits |

Units |

|

|

|

|

|

|

(Note 10) |

(Note 11) |

(Limits) |

|

|

|

|

|

|

|

|

|

POWER SUPPLY CHARACTERISTICS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IA+ |

Positive Analog Supply Current |

|

Awake |

2.7 |

4.0 |

mA (max) |

||

|

|

|

|

|

= HIGH, Powered Down, CCLK on |

10 |

|

µA |

|

|

|

CS |

|

||||

|

|

|

|

= HIGH, Powered Down, CCLK off |

0.1 |

|

µA |

|

|

|

CS |

|

|||||

|

|

|

|

|

|

|

|

|

IREF |

Reference Input Current |

|

Awake |

70 |

|

µA |

||

|

|

|

CS |

= HIGH, Powered Down |

0.1 |

|

µA |

|

AC Electrical Characteristics

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, tr = tf = 3 ns, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5

MHz for the ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Bold-

face limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Note 17)

Symbol |

Parameter |

Conditions |

Typical |

ADC12H030/2/4/8 |

ADC12030/2/4/8 |

Units |

|

|

|

(Note 10) |

|

|

(Limits) |

|

|

|

Limits |

Limits |

||

|

|

|

|

|

||

|

|

|

|

(Note 11) |

(Note 11) |

|

|

|

|

|

|

|

|

fCK |

Conversion Clock |

|

10 |

8 |

5 |

MHz (max) |

|

(CCLK) Frequency |

|

1 |

|

|

MHz (min) |

|

|

|

|

|

|

|

fSK |

Serial Data Clock |

|

10 |

8 |

5 |

MHz (max) |

|

SCLK Frequency |

|

0 |

|

|

Hz (min) |

|

|

|

|

|

|

|

|

Conversion Clock |

|

|

40 |

40 |

% (min) |

|

Duty Cycle |

|

|

60 |

60 |

% (max) |

|

|

|

|

|

|

|

|

Serial Data Clock |

|

|

40 |

40 |

% (min) |

|

Duty Cycle |

|

|

60 |

60 |

% (max) |

|

|

|

|

|

|

|

tC |

Conversion Time |

12-Bit + Sign or 12-Bit |

44(tCK) |

44(tCK) |

44(tCK) |

(max) |

|

|

|

|

5.5 |

8.8 |

µs (max) |

|

|

|

|

|

|

|

|

|

8-Bit + Sign or 8-Bit |

21(tCK) |

21(tCK) |

21(tCK) |

(max) |

|

|

|

|

2.625 |

4.2 |

µs (max) |

|

|

|

|

|

|

|

tA |

Acquisition Time |

6 Cycles Programmed |

6(tCK) |

6(tCK) |

6(tCK) |

(min) |

|

(Note 19) |

|

|

7(tCK) |

7(tCK) |

(max) |

|

|

|

|

0.75 |

1.2 |

µs (min) |

|

|

|

|

0.875 |

1.4 |

µs (max) |

|

|

|

|

|

|

|

|

|

10 Cycles Programmed |

10(tCK) |

10(tCK) |

10(tCK) |

(min) |

|

|

|

|

11(tCK) |

11(tCK) |

(max) |

|

|

|

|

1.25 |

2.0 |

µs (min) |

|

|

|

|

1.375 |

2.2 |

µs (max) |

|

|

|

|

|

|

|

|

|

18 Cycles Programmed |

18(tCK) |

18(tCK) |

18(tCK) |

(min) |

|

|

|

|

19(tCK) |

19(tCK) |

(max) |

|

|

|

|

2.25 |

3.6 |

µs (min) |

|

|

|

|

2.375 |

3.8 |

µs (max) |

|

|

|

|

|

|

|

|

|

34 Cycles Programmed |

34(tCK) |

34(tCK) |

34(tCK) |

(min) |

|

|

|

|

35(tCK) |

35(tCK) |

(max) |

|

|

|

|

4.25 |

6.8 |

µs (min) |

|

|

|

|

4.375 |

7.0 |

µs (max) |

|

|

|

|

|

|

|

www.national.com |

8 |

AC Electrical Characteristics (Continued)

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, tr = tf = 3 ns, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5

MHz for the ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Bold-

face limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Note 17)

Symbol |

|

|

Parameter |

Conditions |

Typical |

ADC12H030/2/4/8 |

ADC12030/2/4/8 |

Units |

|||||

|

|

|

|

|

|

|

|

|

|

(Note 10) |

|

|

(Limits) |

|

|

|

|

|

|

|

|

|

|

Limits |

Limits |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

(Note 11) |

(Note 11) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCKAL |

Self-Calibration Time |

|

4944(tCK) |

4944(tCK) |

4944(tCK) |

(max) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

618.0 |

988.8 |

µs (max) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tAZ |

Auto-Zero Time |

|

76(tCK) |

76(tCK) |

76(tCK) |

(max) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

9.5 |

15.2 |

µs (max) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSYNC |

Self-Calibration |

|

2(tCK) |

2(tCK) |

2(tCK) |

(min) |

|||||||

|

|

|

|

or Auto-Zero |

|

|

3(tCK) |

3(tCK) |

(max) |

||||

|

|

|

|

Synchronization Time |

|

|

0.250 |

0.40 |

µs (min) |

||||

|

|

|

|

from DOR |

|

|

0.375 |

0.60 |

µs (max) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

DOR High Time |

|

9(tSK) |

9(tSK) |

9(tSK) |

(max) |

||||

DOR |

|

||||||||||||

|

|

|

|

|

|

|

|

|

1.125 |

1.8 |

|

||

|

|

|

|

when |

CS |

is Low |

|

|

µs (max) |

||||

|

|

|

|

Continuously for Read |

|

|

|

|

|

||||

|

|

|

|

Data and Software |

|

|

|

|

|

||||

|

|

|

|

Power Up/Down |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

8(tSK) |

8(tSK) |

8(tSK) |

(max) |

|||||

|

|

|

|

CONV |

Valid Data Time |

|

|||||||

CONV |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

1.0 |

1.6 |

µs (max) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC Electrical Characteristics

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, tr = tf = 3 ns, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5

MHz for the ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Bold-

face limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Note 17)

Symbol |

|

|

|

|

|

|

Parameter |

Conditions |

Typical |

Limits |

Units |

||

|

|

|

|

|

|

|

|

|

|

|

(Note 10) |

(Note 11) |

(Limits) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tHPU |

|

Hardware Power-Up Time, Time from |

|

140 |

250 |

µs (max) |

|||||||

|

|

PD Falling Edge to EOC Rising Edge |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSPU |

|

Software Power-Up Time, Time from |

|

|

|

|

|||||||

|

|

Serial Data Clock Falling Edge to |

|

140 |

250 |

µs (max) |

|||||||

|

|

EOC Rising Edge |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tACC |

|

Access Time Delay from |

|

20 |

50 |

ns (max) |

|||||||

|

|

CS |

Falling Edge to DO Data Valid |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

30 |

|

|||

tSET-UP |

|

Set-Up Time of |

CS |

Falling Edge to |

|

|

ns (min) |

||||||

|

Serial Data Clock Rising Edge |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDELAY |

|

Delay from SCLK Falling |

|

0 |

5 |

ns (min) |

|||||||

|

|

Edge to |

CS |

Falling Edge |

|

|

|

|

|||||

|

|

|

RL = 3k, CL = 100 pF |

|

100 |

|

|||||||

t1H, t0H |

|

Delay from |

CS |

Rising Edge to |

40 |

ns (max) |

|||||||

|

DO TRI-STATE |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tHDI |

|

DI Hold Time from Serial Data |

|

5 |

15 |

ns (min) |

|||||||

|

|

Clock Rising Edge |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSDI |

|

DI Set-Up Time from Serial Data |

|

5 |

10 |

ns (min) |

|||||||

|

|

Clock Rising Edge |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tHDO |

|

DO Hold Time from Serial Data |

RL = 3k, CL = 100 pF |

25 |

50 |

ns (max) |

|||||||

|

Clock Falling Edge |

|

|

5 |

ns (min) |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tDDO |

|

Delay from Serial Data Clock |

|

35 |

50 |

ns (max) |

|||||||

|

|

Falling Edge to DO Data Valid |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

www.national.com |

AC Electrical Characteristics (Continued)

The following specifications apply for V+ = VA+ = VD+ = +5.0 VDC, VREF+ = +4.096 VDC, VREF− = 0 VDC, 12-bit + sign conversion mode, tr = tf = 3 ns, fCK = fSK = 8 MHz for the ADC12H030, ADC12H032, ADC12H034 and ADC12H038, fCK = fSK = 5

MHz for the ADC12030, ADC12032, ADC12034 and ADC12038, RS = 25Ω, source impedance for VREF+ and VREF− ≤ 25Ω, fully-differential input with fixed 2.048V common-mode voltage, and 10(tCK) acquisition time unless otherwise specified. Bold-

face limits apply for TA = TJ = TMIN to TMAX; all other limits TA = TJ = 25ÊC. (Note 17)

Symbol |

|

|

|

|

|

|

Parameter |

Conditions |

Typical |

Limits |

Units |

|

|

|

|

|

|

|

|

|

(Note 10) |

(Note 11) |

(Limits) |

|

|

|

|

|

|

|

|

|

|

|

|

tRDO |

DO Rise Time, TRI-STATE to High |

RL = 3k, CL = 100 pF |

10 |

30 |

ns (max) |

||||||

|

DO Rise Time, Low to High |

|

10 |

30 |

ns (max) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

tFDO |

DO Fall Time, TRI-STATE to Low |

RL = 3k, CL = 100 pF |

12 |

30 |

ns (max) |

||||||

|

DO Fall Time, High to Low |

|

12 |

30 |

ns (max) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

tCD |

|

|

|

|

|

|

|

45 |

|

||

Delay from |

CS |

Falling Edge |

|

25 |

ns (max) |

||||||

|

to |

DOR |

Falling Edge |

|

|

|

|

||||

tSD |

Delay from Serial Data Clock Falling |

|

25 |

45 |

ns (max) |

||||||

|

Edge to |

DOR |

Rising Edge |

|

|

|

|

||||

CIN |

Capacitance of Logic Inputs |

|

10 |

|

pF |

||||||

COUT |

Capacitance of Logic Outputs |

|

20 |

|

pF |

||||||

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: When the input voltage (VIN) at any pin exceeds the power supplies (VIN < GND or VIN > VA+ or VD+), the current at that pin should be limited to 30 mA. The 120 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 30 mA to four.

Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by TJmax, θJA and the ambient temperature, TA. The maximum allowable power dissipation at any temperature is PD = (TJmax − T A)/θJA or the number given in the Absolute Maximum Ratings, whichever is lower. For this device, TJmax = 150ÊC. The typical thermal resistance (θJA) of these parts when board mounted follow:

|

Thermal |

Part Number |

Resistance |

|

θJA |

ADC12H030CIWM, ADC12030CIWM |

70ÊC/W |

|

|

ADC12H032CIWM, ADC12032CIWM |

64ÊC/W |

|

|

ADC12H034CIN, ADC12034CIN |

42ÊC/W |

|

|

ADC12H034CIWM, ADC12034CIWM |

57ÊC/W |

|

|

ADC12H038CIWM, ADC12038CIWM |

50ÊC/W |

|

|

Note 5: The human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin.

Note 6: See AN450 ªSurface Mounting Methods and Their Effect on Product Reliabilityº or the section titled ªSurface Mountº found in any post 1986 National Semiconductor Linear Data Book for other methods of soldering surface mount devices.

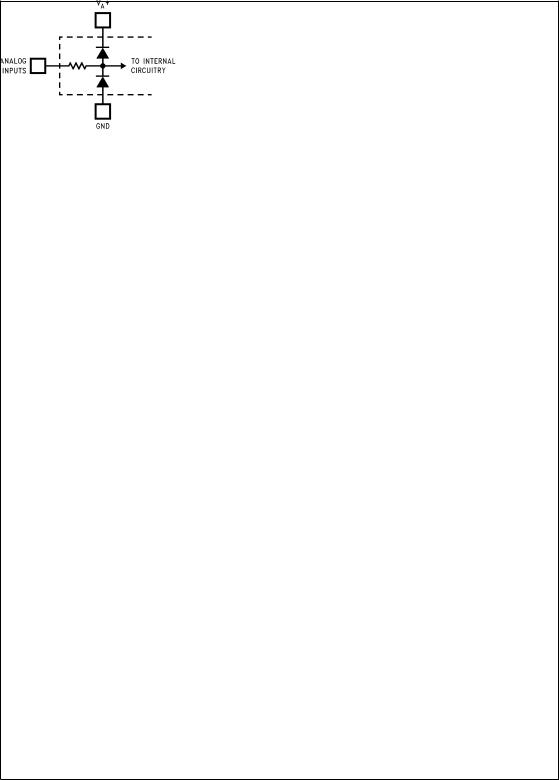

Note 7: Two on-chip diodes are tied to each analog input through a series resistor as shown below. Input voltage magnitude up to 5V above VA+ or 5V below GND will not damage this device. However, errors in the A/D conversion can occur (if these diodes are forward biased by more than 50 mV) if the input voltage magnitude of selected or unselected analog input go above VA+ or below GND by more than 50 mV. As an example, if VA+ is 4.5 VDC, full-scale input voltage must be ≤4.55 VDC to ensure accurate conversions.

DS011354-2

Note 8: To guarantee accuracy, it is required that the VA+ and VD+ be connected together to the same power supply with separate bypass capacitors at each V+ pin.

www.national.com |

10 |

AC Electrical Characteristics (Continued)

Note 9: With the test condition for VREF (VREF+ − V REF−) given as +4.096V, the 12-bit LSB is 1.0 mV and the 8-bit LSB is 16.0 mV. Note 10: Typicals are at TJ = TA = 25ÊC and represent most likely parametric norm.

Note 11: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

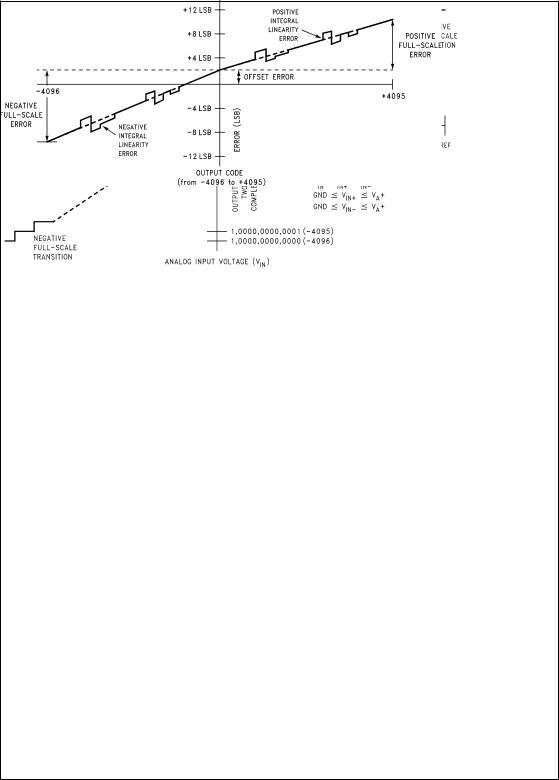

Note 12: Positive integral linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive full-scale and zero. For negative integral linearity error, the straight line passes through negative full-scale and zero (see Figures 2, 3).

Note 13: Zero error is a measure of the deviation from the mid-scale voltage (a code of zero), expressed in LSB. It is the worst-case value of the code transitions between 1 to 0 and 0 to +1 (see Figure 4).

Note 14: Total unadjusted error includes offset, full-scale, linearity and multiplexer errors.

Note 15: The DC common-mode error is measured in the differential multiplexer mode with the assigned positive and negative input channels shorted together.

Note 16: Channel leakage current is measured after the channel selection.

Note 17: Timing specifications are tested at the TTL logic levels, VIL = 0.4V for a falling edge and VIH = 2.4V for a rising edge. TRI-STATE output voltage is forced to 1.4V.

Note 18: The ADC12030 family's self-calibration technique ensures linearity and offset errors as specified, but noise inherent in the self-calibration process will result in a maximum repeatability uncertainty of 0.2 LSB.

Note 19: If SCLK and CCLK are driven from the same clock source, then tA is 6, 10, 18 or 34 clock periods minimum and maximum.

Note 20: The ª12-Bit Conversion of Offsetº and ª12-Bit Conversion of Full-Scaleº modes are intended to test the functionality of the device. Therefore, the tputou data from these modes are not an indication of the accuracy of a conversion result.

DS011354-10

FIGURE 1. Transfer Characteristic

DS011354-11

FIGURE 2. Simplified Error Curve vs Output Code without Auto-Calibration or Auto-Zero Cycles

11 |

www.national.com |

AC Electrical Characteristics (Continued)

DS011354-12

FIGURE 3. Simplified Error Curve vs Output Code after Auto-Calibration Cycle

DS011354-13

FIGURE 4. Offset or Zero Error Voltage

Typical Performance Characteristics The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. The performance for 8-bit + sign mode is equal to or better than shown. (Note 9)

Linearity Error Change |

Linearity Error Change |

Linearity Error Change |

vs Clock Frequency |

vs Temperature |

vs Reference Voltage |

DS011354-53 |

DS011354-54 |

DS011354-55 |

www.national.com |

12 |

Typical Performance Characteristics The following curves apply for 12-bit + sign mode after auto-calibration unless otherwise specified. The performance for 8-bit + sign mode is equal to or better than shown. (Note 9) (Continued)

Linearity Error Change |

Full-Scale Error Change |

Full-Scale Error Change |

vs Supply Voltage |

vs Clock Frequency |

vs Temperature |

DS011354-56 DS011354-57 DS011354-58

Full-Scale Error Change |

Full-Scale Error Change |

Zero Error Change |

vs Reference Voltage |

vs Supply Voltage |

vs Clock Frequency |

DS011354-59 DS011354-60 DS011354-61

Zero Error Change |

Zero Error Change |

Zero Error Change |

vs Temperature |

vs Reference Voltage |

vs Supply Voltage |

DS011354-62 |

DS011354-63 |

DS011354-64 |

13 |

www.national.com |

Loading...

Loading...