NSC 5962-9219001MSA, 5962-9219001MRA, 5962-9219001M2A Datasheet

September 1998

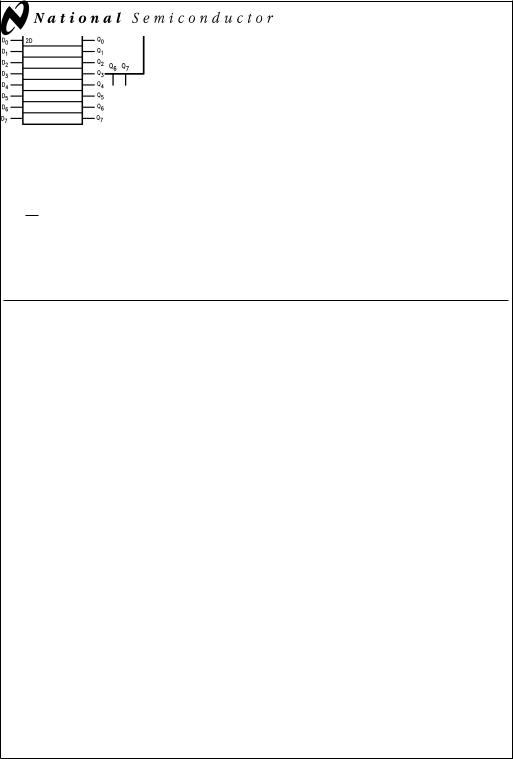

54ACTQ377

Octal D Flip-Flop with Clock Enable

General Description

The ACTQ377 has eight edge-triggered, D-type flip-flops with individual D inputs and Q outputs. The common buffered Clock (CP) input loads all flip-flops simultaneously, when the Clock Enable (CE) is LOW.

The register is fully edge-triggered. The state of each D input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop's Q output. The CE input must be stable only one setup time prior to the LOW-to-HIGH clock transition for predictable operation.

The ACTQ377 utilizes FACT Quiet Series® technology to guarantee quiet output switching and improved dynamic threshold performance. FACT Quiet Series features GTO® output control and undershoot corrector in addition to a split ground bus for superior performance.

Features

nIdeal for addressable register applications

nClock enable for address and data synchronization applications

nEight edge-triggered D flip-flops

nBuffered common clock

nOutputs source/sink 24 mA

nSee '273 for master reset version

nSee '373 for transparent latch version

nSee '374 for TRI-STATE® version

nGuaranteed simultaneous switching noise level and dynamic threshold performance

nTTL-compatible inputs and outputs

nStandard Microcircuit Drawing (SMD) 5962-9219001

Logic Symbols

IEEE/IEC

DS100357-1

DS100357-2

|

Pin |

Description |

|

|

Names |

|

|

|

|

|

|

|

D0±D7 |

Data Inputs |

|

|

|

Clock Enable (Active LOW) |

|

|

CE |

|

|

|

Q0±Q7 |

Data Outputs |

|

|

CP |

Clock Pulse Input |

|

|

|

|

|

GTO® is a trademark of National Semiconductor Corporation.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

FACT® and FACT Quiet Series® are registered trademarks of Fairchild Semiconductor Corporation.

Enable Clock with Flop-Flip D Octal 54ACTQ377

© 1998 National Semiconductor Corporation |

DS100357 |

www.national.com |

Connection Diagrams

Pin Assignment |

Pin Assignment |

for DIP and Flatpak |

for LCC |

DS100357-4

DS100357-3

Mode Select-Function Table

Operating Mode |

|

Inputs |

|

Outputs |

||

|

|

|

|

|

|

|

|

CP |

|

|

|

Dn |

Qn |

|

|

CE |

||||

Load `1' |

N |

|

L |

H |

H |

|

|

|

|

|

|

|

|

Load `0' |

N |

|

L |

L |

L |

|

|

|

|

|

|

|

|

Hold (Do Nothing) |

N |

|

H |

X |

No Change |

|

|

X |

|

H |

X |

No Change |

|

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

N = LOW-to-HIGH Clock Transition

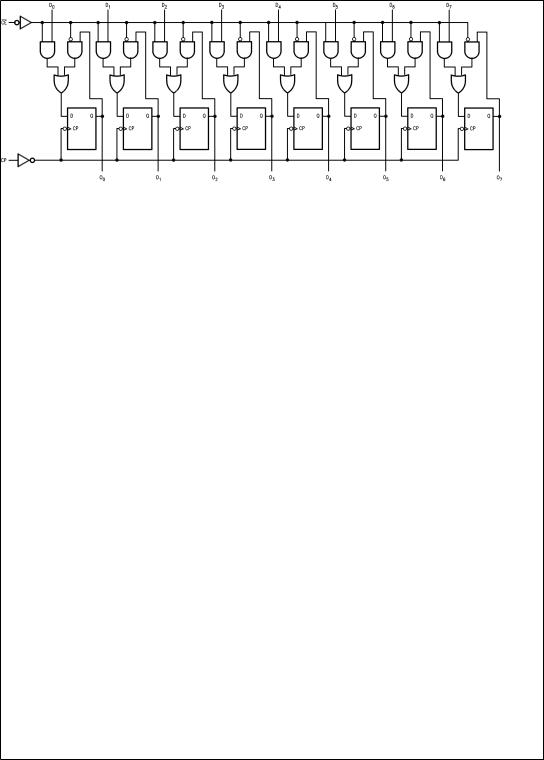

Logic Diagram

DS100357-5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.national.com |

2 |

Loading...

Loading...