NSC 5962R8755401SFA, 5962R8755401SEA, 5962R8755401S2A, 5962R8755401BFA, 5962R8755401BEA Datasheet

...

August 1998

54AC138 · 54ACT138

1-of-8 Decoder/Demultiplexer

General Description

The 'AC/'ACT138 is a high-speed 1-of-8 decoder/ demultiplexer. This device is ideally suited for high-speed bipolar memory chip select address decoding. The multiple input enables allow parallel expansion to a 1-of-24 decoder using just three 'AC/'ACT138 devices or a 1-of-32 decoder using four 'AC/'ACT138 devices and one inverter.

Features

nICC reduced by 50%

nDemultiplexing capability

nMultiple input enable for easy expansion

nActive LOW mutually exclusive outputs

nOutputs source/sink 24 mA

n'ACT138 has TTL-compatible inputs

nStandard Microcircuit Drawing (SMD)

Ð'AC138: 5962-87622

Ð'ACT138: 5962-87554

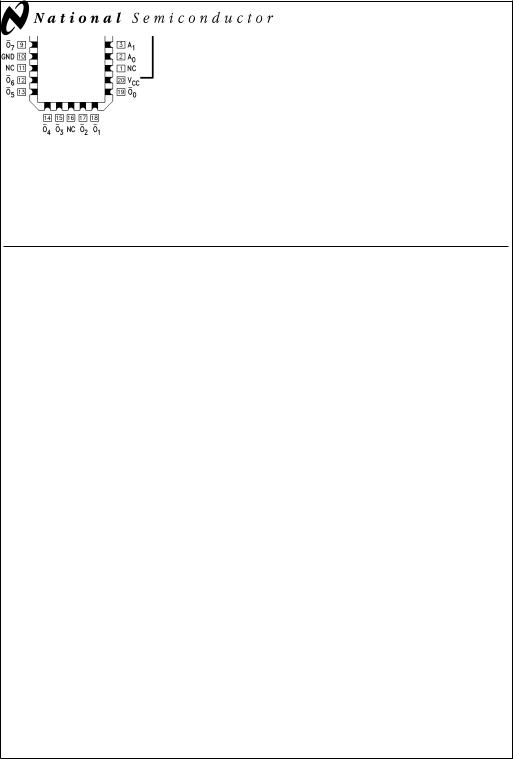

Logic Symbols |

Connection Diagrams |

Pin Assignment for DIP and Flatpak

DS100268-1

IEEE/IEC

DS100268-2

Pin Assignment

for LCC

|

|

|

|

|

|

|

|

DS100268-7 |

|

|

|

|

|

|

|

|

|

|

Pin Names |

Description |

|

|||||

|

|

|

|

|

|

|

|

|

|

A0±A2 |

Address Inputs |

|

|||||

|

|

|

|

|

|

|

|

|

|

E |

1±E |

2 |

Enable Inputs |

|

|||

|

E3 |

Enable Input |

|

|||||

|

|

|

|

7 |

Outputs |

|

||

|

O |

0±O |

DS100268-3 |

|||||

FACT® is a registered trademark of Fairchild Semiconductor Corporation.

Decoder/Demultiplexer 8-of-1 54ACT138 · 54AC138

© 1998 National Semiconductor Corporation |

DS100268 |

www.national.com |

Functional Description

The 'AC/'ACT138 high-speed 1-of-8 decoder/demultiplexer accepts three binary weighted inputs (A0, A1, A2) and, when enabled, provides eight mutually exclusive active-LOW outputs (O0±O7). The 'AC/'ACT138 features three Enable in-

puts, two active-LOW (E1, E2) and one active-HIGH (E3). All outputs will be HIGH unless E1 and E2 are LOW and E3 is HIGH. This multiple enable function allows easy parallel ex-

pansion of the device to a 1-of-32 (5 lines to 32 lines) decoder with just four 'AC/'ACT138 devices and one inverter (see Figure 1). The 'AC/'ACT138 can be used as an 8-output demultiplexer by using one of the active LOW Enable inputs as the data input and the other Enable inputs as strobes. The Enable inputs which are not used must be permanently tied to their appropriate active-HIGH or active-LOW state.

Truth Table

|

|

|

|

|

|

Inputs |

|

|

|

|

|

|

|

|

|

|

|

|

Outputs |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

1 |

|

E |

2 |

E3 |

A0 |

A1 |

A2 |

|

O |

0 |

|

O |

1 |

|

O |

2 |

|

O |

3 |

|

O |

4 |

|

O |

5 |

|

O |

6 |

|

O |

7 |

|

H |

|

X |

X |

X |

X |

X |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

||||||||||

|

X |

|

H |

X |

X |

X |

X |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

||||||||||

|

X |

|

X |

L |

X |

X |

X |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

||||||||||

|

L |

|

L |

H |

L |

L |

L |

|

L |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

||||||||||

|

L |

|

L |

H |

H |

L |

L |

|

H |

|

L |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

||||||||||

|

L |

|

L |

H |

L |

H |

L |

|

H |

|

H |

|

L |

|

H |

|

H |

|

H |

|

H |

|

H |

||||||||||

|

L |

|

L |

H |

H |

H |

L |

|

H |

|

H |

|

H |

|

L |

|

H |

|

H |

|

H |

|

H |

||||||||||

|

L |

|

L |

H |

L |

L |

H |

|

H |

|

H |

|

H |

|

H |

|

L |

|

H |

|

H |

|

H |

||||||||||

|

L |

|

L |

H |

H |

L |

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

L |

|

H |

|

H |

||||||||||

|

L |

|

L |

H |

L |

H |

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

L |

|

H |

||||||||||

|

L |

|

L |

H |

H |

H |

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

H |

|

L |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

www.national.com |

2 |

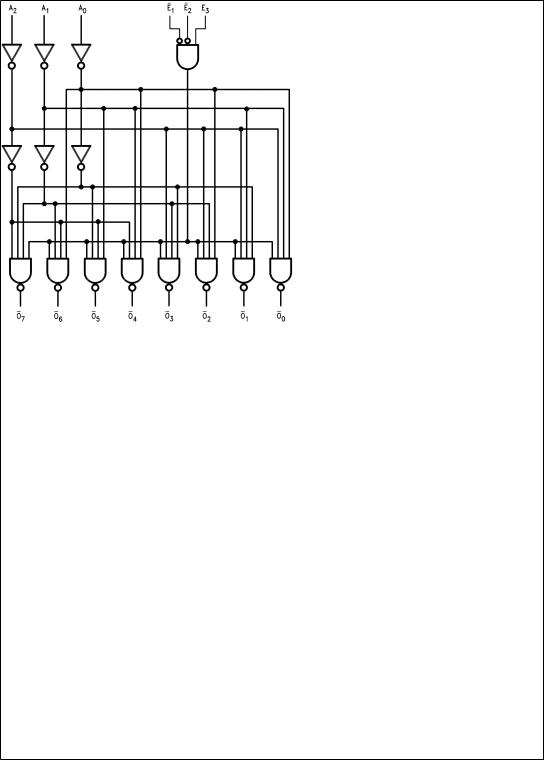

Logic Diagram

DS100268-4

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

3 |

www.national.com |

Loading...

Loading...